PROCESADOR DE COMA FLOTANTE CON UNA SUBPRECISION SELECCIONABLE.

Un procedimiento para llevar a cabo una operación en coma flotante,

que comprende:

seleccionar un formato para una operación en coma flotante, y seleccionar una subprecisión para la operación en coma flotante;

determinar un subconjunto de una pluralidad de bits almacenados en un registro de coma flotante, conforme a la subprecisión seleccionada al excluir uno o más bits sobrantes del subconjunto y en el que el registro de coma flotante comprende una sección de exponente configurada para almacenar bits de exponente y una sección de fracción configurada para almacenar bits de fracción, y en el que los bits sobrantes comprenden bits de fracción; y

llevar a cabo la operación en coma flotante utilizando únicamente el subconjunto de la pluralidad de bits caracterizado por:

leer del registro únicamente los bits incluidos en el subconjunto, y no leer ninguno de los bits sobrantes, para generar un número de entrada caracterizado por la subprecisión seleccionada; y

llevar a cabo la operación en coma flotante en el número de entrada, para generar un número de salida que tiene una pluralidad de bits de salida

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2006/039063.

Solicitante: QUALCOMM MEMS TECHNOLOGIES, INC.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE,SAN DIEGO, CA 92121.

Inventor/es: DOCKSER,KENNETH,ALAN.

Fecha de Publicación: .

Fecha Concesión Europea: 24 de Febrero de 2010.

Clasificación Internacional de Patentes:

- G06F7/57F

Clasificación PCT:

- G06F7/483 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Cálculos realizados con números representados por una combinación no lineal de números denominados, p. ej. números racionales, sistema de numeración logarítmica o números de coma flotante.

- G06F7/57 G06F 7/00 […] › Unidades aritmético lógicas (ALU), p. ej. disposiciones o dispositivos para la realización de dos o más de las operaciones cubiertas por los grupos G06F 7/483 - G06F 7/556 o para la realización de operaciones lógicas.

Fragmento de la descripción:

Procesador de coma flotante con una subprecisión seleccionable.

Antecedentes

Los procesadores de coma flotante son unidades especializadas de cómputo que llevan a cabo ciertas operaciones matemáticas, por ejemplo, multiplicación, división, funciones trigonométricas, y funciones exponenciales, a alta velocidad. En consecuencia, los sistemas potentes de cómputo incorporan a menudo procesadores de coma flotante, bien como parte del procesador principal o bien como un coprocesador. Normalmente, una representación de coma flotante de un número incluye un componente de signo, un exponente y una mantisa. Para hallar el valor, se multiplica la mantisa por una base (normalmente 2 en ordenadores) elevada a la potencia del exponente. Se aplica el signo al valor resultante.

La precisión del procesador de coma flotante está definida por el número de bits utilizados para representar la mantisa. Cuantos más bits en la mantisa, mayor es la precisión. En general, la precisión del procesador de coma flotante depende de la aplicación particular. Por ejemplo, el estándar ANSI/IEEE-754 (seguido por la mayoría de todos los ordenadores con módem) especifica un formato simple de 32 bits que tienen un signo de 1 bit, un exponente de 8 bits y una mantisa de 24 bits. Solo están almacenados los 23 bits de fracción en la codificación de 32 bits, se implica un bit de número entero, inmediatamente a la izquierda del punto binario. El IEEE-754 también especifica un formato doble de 64 bits que tiene un signo de 1 bit, un exponente de 11 bits y una mantisa de 53 bits. De forma análoga a la codificación simple, solo se almacenan los 52 bits de fracción de la mantisa en la codificación de 64 bits, se implica un bit de número entero, inmediatamente a la izquierda del punto binario. Una mayor precisión tiene como resultado una mayor exactitud, pero tiene una intensidad de cómputo mayor, lo que tiene como resultado un mayor consumo de energía.

El rendimiento de las operaciones aritméticas en coma flotante puede conllevar una ineficacia de cómputo porque los procesadores de coma flotante están limitados, normalmente, a la precisión proporcionada bien por el formato simple, o bien tanto por los formatos simple y doble. Aunque algunas aplicaciones pueden requerir estos tipos de precisión, otras aplicaciones pueden no requerirlos. Por ejemplo, algunas aplicaciones gráficas pueden requerir únicamente una mantisa de 16 bits. Para estas aplicaciones gráficas, cualquier exactitud más allá de los 16 bits de precisión tiende a tener como resultado un consumo innecesario de energía. Esto es de inquietud particular en los dispositivos alimentados por batería en los que la energía es escasa, tal como teléfonos inalámbricos, agendas electrónicas (PDA), ordenadores portátiles, consolas de videojuegos, buscapersonas, y cámaras, por mencionar algunos. Si se conoce que una aplicación siempre requiere una cierta precisión reducida, el procesador de coma flotante puede estar diseñado y construido para esa precisión reducida. Sin embargo, para la mayoría de los procesadores de uso general la situación típica es que para ciertas aplicaciones es aceptable una precisión reducida, por ejemplo, para la generación de gráficos 3D, y para otras aplicaciones se necesita una mayor precisión para implementar las funciones, por ejemplo, del Sistema de posicionamiento global (GPS). En consecuencia, existe la necesidad en la técnica para un procesador de coma flotante en el que se puede seleccionarla precisión reducida, o la subprecisión, del formato de coma flotante.

En la publicación de la solicitud de patente US 2005/0066205 se da a conocer un sistema gráfico 3D conforme al preámbulo de las reivindicaciones independientes.

Resumen

En una realización de un procesador de coma flotante, el procesador de coma flotante incluye un registro de coma flotante configurado para almacenar una pluralidad de bits en uno o más formatos de coma flotante, un controlador, y al menos un operador de coma flotante. El controlador está configurado para seleccionar una subprecisión de la precisión especificada para una operación en coma flotante. El controlador está configurado adicionalmente para determinar un subconjunto de la pluralidad de bits, conforme a la subprecisión seleccionada. El operador de coma flotante está configurado para llevar a cabo la operación en coma flotante utilizando únicamente el subconjunto de la pluralidad de bits.

En una realización de un procedimiento para llevar a cabo una operación en coma flotante, el procedimiento incluye seleccionar una subprecisión para la operación en coma flotante. El procedimiento incluye determinar un subconjunto de una pluralidad de bits almacenados en un registro de coma flotante, conforme a la subprecisión seleccionada. El procedimiento incluye llevar a cabo la operación en coma flotante utilizando únicamente el subconjunto de la pluralidad de bits.

Se debe comprender que serán muy evidentes para los expertos en la técnica otras realizaciones del procesador de coma flotante, y del procedimiento de llevar a cabo operaciones en coma flotante a partir de la siguiente descripción detallada, en la que se muestran y se describen diversas realizaciones del procesador de coma flotante y del procedimiento de llevar a cabo operaciones en coma flotante a modo de ilustración. Como se comprenderá, son posibles otras realizaciones distintas del procesador de coma flotante y del procedimiento de llevar a cabo operaciones en coma flotante, y los detalles utilizados para describir estas realizaciones pueden ser modificados en muchos sentidos. En consecuencia, se debe considerar que los dibujos y la descripción detallada son de naturaleza ilustrativa, y no restrictiva.

Breve descripción de los dibujos

La Fig. 1 es un diagrama funcional de bloques que ilustra un ejemplo de un procesador de coma flotante con una subprecisión seleccionable;

la Fig. 2 ilustra de forma esquemática un ejemplo de un archivo de registro de coma flotante utilizado en un procesador de coma flotante con una subprecisión seleccionable;

la Fig. 3A es un diagrama conceptual que ilustra un ejemplo de una suma en coma flotante que se lleva a cabo utilizando procesador de coma flotante con una subprecisión seleccionable;

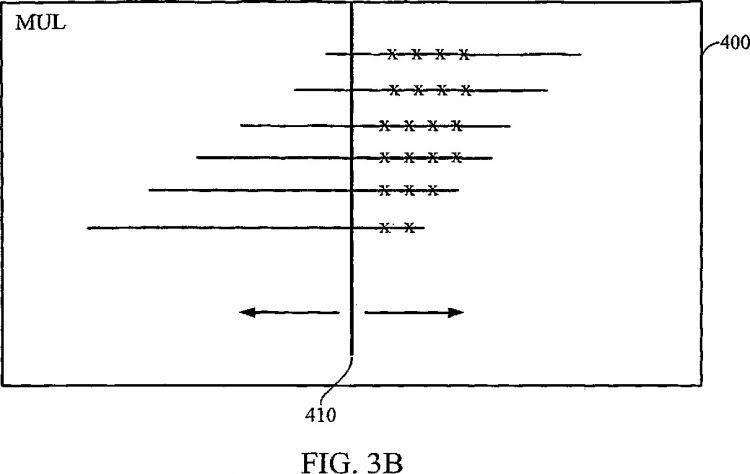

la Fig. 3B es un diagrama conceptual que ilustra un ejemplo de una multiplicación en coma flotante que se lleva a cabo utilizando un procesador de coma flotante con una subprecisión seleccionable.

Descripción detallada

Se pretende que la descripción detallada expuesta a continuación en conexión con los dibujos adjuntos describa diversas realizaciones de la presente invención, pero no se pretende que represente las únicas realizaciones en las que se pueda poner en práctica la presente invención. La descripción detallada incluye detalles específicos, para permitir una comprensión profunda de la presente invención. Sin embargo, los expertos en la técnica deberían apreciar se puede poner en práctica la presente invención sin estos detalles específicos. En algunos casos, las estructuras y los componentes bien conocidos se conocen en forma de diagrama de bloques, para ilustrar con mayor claridad los conceptos de la presente invención.

En al menos una realización de un procesador de coma flotante, se puede reducir la precisión para una o más operaciones en coma flotante con respecto a la del formato especificado. Las instrucciones proporcionadas al procesador de coma flotante para llevar a cabo operaciones matemáticas pueden incluir un campo programable de control. Se puede utilizar el campo de control para seleccionar la subprecisión del formato de coma flotante. Al seleccionar la subprecisión del formato de coma flotante únicamente a la cantidad precisa necesaria para una operación particular, se puede conseguir una mayor eficacia al igual que ahorros significativos de energía.

La Fig. 1 es un diagrama funcional de bloques que ilustra un ejemplo de un procesador 100 de coma flotante (FPP) con una subprecisión seleccionable. El procesador 100 de coma flotante incluye un archivo 110 de registro de coma flotante (FPR); un controlador 130 de coma flotante (CTL); y un operador matemático 140 de coma flotante (FPO). Se puede implementar el procesador 100 de coma flotante como parte del procesador principal, como un coprocesador o como una entidad aparte conectada al procesador principal por medio de un bus u otro canal.

El archivo 110 de registro de coma flotante puede ser cualquier medio adecuado de almacenamiento. En la realización mostrada en la Fig. 1, el archivo 110...

Reivindicaciones:

1. Un procedimiento para llevar a cabo una operación en coma flotante, que comprende:

2. El procedimiento de la reivindicación 1, que comprende, además, forzar a los bits sobrantes a un estado de descarga espontánea baja.

3. El procedimiento de la reivindicación 1, que comprende, además, truncar del número de salida cualquiera de los bits de salida que sobran de la subprecisión seleccionada, generando de ese modo un número truncado de salida caracterizado por la subprecisión seleccionada.

4. El procedimiento de la reivindicación 1 o 3, que comprende, además, redondear el número de salida a la subprecisión seleccionada.

5. El procedimiento de la reivindicación 1, en el que leer los bits en el subconjunto comprende precargar todas las líneas de bits en el subconjunto, y dejar todos los bits sobrantes en un estado descargado.

6. El procedimiento de cualquier reivindicación precedente, en el que el registro comprende una pluralidad de elementos de registro, correspondiendo cada elemento de registro a uno respectivo de la pluralidad de bits; y en el que llevar a cabo la operación en coma flotante comprende poner a cero cualquiera de los elementos de registro que se corresponden con uno de los bits sobrantes.

7. El procedimiento de cualquier reivindicación precedente, en el que el formato de coma flotante comprende al menos uno entre: un formato simple que incluye un bit de signo, ocho bits de exponente, y veintitrés bits de fracción; un formato doble que incluye un bit de signo, once bits de exponente y cincuenta y dos bits de fracción; y un formato extendido que incluye un bit de signo, quince bits de exponente, y sesenta y cuatro bits de mantisa.

8. El procedimiento de cualquier reivindicación precedente, en el que la operación en coma flotante comprende al menos uno entre: una suma en coma flotante; una resta en coma flotante; una multiplicación en coma flotante; una división en coma flotante; una extracción de raíz cuadrada en coma flotante; un cómputo de función trigonométrica en coma flotante; un cómputo de función exponencial en coma flotante; un cómputo de función logarítmica en coma flotante.

9. Un procedimiento de llevar a cabo una operación en coma flotante que comprende:

10. Un procesador de coma flotante, que comprende:

11. El procesador de coma flotante de la reivindicación 10, en el que el controlador está configurado adicionalmente para seleccionar la subprecisión en respuesta a la entrada del usuario.

12. El procesador de coma flotante de la reivindicación 10, en el que el registro de coma flotante comprende una sección de exponente configurada para almacenar bits de exponente y una sección de fracción configurada para almacenar bits de fracción; y en el que los bits sobrantes comprenden bits de fracción.

13. El procesador de coma flotante de la reivindicación 10, en el que el controlador está configurado adicionalmente para forzar a los bits sobrantes a un estado de descarga espontánea baja.

14. El procesador de coma flotante de la reivindicación 10, en el que el operador de coma flotante comprende al menos uno entre:

15. El procesador de coma flotante de cualquiera de las reivindicaciones 10 a 14, en el que el operador de coma flotante está configurado adicionalmente para truncar del número de salida cualquiera de los bits de salida que sobran de la subprecisión seleccionada, generando de ese modo un número truncado de salida caracterizado por la subprecisión seleccionada.

16. El procesador de coma flotante de cualquiera de las reivindicaciones 10 a 15, en el que el operador de coma flotante está configurado adicionalmente para redondear el número de salida a la subprecisión seleccionada.

17. El procesador de coma flotante de la reivindicación 10, en el que el operador de coma flotante está configurado adicionalmente para precargar todos los bits en el subconjunto, y para dejar todos los bits sobrantes en un estado descargado.

18. El procesador de coma flotante de cualquiera de las reivindicaciones 10 a 17, en el que el registro comprende una pluralidad de elementos de registro, correspondiéndose cada elemento de registro a uno respectivo de la pluralidad de bits; y en el que el controlador está configurado adicionalmente para poner a cero cualquiera de los elementos de registro correspondientes a uno de los bits sobrantes.

19. Un procesador de coma flotante, que comprende:

Patentes similares o relacionadas:

Cálculo rápido de productos por fracciones diádicas con errores de redondeo de signo simétrico, del 11 de Marzo de 2020, de QUALCOMM INCORPORATED: Un procedimiento para mantener una exactitud de aproximaciones para una señal fuente proporcionada en un formato digital para su uso en algoritmos de procesamiento […]