METODO Y DISPOSITIVO PARA CODIFICACION DE CANAL ADAPTATIVO.

Un codificador turbo para codificar bits de información de entrada,

que comprende:

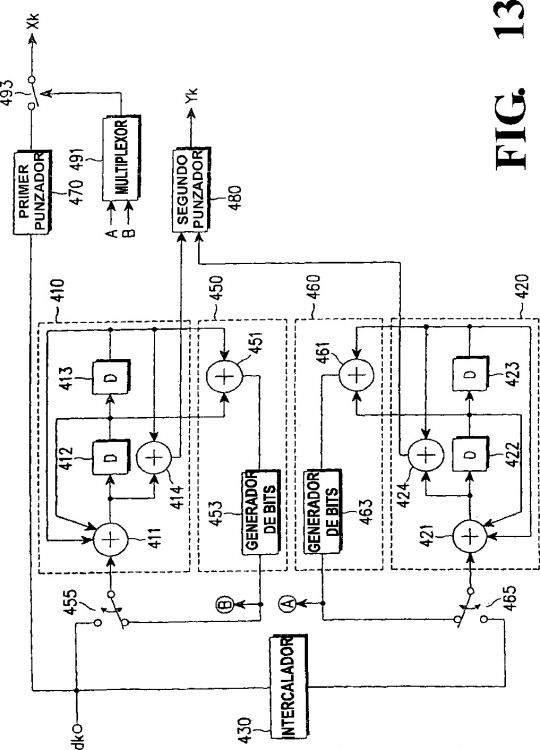

un primer codificador de componente (410) para codificar bits de información de entrada en una trama para generar primeros bits de paridad;

un intercalador (430) para intercalar los bits de información de entrada, y un segundo codificador de componente (420) para codificar los bits de información de entrada intercalada para generar segundos bits de paridad,

caracterizados porque

un primer generador de bits de cola (450) separado del primer codificador de componente (410) para generar primeros bits de cola es igual a valores retroalimentados del primer codificador de componente (410) para terminar el primer codificador de componente, dicho primer generador de bits de cola comprende unos medios X-OR;

un segundo generador de bits de cola (460) separado del segundo codificador de componente (420) para generar segundos bits de cola que son iguales a los valores retroalimentados de los segundos codificador de componente (420) para terminar el segundo codificador de componentes, dicho segundo generador de bits de cola comprende unos medios X-OR;

un primer interruptor (455) para conmutar los valores retroalimentados del primer codificador de componente (410) al primer codificador de componentes como los primeros bits de cola en el extremo de la trama, y

un segundo interruptor (465) para conmutar los valores de retroalimentados del segundo codificador de componente (420) al segundo codificador de componentes como el segundo bits de cola en el extremo de la trama,

en donde cada uno de los codificadores de componentes (410, 420) requiere bits de cola tanto como memorias del codificador de componente que están dispuestas para codificar bits de información de entrada de tamaños de trama variables, en donde los codificadores de componente (410, 420) generan un bit de información y dos bits de paridad en respuesta a proporcionar cada uno de los bits de información al codificador de componente y generar dos bits de de cola y dos los bits de paridad en respuesta a proporcionar cada uno de los primeros y segundos bits de cola al codificador de componente (410, 420)

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E05016017.

Solicitante: SAMSUNG ELECTRONICS CO., LTD..

Nacionalidad solicitante: República de Corea.

Dirección: 416, MAETAN-DONG PALDA-GU,SUWON-SHI KYONGGI DO 442-270.

Inventor/es: KIM, YONG, PARK, CHANG SOO, KONG, JUN JIN, LEE,HYEON,WOO, LEE,PIL,JOONG.

Fecha de Publicación: .

Fecha Solicitud PCT: 30 de Julio de 1998.

Fecha Concesión Europea: 21 de Abril de 2010.

Clasificación Internacional de Patentes:

- H03M13/00H

- H03M13/27 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › usando técnicas de entrelazado.

- H03M13/29T

- H03M13/29T1S

- H04L1/00B3

- H04L1/00B5

- H04L1/00B7C

- H04L1/00B7K1

- H04L1/00B7K3

- H04L1/00B7R1

- H04L1/00B7V

Clasificación PCT:

- H03M13/29 H03M 13/00 […] › combinando dos o más códigos o estructuras de códigos, p. ej. códigos de productos, códigos de producto generalizados, códigos concatenados, códigos internos y externos.

Clasificación antigua:

- H03M13/29 H03M 13/00 […] › combinando dos o más códigos o estructuras de códigos, p. ej. códigos de productos, códigos de producto generalizados, códigos concatenados, códigos internos y externos.

Países PCT: Alemania, España, Francia, Reino Unido, Italia, Suecia, Irlanda, Eslovenia, Finlandia, Rumania, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Método y dispositivo para codificación de canal adaptativo.

Antecedente de la invención

La presente invención se relaciona con métodos y dispositivos para codificación de canal adaptativo para sistemas de comunicaciones, y en particular, con métodos y dispositivos para codificación de canales adaptativos para uso en transmisión de voz y datos.

Un codificador turbo, constituido en una estructura en paralelo o en serie, genera símbolos de paridad a partir de una trama de bit de información N de entrada con dos codificadores de componente simple (o constituyentes). Este utiliza un código convolucional sistemático recursivo (RSC) como un código de componente (o constituyentes).

La Fig. 1 es un diagrama de bloques de un codificador turbo paralelo convencional, descrito en la Patente Estadounidense No. 5,446,747 otorgada a Berrou. En el codificador turbo de La Fig. 1, se interpone un intercalador 12 entre los primeros y segundos codificadores de componente 11 y 13. El intercalador 12 tiene un tamaño equivalente a la longitud de la trama N de los bits de información de entrada, y modifica la secuencia de los bits de información recibidos en el segundo codificador componente 13 para reducir la correlación entre los bits de información. La Fig. 2 es un diagrama de bloques de un codificador turbo en serie convencional que también tiene el intercalador 12 conectado entre los primeros y segundos codificadores de componente 11 y 13.

Los codificadores turbo anteriores producen un código turbo para uso en comunicaciones espaciales. Aunque una restricción de la longitud K en los codificadores de componente 11 y 13 es más corta que aquella de un código convolucional convencional (es decir, K=9), el intercalador 12 utiliza una memoria muy grande, lo que resulta en un retraso muy largo en la decodificación.

La Fig. 3 es un diagrama de bloques de un decodificador turbo para decodificar la salida del codificador turbo paralelo mostrado en la Fig. 1, también descrito en la Patente Estadounidense No. 5,446,747 otorgada a Berrou. La Fig. 4 es un diagrama de bloques de un decodificador turbo para decodificar la salida del codificador turbo en serie mostrado en la Fig. 2, propuesto por Benedetto en un artículo de IEEE Electronics Letters, Vol. 32, No. 13, Junio 1996.

El decodificador turbo en paralelo de La Fig. 3 mejora ventajosamente las características de desempeño en términos de error de bit (BER) al decodificar respectivamente datos de entrada en unidades de trama, utilizando un algoritmo de decodificación iterativo. Un intercalador 323 contribuye a un incremento en una capacidad de corrección de error al distribuir los patrones de error en ráfaga que no se corrigen, mediante un primer decodificador 319, antes de la corrección de los patrones de error en ráfaga en un segundo decodificador 327.

La decodificación iterativa se refiere a la decodificación repetida de símbolos que se decodifican en un procedimiento especifico, utilizando la información extrínseca resultante, para lograr excelente desempeño de decodificación. Los algoritmos de decodificación iterativa son SOVA (Soft-Output Viterbi Algorithm: ver Proceedings of IEEE Vehicular Technology Conference, pp. 941-944, Mayo 1993) y MAP (Maximum Aposteriori Probability: ver IEEE Transactions on Information Theory, pp. 429-445, Vol. 42, No. 2, Marzo 1996). SOVA es una modificación de un algoritmo Viterbi que produce una salida de decisión suave y puede minimizar el índice de error de palabra de código. De otra parte, MAP puede minimizar el índice de error de símbolo.

En el decodificador de La Fig. 3, la salidas y1k e y2k de un "despunzador" 313 son yk y cero, respectivamente, cuando se recibe símbolo de paridad yk del primer codificador de componente 11 de La Fig. 1, mientras que ellos sean cero y yk, respectivamente, cuando se recibe el símbolo de paridad yk del segundo codificador de componente 13 de La Fig. 1. Zk+1 es un símbolo de decisión suave utilizada como información extrínseca en un algoritmo de decodificación iterativo y una entrada para decodificación en una siguiente etapa. Se obtiene un símbolo propuesto final al someter Zk+1 a una decisión dura. El desempeño del código turbo depende del tamaño del intercalador, la estructura del intercalador, y el número de decodificaciones iterativa.

Como se muestra en la Fig. 1, el codificador turbo incluye el intercalador 12. El intercalador 12 produce la codificación/decodificación turbo para ser implementada en unidades de trama. Así, la complejidad del código turbo es proporcional al producto del tamaño de trama de una memoria necesaria para primeros y segundos decodificadores iterativos 319 y 327 mostrados en la Fig. 3 y el número de estado de los códigos componentes para los primeros y segundos codificadores de componente 11 y 13. El código turbo no puede encontrar su aplicación en trasmisión de voz y datos debido al uso de tramas muy grandes. Incrementar el número de estado de los códigos de componentes para el codificador turbo con el fin de alcanzar mejor desempeño conduce a una complejidad incrementada de los primeros y segundos codificadores de componente 11 y 13.

Con un error en ráfaga en los decodificadores como se muestra en la Fig. 3, la salida del primer decodificador iterativo 319 tiene una correlación, que impide la decodificación confiable en el segundo decodificador iterativo 327 en la siguiente etapa de decodificación, por lo tanto, se incurren en errores en un bloque completo y no se pueden corregir en una siguiente etapa de decodificación iterativa. En este contexto, hay una necesidad cada vez mayor de un intercalador y un desintercalador que pueda distribuir errores en ráfagas en una única trama de un sujeto de código para decodificación iterativa sin correlación.

Debido a la ventaja de la baja correlación, un intercalador aleatorio incrementa el desempeño del código turbo. Con un tamaño pequeño de trama, sin embargo, el intercalador aleatorio tiene limitaciones en su efectividad para distribuir errores en ráfagas sin la correlación y requiere una Tabla de Valores. Por lo tanto, la transmisión de voz o la transmisión de datos de bajo índice requieren un tamaño de trama pequeño un número pequeño de estados de código de componente para minimizar el tiempo de retraso. La transmisión de voz o la transmisión de datos de bajo índice necesitan adicionalmente un intercalador estructurado. En resumen, el código turbo convencional no es viable en la transmisión de voz y datos debido a la inaceptable longitud de restricción de los códigos componentes y el intercalador grande. No obstante, se han hecho grandes esfuerzos en la realización de un codificador y un decodificador para un sistema de comunicaciones, que tiene en cuenta la ventaja del código turbo convencional.

Por lo tanto, existe la necesidad de un codificador turbo que tenga un desempeño igual a o menor que aquel de un codificador convolucional en un sistema de comunicaciones convencional. Existe una necesidad adicional de un intercalador que tenga excelente desempeño con estados de código de componentes y tiempo de retraso minimizado. Aunque el desempeño del intercalador 12 de La Fig. 1 o 2 para uso en un codificador turbo es generalmente proporcional al tamaño del intercalador, el tamaño de la trama del código turbo es limitado. En este caso, es preferible utilizar un intercalador que maximice una distancia Hamming mínima de los códigos turbo en términos de un código de bloque. Se puede emplear un intercalador estructurado para tramas pequeñas.

Divsalar, D., et al. "Codigo turbo for Deep-Space Communications", TDA Progress Report, Volumen 42-120, Febrero 15, 1995, páginas 29-39, en particular se refiere a una concatenación en paralelo de dos códigos convolucionales y el problema de la terminación trellis. Se describe un método de terminación particular que se puede utilizar para índices desiguales y codificadores. De acuerdo con este método de terminación, de proporciona un cambio que está en una primera posición para los primeros N ciclos de reloj y en una segunda posición para M ciclos adicionales. Aquellos M ciclos adicionales vaciará los codificadores con ceros.

Bomer, L., et al.: "A CDMA Radio Link con ``Turbo -Decoding'': Concept y Performance Evaluation", 6th IEEE symposium y personal, indoor y mobile radio communications PIMRC'1995 Volumen 2, Septiembre 27, 1995, paginas 788-793, describe una...

Reivindicaciones:

1. Un codificador turbo para codificar bits de información de entrada, que comprende:

un primer codificador de componente (410) para codificar bits de información de entrada en una trama para generar primeros bits de paridad;

un intercalador (430) para intercalar los bits de información de entrada, y un segundo codificador de componente (420) para codificar los bits de información de entrada intercalada para generar segundos bits de paridad,

caracterizados porque

un primer generador de bits de cola (450) separado del primer codificador de componente (410) para generar primeros bits de cola es igual a valores retroalimentados del primer codificador de componente (410) para terminar el primer codificador de componente, dicho primer generador de bits de cola comprende unos medios X-OR;

un segundo generador de bits de cola (460) separado del segundo codificador de componente (420) para generar segundos bits de cola que son iguales a los valores retroalimentados de los segundos codificador de componente (420) para terminar el segundo codificador de componentes, dicho segundo generador de bits de cola comprende unos medios X-OR;

un primer interruptor (455) para conmutar los valores retroalimentados del primer codificador de componente (410) al primer codificador de componentes como los primeros bits de cola en el extremo de la trama, y

un segundo interruptor (465) para conmutar los valores de retroalimentados del segundo codificador de componente (420) al segundo codificador de componentes como el segundo bits de cola en el extremo de la trama,

en donde cada uno de los codificadores de componentes (410, 420) requiere bits de cola tanto como memorias del codificador de componente que están dispuestas para codificar bits de información de entrada de tamaños de trama variables, en donde los codificadores de componente (410, 420) generan un bit de información y dos bits de paridad en respuesta a proporcionar cada uno de los bits de información al codificador de componente y generar dos bits de de cola y dos los bits de paridad en respuesta a proporcionar cada uno de los primeros y segundos bits de cola al codificador de componente (410, 420).

2. El código turbo de acuerdo con la reivindicación 1, que comprende adicionalmente:

Un punzador (480) para punzar una de los primeros bits de paridad o los segundos bits de paridad a la vez.

3. El código turbo de acuerdo con la reivindicación 1, que comprende adicionalmente: un multiplexor (491) para multiplexar los primeros bits de cola y los segundos bits de cola.

4. El código turbo de acuerdo con la reivindicación 1, en donde el primer codificador de componente (410) codifica los bits de información de entrada o los primeros bits de cola para generar los primeros bits de paridad, y el segundo codificador de componente (420) codifica los bits de información de entrada intercalados o los segundos bits de cola para generar los segundos bits de paridad.

5. El código turbo de acuerdo con la reivindicación 4, en donde los bits de cola se cargan en cada codificador de componente (410, 420) después que se han codificado todos los bits de información de entrada.

6. Un método de codificación de canal para uso en un codificador de canal que tiene un primer codificador de componente (410) y un segundo codificador de componentes (420), caracterizados porque

Comprende las etapas de:

recibir bits de información de entrada;

generar primeros bits de paridad de los bit de información de entrada y primeros valores retroalimentación mediante el primer codificador de componente (410);

intercalar los bits de información de entrada adaptativamente de acuerdo con el número de bits de información de entrada;

generar segundos bits de paridad de los bits de información de entrada intercalados y segundos valores retroalimentación mediante el segundo codificador de componentes (420);

generar mediante un primer generador de bits de cola (450) separado del primer codificador de componente (410) y que comprende unos medios X-OR (451) primeros bits de cola y mediante un segundo generador de bits de cola (460) separado del segundo codificador de componentes (420) y que comprende unos medios X-OR (461) segundos bits de cola que son iguales al primeros y segundos valores de retroalimentación,

respectivamente para terminar las memorias en los primeros y segundos codificadores de componente (410, 420) y alimentar los bits de cola en el primero y segundo codificador de componente, y

punzar la salidas de los codificadores de componente (410, 420) para ajustar un índice de transmisión, en donde cada uno de los codificadores de componente (410, 420) requiere bits de cola tanto como memorias del codificador de componente que están dispuestas para codificar los bits de información de entrada de tamaños de trama variables, en donde un bit de información y dos bits de paridad se generan en respuesta a proporcional cada uno de los bits de información al codificador de componente y dos bits de cola y dos bits de paridad se generan en respuesta a proporcionar cada uno de los primeros y segundos bits de cola a los codificadores de componente (410, 420).

7. El método de codificación de canal de acuerdo con la reivindicación 6, en donde los bits de cola se cargan a cada codificador de componente (410, 420) después que se han codificado todos los bit de información de entrada.

8. El método de codificación de canal de acuerdo con la reivindicación 6, que comprende la etapa adicional de:

multiplexar los primeros bits de cola y los segundos bits de cola.

9. El codificador turbo de acuerdo con la reivindicación 1, que comprende adicionalmente:

Una entrada para recibir bits de tamaño variable de bits de información de entrada y una salida para generar los bits de información;

un punzador (480) para punzar una parte de los primeros y segundos los bits de paridad para ajustar el índice de transmisión de datos, en donde se genera un número de bits de cola idénticos al número de memorias de retraso en el índice de transmisión de datos, en donde se genera un número de bits de cola idéntico al número de memorias de retraso para terminar el codificador de componentes (410, 420) y los bits de cola se transmiten en la salida de los bits de información;

en donde el primer codificador de componente (420) tiene un número predeterminado de memorias de retraso para codificar los bits de información de entrada recibidos desde la entrada y generar los primeros los bits de paridad y

el intercalador (430) intercala los bits de información de entrada recibidos de la entrada y el segundo codificador de componentes (420) tiene un número predeterminado de memorias de retraso para codificar los bits de información intercalada y generar segundos bits de paridad.

10. El dispositivo de codificación de canal de acuerdo con la reivindicación 9, en donde la información de entrada y los bits de paridad se punzan en forma separada.

11. El dispositivo de codificación de canal de acuerdo con la reivindicación 9, en donde no toda la información de entrada, los primeros bits de paridad, y los segundos bits de paridad se punzan.

12. El dispositivo de codificación de canal de acuerdo con la reivindicación 9, en donde no todos los primero bits de paridad y los segundos bits de paridad se punzan.

Patentes similares o relacionadas:

Método y aparato para la transmisión inalámbrica de datos sujetos a bloqueos de señal periódicos, del 6 de Mayo de 2020, de Hughes Network Systems, LLC: Un método, que comprende: segmentar (S311, S321, S331) un flujo de datos en paquetes de un tamaño fijo para una transmisión en modo ráfaga a través de […]

Método y aparato para la transmisión inalámbrica de datos sujeta a bloqueos de señal periódicos, del 23 de Octubre de 2019, de Hughes Network Systems, LLC: Un método para la transmisión inalámbrica de una primera corriente de datos, estando la transmisión sujeta a bloqueos periódicos, el método que comprende: segmentar una […]

Aparato y método de procesamiento de datos, del 25 de Septiembre de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos operable para mapear símbolos de datos recibidos de un número predeterminado de señales de subportadoras de símbolos […]

Aparato y método de procesamiento de datos, del 25 de Septiembre de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos operable para mapear símbolos de datos recibidos de un número predeterminado de señales de subportadoras de símbolos […]

Intercalador de bits para un sistema de BICM con códigos de QC-LDPC, del 3 de Julio de 2019, de PANASONIC CORPORATION: Un procedimiento de intercalación de bits para intercalar bits de una palabra de código generada en base a un esquema de codificación de comprobación de paridad de baja densidad […]

Aparato y método de procesamiento de datos, del 8 de Mayo de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos para mapear símbolos recibidos desde un número predeterminado de señales de subportadoras de un símbolo multiplexado por división ortogonal […]

Intercalador de bits para un sistema de BICM con códigos QC LDPC, del 6 de Marzo de 2019, de PANASONIC CORPORATION: Un procedimiento de entrelazado de bits para entrelazar bits de una palabra de código generada basándose en un esquema de codificación de verificación de paridad de baja densidad […]

Entrelazador de bits para un sistema BICM con códigos QC LDPC, del 28 de Febrero de 2019, de PANASONIC CORPORATION: Un método de entrelazado de bits para entrelazar bits de una palabra de código generada en base a un esquema de codificación con comprobación de paridad de baja densidad […]

Método de codificación del código polar y dispositivo de codificación, del 27 de Febrero de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación del código polar, caracterizado por comprender: asignar M bits reservados de una señalización de difusión a M bits […]