APARATO PARA CONMUTAR DE FORMA DINAMICA LA FUENTE DEL RELOJ DE UN SISTEMA DE PROCESO DE DATOS.

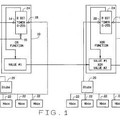

UN SISTEMA DE PROCESO DE DATOS INCLUYE UN PRIMER Y UN SEGUNDO SISTEMACENTRAL EN DONDE LA UNIDAD CENTRAL DE PROCESO (CPU) DEL PRIMER SISTEMA CENTRAL ESTA CONECTADA A LA UNIDAD DE CONTROL DEL SISTEMA (SCU) DEL SEGUNDO SISTEMA CENTRAL Y LA CPU DEL SEGUNDO SISTEMA CENTRAL ESTA CONECTADA A LA SCU DEL PRIMER SISTEMA CENTRAL,

CADA SISTEMA CENTRAL INCLUYE UN PROCESADOR DE SERVICIO Y UN SUBSISTEMA TEMPORIZADOR PARA SUMINISTRAR SEÑALES DE RELOJ. CADA SISTEMA CENTRAL INCLUYE UN APARATO PARA DISTRIBUIR LAS SEÑALES DE RELOJ DE TAL MANERA QUE CADA SISTEMA CENTRAL SE TEMPORIZA A PARTIR DE SEÑALES PREDETERMINADAS DE TEMPORIZACION EN RESPUESTA A LAS SEÑALES DE CONTROL DEL PROCESADOR DE SERVICIOS. EL APARATO PERMITE QUE LA DISTRIBUCCION DE LAS SEÑALES DE TEMPORIZACION SEA DINAMICAMENTE CONMUTADA MIENTRAS LOS SISTEMAS CENTRALES ESTAN FUNCIONANDO, LA CONMUTACION DE LAS SEÑALES DE RELOJ SE REALIZA SIN AFECTAR EL FUNCIONAMIENTO DE LOS SISTEMAS CENTRALES. EL APARATO COMPRENDE UN ELEMENTO GENERADOR PARA GENERAR SEÑALES DE RELOJ LOCALES. UN PRIMER ELEMENTO LOGICO GENERA UNA SEÑAL DE ALTO EN UN MOMENTO PREDETERMINADO CON RELACION A LAS SEÑALES DE RELOJ LOCALES EN RESPUESTA A PREDETERMINADAS SEÑALES DE CONTROL. UN ELEMENTO CONMUTADOR DA SALIDA EN FORMA CONDICIONAL A LAS SEÑALES DE RELOJ LOCALES EN RESPUESTA A LA SEÑAL DE ALTO. UN SELECTOR QUE RECIBE SEÑALES DE RELOJ REMOTAS DESDE EL SUBSISTEMA DE TEMPORIZACION DEL OTRO SISTEMA CENTRAL DA SALIDA SELECTIVAMENTE A LAS SEÑALES DE RELOJ LOCALES O A LAS SEÑALES DE RELOJ REMOTAS EN RESPUESTA A LAS SEÑALES DE CONTROL PREDETERMINADAS, LAS SEÑALES DE CONTROL SON MODIFICADAS DURANTE UN PERIODO DE TIEMPO MIENTRAS LA SEÑAL DE ALTO ESTA ACTIVO, PERMITIENDO ASI AL SELECTOR SELECCIONAR SEÑALES DE RELOJ ALTERNAS ANTES DE QUE LA SEÑAL DE ALTO SE VUELVA INACTIVA CONMUTANDO DE ESTA FORMA LA FUENTE DE LAS SEÑALES DE RELOJ QUE ESTAN TEMPORIZANDO LOS SISTEMAS CENTRALES SIN PERTURBAR LAS TAREAS QUE ESTAN SIENDO EJECUTADAS EN LOS SISTEMAS CENTRALES.

Tipo: Resumen de patente/invención.

Solicitante: BULL HN INFORMATION SYSTEMS INC..

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 300 CONCORD ROAD, BILLERICA, MA 01821-4186.

Inventor/es: CALLE, JAIME.

Fecha de Publicación: .

Fecha Concesión Europea: 11 de Enero de 1995.

Clasificación Internacional de Patentes:

- G06F1/04 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 1/00 Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76). › Generación o distribución de señales de reloj o de señales derivadas directamente de éstas.

Patentes similares o relacionadas:

Unidad lógica secuencial de múltiples suministros de energía, del 4 de Octubre de 2017, de INTEL CORPORATION: Un aparato para mejorar la velocidad de una unidad lógica secuencial que comprende: una ruta de datos, configurada para recibir una señal de entrada, que […]

Base de tiempos programable, del 6 de Abril de 2016, de MICROCHIP TECHNOLOGY INCORPORATED: Un microcontrolador que comprende una base de tiempos programable, comprendiendo la base de tiempos una indicación de activación para poner en marcha un temporizador […]

Establecimiento de llamada de telecomunicación de medios mixtos, del 18 de Marzo de 2016, de 3G Licensing S.A: Estación móvil apta para videotelefonía en respuesta a una interrupción de una llamada en curso de telecomunicaciones de medios mixtos, comprendiendo […]

Establecimiento de llamada de telecomunicación de medios mixtos, del 18 de Marzo de 2016, de 3G Licensing S.A: Estación móvil apta para videotelefonía en respuesta a una interrupción de una llamada en curso de telecomunicaciones de medios mixtos, comprendiendo […]

Generador de datos estadísticos no deterministas, del 29 de Abril de 2013, de DIS-ENT, LLC: Un procedimiento de generación de bits aleatorios no deterministas y no periódicos que comprende las etapas de: proporcionar una pluralidad de generadores […]

Generador de datos estadísticos no deterministas, del 29 de Abril de 2013, de DIS-ENT, LLC: Un procedimiento de generación de bits aleatorios no deterministas y no periódicos que comprende las etapas de: proporcionar una pluralidad de generadores […]

CIRCUITO PARA DESPLAZAR LA FASE DE RELOJ SIN PASOS DE FORMA PROGRAMABLE., del 1 de Abril de 2006, de ALCATEL: Un circuito para desplazamiento de fase programable sin pasos de reloj, que comprende: - un divisor (DIVISOR) que recibe una referencia de reloj […]

CIRCUITO INTEGRADO SINCRONIZADOR DE DATOS ENTRE REDES., del 1 de Marzo de 1999, de TELEFONICA DE ESPAÑA, S.A.: CIRCUITO INTEGRADO SINCRONIZADOR DE DATOS ENTRE REDES, QUE CONSISTE EN UN GENERADOR DE TEMPORIZACIONES Y DOS SINCRONIZADORES DE DATOS IDENTICOS (21 […]

GENERADORES DE FORMA DE ONDAS DE RELOJ DIGITAL, del 16 de Mayo de 1997, de ADVANCED MICRO DEVICES INC.: SE PROPORCIONAN UN GENERADOR DE FORMA DE ONDAS DE RELOJ DIGITAL, Y METODO PARA GENERAR UNA SEÑAL DE RELOJ, PARA UN MICROPROCESADOR U OTRO CIRCUITO DIGITAL […]

ALIMENTACION DE UN SISTEMA DE SEGURIDAD DE IMPULSOS DE RELOJ PARA SISTEMAS DIGITALES, del 16 de Abril de 1996, de SIEMENS AKTIENGESELLSCHAFT: SE TRATA DE UN SUMINISTRO ADICIONAL DE CICLOS PARA SISTEMAS DIGITALES, SOBRE TODO PARA SISTEMAS MULTIPLEX SINCRONIZADOS Y SISTEMAS OPERADORES, CON UN OSCILADOR […]