Procedimiento de protección de la ejecución de un código informático mediante redundancia dinámica.

Procedimiento de proteccion de la ejecución de un c6digo informatico por un microprocesador,

estando dividido dicho codigo en funciones elementales (1, 2, 3, 4, 5, 6), comprendiendo dicha ejecución la utilización de un contador, llamado NC, actualizado (11, 12, 13, 14, 15) despues de la ejecución de cada dicha función elemental, y de al menos dos variables de protección r0 y r1, caracterizado porque comprende al menos las etapas de: inicialización de las variables de protección,

identificación de un punto de redundancia, despues de cada incremento de contador NC, por la aplicacion de una función de comparación FC a dicho contador NC y a dicha variable,

Desencadenamiento de una etapa de redundancia cuando dicha función de comparación FC devuelve un exito, consistiendo dicha etapa de redundancia en la aplicacion de una función booleanas "SENS" a la citada variable r1, y en un inicio, en función del valor de retorno de dicha función SENS, de una función "redundancia posterior" o de as funciones elementales ya ejecutadas antes de que el punto de redundancia sea ejecutado de nuevo, o de una función "redundancia anterior" o las funciones elementales ejecutadas despues de que el punto de redundancia identificado sea ejecutado de nuevo,

reanudación de la ejecución de dichas funciones elementales que queden eventualmente por ejecutar.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2011/065679.

Solicitante: GEMALTO SA.

Nacionalidad solicitante: Francia.

Dirección: 6, RUE DE LA VERRERIE 92190 MEUDON FRANCIA.

Inventor/es: VILLEGAS,KARINE, GAUTERON,LAURENT.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F21/52 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 21/00 Disposiciones de seguridad para la protección de computadores, sus componentes, programas o datos contra actividades no autorizadas. › durante la ejecución del programa, p. ej.: integridad de la pila, desbordamiento de búfer o la prevención de borrado de datos durante la ejecución del programa, p. ej. integridad de la pila, desbordamiento de búfer o la prevención de borrado de datos no deseados.

PDF original: ES-2527581_T3.pdf

Fragmento de la descripción:

Procedimiento de protección de la ejecución de un código informático mediante redundancia dinámica.

La presente invención se refiere al campo de la seguridad y la protección de la ejecución de un código informático por una unidad de procesamiento de un equipo electrónico, y los dispositivos asociados, tales como tarjetas inteligentes.

Las tarjetas inteligentes son objeto de numerosos intentos de pirateo por ataques activos o pasivos. Un ataque activo implica la inyección de un fallo para alterar físicamente el circuito integrado del chip para cambiar el comportamiento de este último y desviar el código de software hacia otro tipo de ejecución.

En contraste con un ataque pasivo, por ejemplo por el canal lateral (side-canal), el atacante intenta realizar un análisis estadístico de cantidades medióles del chip como la corriente de alimentación o la radiación electromagnética emitida por el chip, para controlar o deducir las tareas de ejecución del chip.

Para paliar este tipo de ataques, es conocido el usar y insertar, cuando se ejecuta un comando, un retardo aleatorio, es decir, retardos cuya duración es elegida de manera aleatoria o pseudo-aleatoria como contramedida contra este tipo de ataques, para hacerlos más difíciles de realizar. De hecho, la presencia de estos retrasos aleatorios hace que sea difícil determinar el momento en el que el fallo ha de ser inyectado por el atacante durante la ejecución de un proceso y evita al atacante sincronizarse para llevar a cabo mediciones por un canal lateral.

En la presente descripción y reivindicaciones se entenderá por "código fuente", una secuencia de instrucciones ejecutables que forman parte o la totalidad de una aplicación informática.

Del mismo modo, se entiende por "código ejecutado" una secuencia de instrucciones realmente ejecutadas por el procesador durante la ejecución de la totalidad o parte de la solicitud correspondiente.

Es conocido el hecho de insertar en el código fuente, fragmentos de código cuyo resultado no es necesario para la ejecución normal del código en cuestión. Estas porciones de código son generalmente llamadas "señuelo". Estos señuelos tienen como particularidad, que en un análisis de canal lateral, parecen secuencias reales importantes de código.

Dichas contramedidas (señuelos o retrasos aleatorios) tienen un objetivo común de hacer los ataques externos más difíciles impidiendo al atacante entender y/o predecir con precisión la ejecución del programa.

Es frecuente introducir tales contramedidas en múltiples emplazamientos temporales durante la ejecución de un código de fuente por el chip. En particular, se ha pensado para asegurar con dichas contramedidas la ejecución de operaciones delicadas o de riesgo (como una lectura/escritura en memoria, un cálculo criptográfico, un algoritmo para una toma de decisiones). De hecho, estas operaciones delicadas son las más solicitadas por los piratas, parece lógico insertar numerosas contramedidas a largo de la ejecución del código fuente, antes y durante tales operaciones delicadas.

Una desventaja de esta solución es que es posible detectar la presencia de estas contramedidas durante el análisis por el canal lateral, a pesar de los esfuerzos para hacerlas lo menos visibles posible. Estas contramedidas se colocan generalmente cerca de las secuencias criticas del código fuente, su detección se puede utilizar para calibrar los ataques más cerca de los puntos cruciales.

El documento US 24/34823 describe un método de protección de la ejecución de un código por un microprocesador que utiliza un cálculo de suma de control sobre la señal de dirección del procesador cuando el contador ordinal esté entre dos direcciones predeterminadas que constituyen una dirección de partida y una dirección de fin de cálculo de la suma de control. Esta suma de control permite verificar la ejecución correcta de la secuencia de instrucciones entre las dos direcciones predeterminadas.

La presente invención pretende resolver los inconvenientes del estado de la técnica proponiendo hacer variar el código ejecutado de una ejecución a otra a través de redundancias, y la verificación de resultados intermedios.

Para ello, la invención consiste en un procedimiento para proteger la ejecución de código informático por un microprocesador, estando dividido dicho código informático en funciones elementales, comprendiendo la ejecución la utilización de un contador, llamado NO, actualizado después de la ejecución de cada función elemental, al menos dos variables de protección rO y r1. Este método comprende al menos las etapas de:

inicialización de las variables de seguridad

identificación del punto de redundancia, después de cada incremento del contador CN, una función de comparación FC se aplica al contador NC y a la variable rO, cuando la función de comparación FC devuelve un

éxito, activación de la etapa de redundancia.

redundancia, aplicación de una función booleana "SENS a la variable r1,

dependiendo del valor de retorno de la función SENS, inicio de la función "redundancia posterior", o inicio de la función "redundancia anterior

reanudación de la ejecución de las funciones elementales que queden eventualmente por ejecutar.

De acuerdo con una forma de realización, la función "redundancia posterior puede incluir al menos las etapas de:

calcular un valor CHKO a partir de los resultados de la totalidad o parte de las funciones elementales ejecutadas llamadas "subconjunto redundante",

reejecución de las funciones elementales que componen este "subconjunto redundante", formando un nuevo conjunto llamado "subconjunto redundante",

calcular un valor de CHK1 a partir de los resultados de las funciones elementales del "subconjunto redundante"

la aplicación de una función de comparación COMP a los valores CHKO y CHK1.

De acuerdo con una forma de realización, la "redundancia anterior puede comprender al menos las etapas de:

la ejecución de la totalidad o parte de las funciones elementales pendientes de ejecutar llamadas "subconjunto redundante",

calcular un valor CHKO a partir de los resultados de las funciones elementales que componen el "subconjunto redundante",

reejecución de las funciones elementales que componen el "subconjunto redundante", formando un nuevo conjunto llamado "subconjunto redundante"

calcular un valor de CHK1 a partir de los resultados de las funciones elementales del "subconjunto redundante"

la aplicación de una función de comparación COMP a los valores CHKO y CHK1.

Según una forma de implementación, la variable rO puede ser inicializada con un número entero aleatorio menor o igual al número total de funciones elementales que componen el código informático.

Según una forma de implementación, la variable r1 puede ser inicializada con un valor booleano aleatorio.

Según una forma de implementación, el procedimiento puede comprender además una variable r2, inicializada durante la etapa de la redundancia de tal manera que,

si el valor de retorno de la función "SENS" desencadena una redundancia posterior, entonces la variable r2 se inicializa con un entero aleatorio inferior o igual al número de funciones elementales ejecutadas,

si el valor de retomo de loa función "SENS" desencadena una redundancia anterior, entonces la variable r2 se inicializa con un entero aleatorio inferior o igual al número de funciones elementales que restan por ejecutar.

En este caso, en la función "redundancia posterior", el "subconjunto redundante" se define por las funciones elementales r2 últimas ejecutadas. Del mismo modo, en la "redundancia anterior", el "subconjunto redundante" se define por las funciones elementales r2 siguientes ejecutadas.

Dependiendo del modo de implementación, la función FC puede ser la función de "igualdad".

Dependiendo del modo de implementación, la función "SENS es una función que tiene la misma probabilidad de desencadenar una redundancia anterior o una redundancia posterior. Por lo tanto, la función "SENS puede desencadenar una redundancia anterior si r1 es igual a 1, y desencadenar una redundancia posterior si r1 es igual a.

Otras características y ventajas de la invención serán evidentes a partir de la descripción que viene a continuación, a título indicativo y no limitativo, con referencia a las figuras adjuntas en las que:

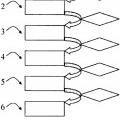

La figura 1 muestra las funciones elementales introducidas que conforman un código de referencia

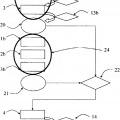

La figura 2 muestra un primer ejemplo de código ejecutado cuando la presente invención se aplica al código de la figura 1

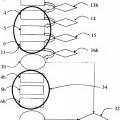

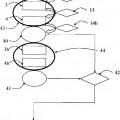

La figura 3 muestra... [Seguir leyendo]

Reivindicaciones:

1. Procedimiento de protección de la ejecución de un código informático por un microprocesador, estando dividido dicho código en funciones elementales (1, 2, 3, 4, 5, 6), comprendiendo dicha ejecución la utilización de un contador, llamado NC, actualizado (11, 12, 13, 14, 15) después de la ejecución de cada dicha función elemental, y de al menos dos variables de protección rO y r1, caracterizado porque comprende al menos las etapas de:

inicialización de las variables de protección,

identificación de un punto de redundancia, después de cada incremento de contador NC, por la aplicación de una función de comparación FC a dicho contador NC y a dicha variable,

Desencadenamiento de una etapa de redundancia cuando dicha función de comparación FC devuelve un éxito, consistiendo dicha etapa de redundancia en la aplicación de una función booleanas SENS a la citada variable r1, y en un inicio, en función del valor de retorno de dicha función SENS, de una función "redundancia posterior" o de las funciones elementales ya ejecutadas antes de que el punto de redundancia sea ejecutado de nuevo, o de una función "redundancia anterior o las funciones elementales ejecutadas después de que el punto de redundancia identificado sea ejecutado de nuevo,

reanudación de la ejecución de dichas funciones elementales que queden eventualmente por ejecutar.

2. Procedimiento de acuerdo con la reivindicación 1 caracterizado porque la citada función "redundancia posterior" incluye al menos las etapas de:

- Cálculo (2, 3, 4) de un valor CHKO a partir de los resultados de la totalidad o parte de dichas funciones

elementales ejecutadas llamadas ``subconjunto redundante" (23, 33, 43),

re-ejecución de dichas funciones elementales que componen dicho "subconjunto redundante", formando un nuevo conjunto llamado subconjunto redundante" (24, 34, 44),

cálculo (21, 31, 41) de un valor CHK1, a partir de los resultados de las funciones elementales de dicho "subconjunto redundante,

- aplicación de una función de comparación COMP a los valores CHKO y CHK1 (22, 32, 42).

3. Procedimiento de acuerdo con la reivindicación 1 caracterizado porque la citada función "redundancia anterior" incluye al menos las etapas de:

ejecución de la totalidad o parte de las funciones elementales pendientes de ejecución llamadas "subconjunto redundante" (23, 33, 43),

cálculo (2, 3, 4) de un valor CHKO a partir de los resultados de la totalidad o parte de dichas funciones 25 elementales ejecutadas llamadas subconjunto redundante" (23, 33, 43),

re-ejecución de dichas funciones elementales que componen dicho "subconjunto redundante", formando un nuevo conjunto llamado "subconjunto redundante" (24, 34, 44),

cálculo (21, 31, 41) de un valor CHK1, a partir de los resultados de las funciones elementales de dicho "subconjunto redundante",

aplicación de una función de comparación COMP a los valores CHKO y CHK1 (22, 32,42).

4. Procedimiento de acuerdo con la reivindicación 1, caracterizado porque la variable rO se inicializa con un entero aleatorio inferior o igual al número total de funciones elementales que componen dicho código informático.

5. Procedimiento de acuerdo con la reivindicación 1, caracterizado porque la variable r1 se inicializa con un valor booleano aleatorio.

6. Procedimiento de acuerdo con la reivindicación 1, caracterizado porque comprende además una variable r2, iniciaiizada durante la citada etapa de redundancia tal que,

si el valor de retorno de la citada función SENS" desencadena una redundancia posterior, entonces dicha variable r2 se inicializa con un entero aleatorio inferior o igual al número de funciones elementales ejecutadas,

si el valor de retorno de la citada función "SENS" desencadena la redundancia anterior, entonces dicha variable r2 se inicializa con un entero aleatorio Inferior o igual al número de funciones elementales pendientes de ejecutar.

7. Procedimiento de acuerdo con la reivindicación 6 caracterizado porque, en dicha función "redundancia posterior" dicho "subconjunto redundante" se define por las últimas funciones elementales r2 ejecutadas.

8. Procedimiento de acuerdo con la reivindicación 6 caracterizado porque, en dicha función "redundancia anterior dicho "subconjunto redundante se define por las siguientes funciones elementales r2 ejecutadas.

9. Procedimiento según una de las reivindicaciones 2 a 5, caracterizado porque la citada función FC es la función "igualdad".

1. Procedimiento según una de las reivindicaciones 1 a 5, caracterizado porque la citada función "SENS" es una función que tiene la misma probabilidad de desencadenar una redundancia anterior que una redundancia posterior.

11. Procedimiento según la reivindicación 1 caracterizado porque la citada función "SENS desencadena una redundancia anterior si r1 es igual a 1, y desencadena una redundancia posterior si r1 es igual a.

Patentes similares o relacionadas:

Servidor de seguridad de soporte lógico, del 19 de Febrero de 2020, de Idemia Identity & Security France: Procedimiento de verificación de ejecución de applets (AA1, AB1) desarrolladas en un lenguaje orientado objeto y compiladas en código intermedio, siendo el procedimiento […]

Sistema informático asegurado con autenticación asíncrona, del 1 de Enero de 2020, de Winbond Electronics Corp: Dispositivo informático, que comprende: un puente de entrada, que se acopla para recibir una secuencia de elementos de datos para su uso mediante el […]

Procedimiento de segurización de al menos una zona de memoria de un dispositivo electrónico, módulo de segurización, dispositivo electrónico y programa de ordenador correspondientes, del 25 de Septiembre de 2019, de Ingenico Group: El procedimiento de segurización de al menos 1 a de memoria de un dispositivo electrónico que comprende las siguientes etapas:

- detección […]

Procedimiento de segurización de al menos una zona de memoria de un dispositivo electrónico, módulo de segurización, dispositivo electrónico y programa de ordenador correspondientes, del 25 de Septiembre de 2019, de Ingenico Group: El procedimiento de segurización de al menos 1 a de memoria de un dispositivo electrónico que comprende las siguientes etapas:

- detección […]

Integridad de descifrado de código bajo demanda, del 3 de Julio de 2019, de NAGRAVISION SA: Método para supervisar la integridad de código, que comprende: recibir uno o más archivos en los que el código ficticio ocupa un área de descifrado de código bajo demanda […]

Codificación de etiquetas en valores para capturar los flujos de información, del 5 de Abril de 2019, de QUALCOMM INCORPORATED: Un procedimiento para codificar etiquetas de seguridad en un valor de lenguaje dinámico, que comprende: asignar una cantidad de bits en el valor del lenguaje […]

Protección de procesos antimalware, del 3 de Abril de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento que comprende: recibir , mediante un dispositivo informático, un certificado de confianza de una fuente verificada; […]

Gestión de aplicaciones relacionadas con módulos seguros, del 6 de Marzo de 2019, de Nokia Technologies OY: Un aparato capaz de alojar un módulo seguro , comprendiendo el aparato: medios de memoria para almacenar al menos una aplicación ; medios de […]

Procedimiento y entorno de ejecución para la ejecución asegurada de instrucciones de programa, del 25 de Febrero de 2019, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para la ejecución asegurada y asistida por ordenador de una aplicación con las siguientes etapas del procedimiento: - encendido […]