INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA.

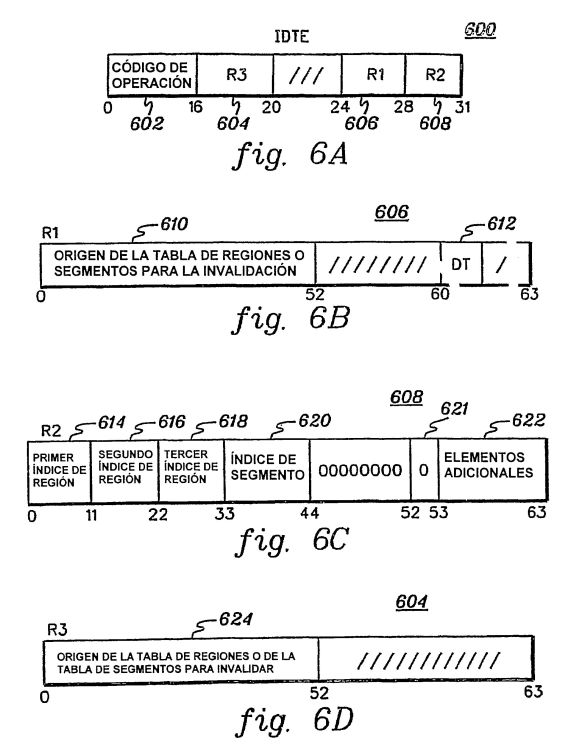

Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción de direcciones,

dispuestas en tablas de segmentos y tablas de regiones, donde un elemento en una tabla de regiones corresponde a una tabla de segmentos, para traducir dinámicamente direcciones virtuales a direcciones de almacenamiento principal, el método comprende los pasos de: determinar la instrucción ejecutable desde un código de operación de una máquina para ser ejecutada, que la instrucción esté configurada para iniciar la ejecución de una operación de invalidación y borrado; y ejecutar la instrucción, comprendiendo el paso de ejecución las etapas de: interpretar la instrucción para identificar una rutina de software determinada para emular la operación de la instrucción en una unidad central de procesamiento subyacente que tiene una arquitectura de conjuntos de instrucciones diferente, la rutina de software predeterminada comprende una pluralidad de instrucciones; ejecutar la rutina de software predeterminada; invalidar (402, 404, 406) la gama de dos o más elementos de una tabla de traducción de direcciones; en la que la gama es especificada como una gama específica de elementos de una tabla de traducción de direcciones.

Tipo: Resumen de patente/invención.

Solicitante: INTERNATIONAL BUSINESS MACHINES CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: NEW ORCHARD ROAD,ARMONK, N.Y. 10504.

Inventor/es: SLEGEL,TIMOTHY IBM UK LTD.,I.P.L, HELLER,LISA IBM UK LTD.,I.P.L, PFEFFER,ERWIN IBM UK LTD.,I.P.L, PLAMBECK,KENNETH IBM UK LTD.,I.P.L.

Fecha de Publicación: .

Fecha Solicitud PCT: 6 de Mayo de 2004.

Fecha Concesión Europea: 6 de Mayo de 2009.

Clasificación PCT:

- G06F12/10 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Traducción de direcciones.

- G06F9/30 G06F […] › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

- G06F9/318 G06F 9/00 […] › con extensión o modificación de operaciones.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Patentes similares o relacionadas:

Microprocesador o microcontrolador potenciado, del 27 de Febrero de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un dispositivo de microprocesador de n bits que comprende: una unidad central de procesamiento de n bits (CPU); una pluralidad de registros […]

MICROPROCESADOR CON SELECCIÓN AUTOMÁTICA DE PARALELISMO SIMD, del 9 de Junio de 2011, de QUALCOMM INCORPORATED: Un procedimiento para controlar el paralelismo de operaciones en un procesador de datos en paralelo, que comprende: monitorizar una o más condiciones […]

MECANISMO EN UN MICROPROCESADOR PARA EJECUTAR INSTRUCCIONES NATIVAS DIRECTAMENTE DESDE LA MEMORIA, del 13 de Enero de 2011, de IP-FIRST LLC: Un aparato en un microprocesador para ejecutar las instrucciones nativas que se proporcionan directamente al microprocesador a través de un canal principal […]

SISTEMA DE PROCESAMIENTO DE DATOS CON EJECUCION CONDICIONAL DE INSTRUCCIONES COMPUESTAS EXTENDIDAS., del 16 de Diciembre de 2004, de MOTOROLA, INC.: Un sistema para dar órdenes a un procesador de datos, el sistema incluye una raíz de instrucción que tiene un campo de selección de operación para seleccionar […]

SISTEMA INFORMATICO., del , de COMMUNICATE LTD.: EN UN SISTEMA DE ORDENADOR CON UN PROCESADOR RISC QUE UTILIZA INSTRUCCIONES DE 32 BITS, CIERTAS INSTRUCCIONES SE ALMACENAN EN FORMA COMPRIMIDA DE 16 BITS Y SE EXPANDEN […]

MICROPROCESADOR QUE UTILIZA UN CAMPO DE INSTRUCCION PARA ESPECIFICAR FUNCIONALIDAD EXTENDIDA, del 1 de Junio de 1999, de ADVANCED MICRO DEVICES INC.: SE DESCRIBE UN MICROPROCESADOR QUE EXPANDE LA FUNCIONALIDAD O RENDIMIENTO DE UNA ARQUITECTURA IMPLEMENTADA DE MANERA TRANSPARENTE O NO TRANSPARENTE. EL […]

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

INSTRUCCIONES DE ASISTENCIA AL TRATAMIENTO DE UN MENSAJE CIFRADO, del 16 de Agosto de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método de cifrar o descifrar almacenamiento de un entorno de ordenador, comprendiendo dicho método: especificar, mediante una instrucción de microprocesador, […]

INSTRUCCIONES DE ASISTENCIA AL TRATAMIENTO DE UN MENSAJE CIFRADO, del 16 de Agosto de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método de cifrar o descifrar almacenamiento de un entorno de ordenador, comprendiendo dicho método: especificar, mediante una instrucción de microprocesador, […]