DISPOSITIVO PARA LA MEJORA DE LA SEGURIDAD DE MICROPROCESADORES EN SISTEMAS EMPOTRADOS.

Dispositivo para la mejora de la seguridad de microprocesadores en sistemas empotrados.

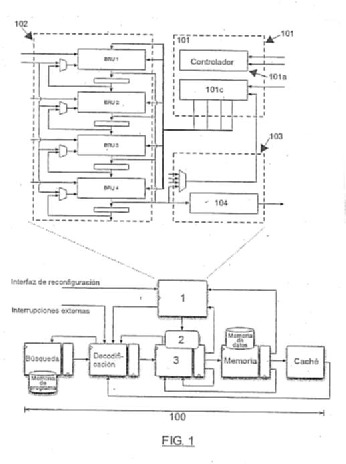

Dispositivo para la mejora de la seguridad de sistemas empotrados basados en microprocesador, de tipo reconfigurable y de bajo consumo, que permite la ejecución de operaciones vectoriales, y que comprende, al menos:(a) una primera unidad vectorial reconfigurable (1) diseñada como una ruta de datos segmentada con múltiples contextos configurables independientemente, y que comprende, al menos, tres etapas o bloques:(i) una primera etapa de decodificación (101) configurada para la obtención de la información de la operación y los operandos involucrados en la ejecución;(ii) una segunda etapa de ejecución (102) que a su vez comprende una pluralidad de unidades reconfigurables básicas conectadas en cascada; y(iii) una tercera etapa de salida (103);(b) una segunda unidad de carga y almacenamiento vectorial (2) integrada en la unidad de ejecución (3) de la ruta de datos principal (100)

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200900442.

Solicitante: UNIVERSIDAD POLITECNICA DE MADRID.

Nacionalidad solicitante: España.

Provincia: MADRID.

Inventor/es: NIETO-TALADRIZ GARCIA,OCTAVIO, FRAGA AYDILLO,DAVID, DE GOYENECHE Y VAZQUEZ DE SETAS,JUNA-MARIANO, MALAGON MARZO,PEDRO, ARAUJO PINTO,ALVARO, RUBIO MINGORANCE,AGUSTIN, VALLEJO LOPEZ,JUAN CARLOS, VILLANUEVA GONZALEZ,DANIEL, MOYA FERNANDEZ,JOSE MANUEL, ROMERO PERALES,ELENA.

Fecha de Solicitud: 17 de Febrero de 2009.

Fecha de Publicación: .

Fecha de Concesión: 28 de Enero de 2011.

Clasificación Internacional de Patentes:

- G06F9/38 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Clasificación PCT:

- G06F9/38 G06F 9/00 […] › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Fragmento de la descripción:

Dispositivo para la mejora de la seguridad de microprocesadores en sistemas empotrados.

El objeto de la presente invención es un dispositivo y un método para mejorar la seguridad de los microprocesadores en los sistemas empotrados, todo ello basado en una unidad vectorial reconfigurable. La presente invención se encuadra dentro del ámbito de los sistemas empotrados y es especialmente relevante en el campo de las redes de sensores.

Antecedentes de la invención

Diferentes aproximaciones como el Differential Power Analysis (Análisis de potencia diferencia, DPA) y sus variantes, que involucran muchos aspectos del diseño de sistemas, tanto HW (hardware) como SW (software), cifrado entre otros, ofrecen retos adicionales para los proyectos de ingeniería en sistemas empotrados, puesto que los riesgos de seguridad deben manejarse en distintos niveles de abstracción y no deben ser expuestos a niveles superiores. Algunas de las contramedidas propuestas incluyen la utilización de relojes aleatorios con objeto de introducir no-determinismo en el sistema [O. Kömmerling and M. G. Kuhn, "Design principles for tamper-resistant smartcard processors", in Proceedings of the USENIX Workshop on Smartcard Technology, Chicago, 10-11 May, 1999., 1999, pp. 9-20], enmascaramiento de los datos antes de operar con ellos para ocultar la información sensible, ver patente JP2000-66585, US 10/825,291 y US 10/851,123 [Publicado posteriormente en C. H. Gebotys, "A split-mask countermeasure for low-energy secure embedded systems", Trans. on Embedded Computing Sys., vol. 5, no. 3, pp. 577-612, 2006], uso de amplitudes de señal muy reducidas, y la introducción de ruido en las posibles medidas de potencia [T. S. Messerges, E. A. Dabbish, and R. H. Sloan, "Examining smartcard security under the threat of power analysis attacks", IEEE Trans. Comput., vol. 51, no. 5, pp. 541-552, 2002] [P. Kocher, J. Jaffe, and B. Jun, "Differential power analysis", Lecture Notes in Computer Science, vol. 1666, pp. 388-397, 1999]. Todas estas medidas sólo consiguen que sea necesario un mayor número de muestras para descubrir las claves, pero no eliminan el riesgo.

Recientemente [D. Hwang, K. Tiri., A. Hodjat, B.-C. Lai, S. Yang, P. Schaumont, and I. Verbauwhede, "AES-based security coprocessor IC in 0.18-μm CMOS with resistance to differential power analysis side-channel attacks", IEEE Journal:of Solid-State Circuits, vol. 41, no. 4, pp. 781-792, April 2006] se ha propuesto la utilización de un estilo de lógica dinámica denominado wave dynamic differential logic (WDDL) junto con una técnica de rutado denominada rutado diferencial para combatir las técnicas de análisis de potencia diferencial (DPA). Por supuesto, el coste es un aumento significativo del área y el consumo (un orden de magnitud superior) y una pérdida significativa del rendimiento máximo (0,99 Gb/s frente a 3,89 Gb/s de la implementación estándar). La patente US/6654884 describe un método para mantener constante la distancia de Hamming con puertas especiales (lo que implica un mayor coste).

Lo que hace específica esta invención es la utilización de lógica reconfigurable para permitir que el hardware del dispositivo esté cambiando continuamente, lo que dificulta enormemente ataques basados en análisis de consumo o emisiones electromagnéticas. Esto permite que el dispositivo se defienda de estos ataques al mismo tiempo que mejora su rendimiento.

Por otro lado, a diferencia de otras unidades reconfigurables propuestas, la estructura en forma de ruta de datos segmentada hace que las comunicaciones sean muy locales. Al no existir líneas largas con muchas conexiones, las capacidades son menores y el consumo es menor.

Descripción de la invención

Como ha sido mencionado, los ataques a sistemas empotrados más comunes, incluyendo DPA (Differential Power Analysis) y sus variantes, se basan en el análisis estadístico de muchas capturas que pueden filtrar información de la clave (consumo, emisiones electromagnéticas, tiempos de ejecución, etc). Al considerar muchas capturas se elimina la dependencia que puede tener con los datos de entrada. El éxito del ataque se basa en que el dispositivo se comporta de la misma forma para todas esas capturas.

El dispositivo que se describe a continuación varía de forma aleatoria el propio hardware del dispositivo, utilizando la lógica reconfigurable para variar la implementación física de la ruta de datos, lo que determina en cada momento el patrón de consumo emisiones electromagnéticas, y tiempo de ejecución.

El dispositivo reconfigurable y de bajo consumo para la mejora de la seguridad de microprocesadores para sistemas empotrados, de forma básica comprende, al menos:

(a) una primera unidad vectorial reconfigurable diseñada como una ruta de datos segmentada con múltiples contextos configurables independientemente, y que está dividida en tres etapas:

(b) una segunda unidad de carga y almacenamiento vectorial integrada en la unidad de ejecución de la ruta de datos principal configurada para desacoplar la extracción de operandos de las operaciones vectoriales de la primera unidad vectorial reconfigurable de la operación normal de la ruta de datos principal.

Puede pensarse que la variación de la implementación física de la ruta de datos reconfigurable sólo añade algo de ruido a las muestras y por tanto, al igual que ocurre cuando se introducen consumos adicionales aleatorios, sólo obliga a obtener más muestras para atacarlo. Sin embargo, cada bucle puede implementarse de múltiples formas en la unidad reconfigurable, de forma que incluso cambia el patrón de acceso a memoria. Por tanto, no es fácil saber qué dato se está procesando en cada momento. Por otro lado, el cambio de implementación no está sincronizado con el cambio de dato a cifrar, sino que puede producirse en cualquier momento durante la ejecución del bucle.

El problema de la lógica reconfigurable en sistemas empotrados es el elevado consumo que suele tener. Sin embargo, esto se debe en gran medida a las elevadas capacidades asociadas a las líneas largas de interconexión. Para reducir el consumo, la unidad reconfigurable propuesta restringe fuertemente el flujo de datos dentro de la unidad reconfigurable, de forma que las comunicaciones son muy locales y las capacidades mucho más reducidas.

La arquitectura reconfigurable que proponemos para el procesador del sistema empotrado la denominamos SORU (Stream Oriented Reconfigurable Unit o unidad vectorial reconfigurable), y está especialmente diseñada para soportar la auto-adaptación dinámica.

Existe un gran número de diseños de arquitecturas reconfigurables pero, hasta donde sabemos, ninguna es apta para este escenario de cambio constante porque la generación de la configuración de la lógica reconfigurable tiene un coste computacional muy elevado.

La arquitectura vectorial reconfigurable está basada en un procesador RISC de propósito...

Reivindicaciones:

1. Dispositivo para la mejora de la seguridad de microprocesadores en sistemas empotrados de tipo reconfigurable y de bajo consumo para la ejecución de operaciones vectoriales mediante reducción de energía en el procesamiento de datos sensibles haciendo que la comunicación entre etapas sea fija y muy local, evitando así el uso de buses empleando líneas de conexión muy cortas, lo que lleva a minimizar las capacidades y la corriente necesaria para cargarlas, estando este dispositivo caracterizado por comprender, al menos:

(a) una primera unidad vectorial reconfigurable automáticamente en tiempo de ejecución (1) diseñada como una ruta de datos pre-rutada, segmentada, con múltiples contextos configurables independientemente, y que consta de tres etapas:

(b) una segunda unidad de carga y almacenamiento vectorial (2), integrada en la unidad de ejecución. (3) de la ruta de datos principal (100), configurada para desacoplar la extracción de operandos de las operaciones vectoriales de la primera unidad vectorial reconfigurable (1) de la operación normal de la ruta de datos principal (100), y que automatiza la carga de vectores completos desde la memoria principal a los registros del dispositivo sin intervención del procesador principal y de forma independiente a los accesos a memoria de éste.

2. Dispositivo de acuerdo con la reivindicación 1 donde el software de soporte de ejecución es una librería de bajo nivel comprendiendo el código de inicialización.

3. Dispositivo de acuerdo con la reivindicación 1 donde el software de soporte de ejecución es un sistema operativo de tiempo real.

4. Dispositivo de acuerdo con la reivindicación 1 donde se fija una interfaz de la unidad básica reconfigurable independiente de la estructura interna de ésta, comprendida por, al menos, tres entradas de datos, siendo estas tres entradas el resultado de cada unidad reconfigurable previa, un nuevo dato del bloque de registro interno y el último resultado calculado por esa dicha unidad reconfigurable básica; siendo además dicho resultado de una operación en una unidad reconfigurable básica almacenado en un registro, de forma que pueda ser usado por la siguiente unidad reconfigurable básica en el siguiente ciclo de reloj.

Patentes similares o relacionadas:

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]

Aumento de protocolo de coherencia para indicar estado de transacción, del 4 de Diciembre de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método implementado por ordenador para implementar un protocolo de coherencia, comprendiendo el método: enviar , por un procesador (112a) solicitante, […]

Método y aparato para un acceso a memoria basado en hilos en un procesador multihilo, del 11 de Septiembre de 2019, de QUALCOMM INCORPORATED: Método para acceder a una memoria por un procesador multihilo , comprendiendo el método: determinar un identificador de hilo asociado a un […]

Procedimientos y aparatos para predecir la no ejecución de instrucciones de no bifurcación condicional, del 15 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para manejar una instrucción de no bifurcación condicional, que comprende: identificar una instrucción […]

Procesamiento transaccional, del 17 de Abril de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método de controlar la ejecución de una transacción en un entorno informático, comprendiendo el método los pasos de: Iniciar, mediante un procesador, la ejecución […]

Guardar/restablecer registros seleccionados en procesamiento transaccional, del 13 de Marzo de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para facilitar el procesamiento de transacciones dentro de un entorno de computación, comprendiendo dicho método: obtener una instrucción […]