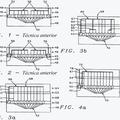

Estructura y procedimiento para una TSV con alivio de tensión.

Una pastilla semiconductora que comprende:

un sustrato (102) que tiene una cara activa;

capas conductoras acopladas a la cara activa;

una vía a través de sustrato (950, 1450) en una cavidad de vía que se extiende a través del sustrato y que tiene un diámetro sustancialmente constante a través de una longitud de la vía a través de sustrato, comprendiendo la vía a través de sustrato un material de relleno conductor;

una primera capa de aislamiento (940, 1440) que rodea la vía a través de sustrato y se proporciona en una pared lateral de la cavidad de vía; y

una segunda capa de aislamiento (970, 1470) que rodea la vía a través de sustrato, la segunda capa de aislamiento formada entre la primera capa de aislamiento y el relleno conductor y que comprende dos partes, una parte rebajada (1172, 1582) y una parte dieléctrica, en la que la parte dieléctrica de la segunda capa de aislamiento se proporciona en la primera capa de aislamiento, y la parte rebajada define un espacio cerca de la cara activa del sustrato y entre la primera capa de aislamiento y el material de relleno conductor, pudiendo el material en el espacio aliviar la tensión del material de relleno conductor.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2013/027729.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE SAN DIEGO, CA 92121-1714 ESTADOS UNIDOS DE AMERICA.

Inventor/es: GU,SHIQUN, RAMACHANDRAN,VIDHYA.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H01L21/768 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 21/00 Procedimientos o aparatos especialmente adaptados para la fabricación o el tratamiento de dispositivos semiconductores o de dispositivos de estado sólido, o bien de sus partes constitutivas. › Fijación de interconexiones que sirvan para conducir la corriente entre componentes separados en el interior de un dispositivo.

- H01L23/48 H01L […] › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › Disposiciones para conducir la corriente eléctrica hacia o desde el cuerpo de estado sólido durante su funcionamiento, p. ej. hilos de conexión o bornes.

PDF original: ES-2817788_T3.pdf

Patentes similares o relacionadas:

Sustrato de pastilla embebida con taladro posterior, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un dispositivo, que comprende: un sustrato que tiene un primer lado y un segundo lado opuesto, en el que el sustrato es un sustrato central que […]

Esquemas de interconexión posterior a la pasivación en la parte superior de los chips IC, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Una estructura de interconexión posterior a la pasivación, que comprende:

uno o más circuitos internos que comprenden uno o más dispositivos activos formados en […]

Esquemas de interconexión posterior a la pasivación en la parte superior de los chips IC, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Una estructura de interconexión posterior a la pasivación, que comprende:

uno o más circuitos internos que comprenden uno o más dispositivos activos formados en […]

Sistema multicapas con elementos de contacto y procedimiento para la creación de un elemento de contacto para un sistema multicapas, del 2 de Mayo de 2018, de INTERPANE ENTWICKLUNGS- UND BERATUNGSGESELLSCHAFT MBH & CO. KG: Sistema de capas con elemento de contacto , que comprende un sustrato , un sistema multicapas dispuesto sobre el sustrato con al menos una capa superior […]

Dispositivo para el posicionamiento y la puesta en contacto de contactos de prueba, del 22 de Noviembre de 2017, de Pac Tech - Packaging Technologies GmbH: Dispositivo para el posicionamiento y la puesta en contacto de contactos de prueba en un soporte de contactos para producir una disposición de contactos […]

Proceso para rellenar surcos de contacto en microelectrónica, del 23 de Agosto de 2017, de MacDermid Enthone Inc: Proceso para metalizar un elemento de surco de contacto a través de silicio en un dispositivo de circuito integrado semiconductor, comprendiendo […]

Procedimiento para formar una imagen conductora sobre una superficie no conductora, del 24 de Junio de 2015, de Earthone Circuit Technologies Corporation: Procedimiento para formar una capa conductora sobre una superficie, que comprende realizar las siguientes etapas en orden: activar por lo […]

Estructura de interconexión basada en nanotubos de carbono redirigidos, del 11 de Febrero de 2015, de COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES: Dispositivo electrónico que comprende conexiones eléctricas que se extienden según al menos dos direcciones distintas, estando dichas conexiones realizadas por medio […]

Control térmico activo para dispositivos de IC apilados, del 11 de Marzo de 2020, de QUALCOMM INCORPORATED: Un dispositivo de IC apilado que comprende: un nivel superior y un nivel inferior , teniendo cada nivel una capa de sustrato y una capa activa en […]