ESTRUCTURA CACHE PARA UN RAPIDO ACCESO A ARCHIVOS GUARDADOS POR SEPARADO.

Proceso para la creación de una estructura caché para un acceso rápido a archivos guardados por separado con un nombre de fichero inequívoco,

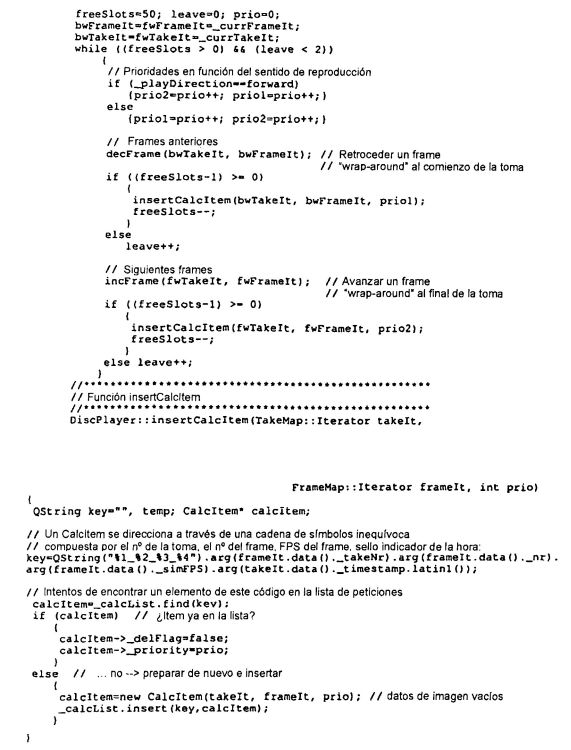

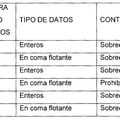

creándose o actualizándose una lista de peticiones al ser pedido uno de esos archivos x y cargándose, una vez creada o actualizada la lista de peticiones, en la memoria principal determinados archivos especificados en dicha lista, caracterizado porque cada elemento de la lista de peticiones contiene los cinco componentes "nombre de fichero", "estado", "prioridad", "indicador en datos de imagen" y "marca de borrado", siguiendo la creación o actualización de la lista de peticiones los siguientes pasos: Posicionamiento de la marca de borrado en VERDADERO para todos los elementos de la lista, creación de nuevos elementos de la lista de peticiones mediante dos iteradores - avanzando uno de éstos un número determinado de pasos a partir del objeto solicitado x y retrocediendo el otro un número determinado de pasos a partir del objeto solicitado x entre los archivos guardados por separado con nombres de fichero inequívocos -, posicionándose la marca de borrado de los nuevos elementos en FALSO, el estado de los nuevos elementos en Solicitado y el indicador de los datos de imagen de los nuevos elementos en Vacío, siempre y cuando los elementos relacionados con los archivos encontrados por los iteradores aún no estén incluidos en la lista bajo esos nombres de fichero, o posicionamiento de la marca de borrado de los elementos ya incluidos en la lista en FALSO si los nombres de fichero de esos elementos son idénticos con los nombres de fichero de los archivos encontrados por los iteradores, a continuación establecimiento de la prioridad de los elementos de la lista de peticiones con la marca de borrado FALSO en función del objeto requerido x, asignándose al objeto x la máxima prioridad, al siguiente la segunda en magnitud, al inmediatamente anterior la tercera en magnitud, etc.; y porque se cargan en la memoria principal aquellos archivos identificados en dicha lista cuyo estado corresponda a Solicitado, consistiendo el proceso de carga en los siguientes pasos: carga de los archivos en la memoria principal en el orden de prioridad que les haya sido asignado mediante los elementos de la lista de peticiones, posicionamiento del indicador relacionado con los datos de imagen de esos elementos cargados en la memoria principal en Datos de imagen válidos, a continuación posicionamiento del estado de esos elementos cargados en la memoria principal en Finalizado y a continuación borrado de aquellos elementos de la lista de peticiones cuya marca de borrado esté puesta en VERDADERO.

Tipo: Resumen de patente/invención.

Solicitante: VANTAGE FILM GMBH.

Nacionalidad solicitante: Alemania.

Dirección: ALTSTRASSE 9,92637 WEIDEN.

Inventor/es: PRELL,BERNHARD.

Fecha de Publicación: .

Fecha Solicitud PCT: 17 de Septiembre de 2004.

Fecha Concesión Europea: 21 de Febrero de 2007.

Clasificación PCT:

- G06F12/12 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Control de remplazamiento.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Patentes similares o relacionadas:

Proporcionar control de asignación de memoria caché compartida en sistemas de memoria caché compartida, del 11 de Diciembre de 2018, de QUALCOMM INCORPORATED: Un controlador de memoria caché de un sistema de memoria caché compartida , que comprende: medios para recibir una solicitud de acceso […]

DISPOSITIVO DE ACELERACION DESDE EL ACCESO A MEMORIA EN UN SISTEMA INFORMATICO., del 16 de Noviembre de 1994, de BULL S.A.: EL INVENTO SE SITUA EN EL CAMPO DE LOS SISTEMAS INFORMATICOS. PARA ACELERAR LOS ACCESOS A MEMORIA, SE UTILIZA UNA MEMORIA RAPIDA DE LECTURA ASOCIATIVA QUE CONTIENE UNOS EXTRACTOS […]

PROCEDIMIENTO Y DISPOSITIVO PARA ACELERAR EL ACCESO A MEMORIA, UTILIZANDO UN ALGORITMO LRU MODIFICADO., del 16 de Noviembre de 1994, de BULL S.A.: EL INVENTO SE SITUA EN EL CAMPO DE LOS SISTEMAS INFORMATICOS. PARA ACELERAR EL ACCESO A MEMORIA, UNA MEMORIA RAPIDA DE LECTURA ASOCIATIVA CONTIENE UNOS EXTRACTOS FORMADOS […]

APARATO Y METODO PARA REEMPLAZAR UNA PAGINA EN UN SISTEMA DE PROCESO DE DATOS QUE TIENE UNA MEMORIA VIRTUAL, del 1 de Mayo de 1994, de BULL HN INFORMATION SYSTEMS INC.: EN UN MULTIPROCESADOR, SISTEMA DE PROCESO DE DATOS MULTIPROGRAMADO QUE EMPLEA DIRECCIONES, APARATO Y METODO VIRTUALES, ESTA PREVISTO PARA SELECCIONAR […]

SISTEMA DE PROCESAMIENTO DE ERRORES PARA UN DEPOSITO DE MEMORIA DE TIPO BUFFER., del 16 de Junio de 1983, de FUJITSU LIMITED: SISTEMA DE PROCESAMIENTO DE ERRORES PARA UN DEPOSITO DE MEMORIA DE TIPO BUFFER. COMPRENDE: MEDIOS DETECTORES DE ERROR PARESTADO, EN QUE LOS MEDIOS DESIGNADORES […]

PROCEDIMIENTO Y MECANISMOS PARA UNA GESTIÓN PROACTIVA DE LA MEMORIA, del 2 de Enero de 2012, de MICROSOFT CORPORATION: Un sistema en un entorno informático que comprende: un mecanismo de seguimiento que hace seguimiento de la utilización de páginas de memoria […]

METODOS Y APARATOS PARA CONTROLAR UNA MEMORIA CACHE, del 16 de Abril de 2009, de SONY COMPUTER ENTERTAINMENT INC.: Un método para controlar una memoria caché (110, 110A), que comprende los pasos de: recibir una dirección para al menos una entre […]

METODOS Y APARATOS PARA CONTROLAR UNA MEMORIA CACHE, del 16 de Abril de 2009, de SONY COMPUTER ENTERTAINMENT INC.: Un método para controlar una memoria caché (110, 110A), que comprende los pasos de: recibir una dirección para al menos una entre […]

DISPOSITIVO DE CALCULO DE PAGINACION EN TIEMPO REAL Y METODO DE OPERACION, del 1 de Marzo de 2009, de SYMBIAN SOFTWARE LIMITED: Un método para proporcionar actuación en tiempo real con paginación de la memoria en un dispositivo de cálculo, comprendiendo el método capacitar […]

DISPOSITIVO DE CALCULO DE PAGINACION EN TIEMPO REAL Y METODO DE OPERACION, del 1 de Marzo de 2009, de SYMBIAN SOFTWARE LIMITED: Un método para proporcionar actuación en tiempo real con paginación de la memoria en un dispositivo de cálculo, comprendiendo el método capacitar […]