Intercalador de bits para un sistema de BICM con códigos QC LDPC.

Un método de intercalación de bits para intercalar una palabra de código generada mediante una codificación de comprobación de paridad de baja densidad cuasi cíclica,

QC LDPC, que emplea Q × Q matrices circulantes, incluyendo codificación QC LDPC de repetir-acumular, comprendiendo el método de intercalación de bits:

una etapa de permutación de bits para aplicar un proceso de permutación de bits a la palabra de código para redisponer bits de palabra de código, estando compuesta la palabra de código de N bloques cíclicos consistiendo cada uno en Q bits de bloques cíclicos; y

una etapa de división para dividir la palabra de código, después del proceso de permutación de bits, en una pluralidad de palabras de constelación, estando compuesta cada una de las palabras de constelación de M bits, en donde

F es un entero mayor de 1 y es un divisor de M y de Q,

N no es un múltiplo de M/F,

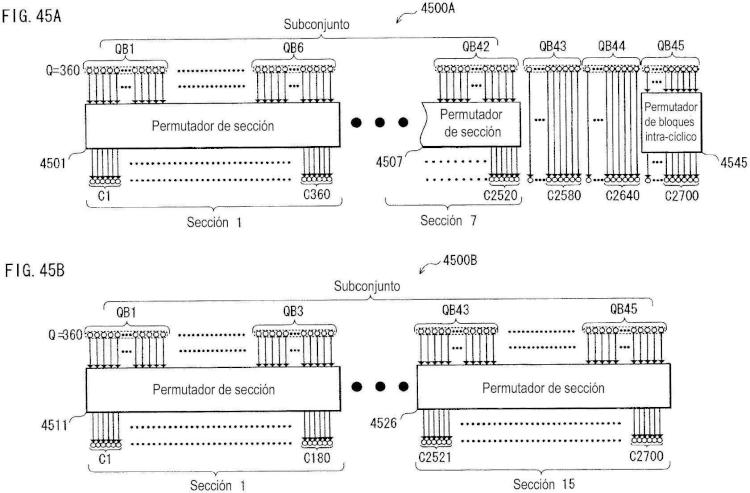

N' es igual a (M/F)×floor(N/(M/F)),

antes del proceso de permutación de bits, se dividen N' bloques cíclicos entre los N bloques cíclicos en F×N'/M secciones de repliegue, consistiendo cada una de las secciones de repliegue en M/F de los bloques cíclicos, y en la etapa de permutación de bits, para cada sección de repliegue, el proceso de permutación de bits se aplica a los Q×(M/F) bits de una sección de repliegue dada de manera que M bits, incluyendo F bits de bloques cíclicos de cada uno de los M/F bloques cíclicos diferentes, se asignan a una de las Q/F palabras de constelación asociadas a la sección de repliegue dada.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/JP2012/003272.

Solicitante: PANASONIC CORPORATION.

Nacionalidad solicitante: Japón.

Dirección: 1006 Oaza Kadoma Kadoma-shi, Osaka 571-8501 JAPON.

Inventor/es: PETROV,MIHAIL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M13/11 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › usando bits de paridad múltiple.

- H03M13/25 H03M 13/00 […] › Detección de errores o corrección de errores transmitidos por codificación espacial de la señal, es decir, añadiendo redundancia en la constelación de la señal, p. ej. modulación codificada de Trellis [TCM].

- H03M13/27 H03M 13/00 […] › usando técnicas de entrelazado.

- H03M13/29 H03M 13/00 […] › combinando dos o más códigos o estructuras de códigos, p. ej. códigos de productos, códigos de producto generalizados, códigos concatenados, códigos internos y externos.

- H03M13/35 H03M 13/00 […] › Protección desigual o adaptativa contra los errores, p. ej. proporcionando un nivel diferente de protección según la importancia de la información de origen o adaptando la codificación según la variación de las características del canal de transmisión.

- H04L1/00 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › Disposiciones para detectar o evitar errores en la información recibida.

- H04L1/06 H04L […] › H04L 1/00 Disposiciones para detectar o evitar errores en la información recibida. › utilizando diversidad de espacio.

PDF original: ES-2546912_T3.pdf

Fragmento de la descripción:

Intercalador de bits para un sistema de BICM con códigos QC LDPC

La presente divulgación se refiere al campo de comunicaciones digitales, y más específicamente a un intercalador de bits para un sistema de codificación y modulación de bits intercalados con códigos de comprobación de paridad de baja densidad cuasi cíclicos.

En los últimos años, los sistemas de codificación y modulación de bits intercalados (en lo sucesivo, BICM) se han usado en el campo de las comunicaciones digitales (véase, por ejemplo, la norma DVB-T2 ETSI EN 302 755 V1.2.1) .

Los sistemas de BICM generalmente incorporan las siguientes tres etapas.

(1) Codificar bloques de datos en palabras de código usando, por ejemplo, códigos de comprobación de paridad de baja densidad cuasi cíclicos (en lo sucesivo, QC LDPC) o similares.

(2) Realizar intercalación de bits en los bits de cada palabra de código.

(3) Dividir cada palabra de código intercalada de bits en palabras de constelación que tienen un número de bits de constelación, y mapear las palabras de constelación en constelaciones.

Normalmente, es deseable la eficacia en la intercalación aplicada a las palabras de código de los códigos de comprobación de paridad de baja densidad cuasi cíclicos.

El artículo "Macro Interleaver Design for Bit Interleaved Coded Modulation with Low-Density Parity-Check Codes" por Frank Kienle y Norbert Wehn (Vehicular Technology Conference, 2008. VTC Spring 2008. IEEE, Piscataway, NJ, Estados Unidos) desvela un intercalador diseñado para modulación codificada intercalada de bits con códigos de comprobación de paridad de baja densidad.

El artículo "Performance of belief propagation coded modulation with iterative decoding" por Hua Rui, XiaoFei Zhang, y DaZhuan Xu (International Conference on Communications, Circuits and Systems, ICCCAS 2004, Chengdu, China 27-29 de junio de 2004, IEEE, Piscataway, NJ, Estados Unidos) se refiere a modulación codificada de bits intercalados con decodificación iterativa para transmisión eficaz de ancho de banda a través del canal de desvanecimiento de Rayleigh y desvela un esquema iterativo concatenado en serie (BPCM-ID) que combina códigos de comprobación de paridad de baja densidad (LDPC) con modulación multinivel.

La referencia WO 2010-024914 (A1) desvela un método para reusar códigos de comprobación de paridad de baja densidad (LDPC) de difusión de vídeo digital por satélite de la segunda generación (DVB-S2) , y por lo tanto también hardware de DVB-S2, en difusión de vídeo digital para contextos de cable de la segunda generación (DVB-C2) . Los códigos de LDPC son susceptibles a un error umbral, más allá del que la información codificada no puede recuperarse con precisión. Coincidiendo los niveles variables de protección en una palabra de código de LDPC con los niveles variables de protección en modulación de amplitud en cuadratura, el número de errores puede mantenerse por debajo del error umbral.

La presente divulgación tiene por objetivo proporcionar un método de intercalación de bits que posibilita que se aplique intercalación eficaz a las palabras de código de códigos de comprobación de paridad de baja densidad cuasi cíclicos, así como un intercalador de bits correspondiente, un método de decodificación y un decodificador.

Esto se consigue mediante las características de las reivindicaciones independientes. Las realizaciones preferidas son la materia objeto de las reivindicaciones dependientes.

El alcance de la presente invención se define únicamente mediante las reivindicaciones adjuntas. Se proporcionan las realizaciones con F=1 o con N siendo un múltiplo de M/F para fines ilustrativos únicamente y no son parte de la invención reivindicada.

El método de intercalación de bits de la presente invención posibilita que se aplique intercalación eficaz a las palabras de código de los códigos de comprobación de paridad de baja densidad cuasi cíclicos.

[Breve descripción de los dibujos]

La Figura 1 es un diagrama de bloques que muestra la configuración de un transmisor que incluye un codificador de BICM típico. La Figura 2 ilustra un ejemplo de una matriz de comprobación de paridad para códigos de comprobación de paridad de baja densidad cuasi cíclicos que tienen una tasa de codificación de 1/2. La Figura 3 ilustra un ejemplo de una matriz de comprobación de paridad para códigos de comprobación de paridad de baja densidad cuasi cíclicos de repetir-acumular que tienen una tasa de codificación de 2/3. La Figura 4 ilustra una matriz de comprobación de paridad para los códigos de comprobación de paridad de baja

densidad cuasi cíclicos de repetir-acumular de la Figura 3 después de una permutación de fila. La Figura 5 ilustra una matriz de comprobación de paridad para los códigos de comprobación de paridad de baja densidad cuasi cíclicos de repetir-acumular de la Figura 3 después de una permutación de fila y una permutación de paridad. La Figura 6 describe diferentes niveles de robustez de los bits codificados en ocho símbolos de PAM. La Figura 7 es un diagrama de bloques que muestra la configuración de un intercalador de bits típico donde el factor cíclico Q es 8, el número de bloques cíclicos por palabra de código de comprobación de paridad de baja densidad N es 12 y el número de bits por constelación M es 4. La Figura 8A es un diagrama de bloques que muestra la configuración de un modulador de DVB-T2 usado en la norma DVB-T2 y la Figura 8B es un diagrama de bloques que muestra la configuración de un codificador de BICM para el modulador de DVB-T2 de la Figura 8A. La Figura 9A ilustra un proceso de escritura para los bits de una palabra de código de 16 K (es decir, un código de LDPC donde la longitud de la palabra de código de LDPC es 16200 bits) según se realiza mediante un intercalador de comuna-fila que tiene doce columnas, y la Figura 9B ilustra un proceso de lectura para los bits de la palabra de código escritos de la manera indicada mediante la Figura 9A según se realiza mediante el intercalador de columna-fila. La Figura 10A ilustra un proceso de escritura para los bits de una palabra de código de 16 K según se realiza mediante un intercalador de columna-fila que tiene ocho columnas, y la Figura 10B ilustra un proceso de lectura para los bits de la palabra de código escritos de la manera indicada mediante la Figura 10A según se realiza mediante el intercalador de columna-fila. La Figura 11 es un diagrama de bloques que muestra la configuración de un demultiplexor de bit a celda usado para códigos de 16 K de 16-QAM en la norma de DVB-T2. La Figura 12 es un diagrama de bloques que muestra la configuración de un demultiplexor de bit a celda usado para códigos de 16 K de 64-QAM en la norma de DVB-T2. La Figura 13 es un diagrama de bloques que muestra la configuración de un demultiplexor de bit a celda usado para códigos de 16 K de 256-QAM en la norma de DVB-T2. La Figura 14 ilustra un problema que aparece para los códigos de 16 K con un intercalador de bits de DVB-T2 de ocho columnas. La Figura 15 ilustra un problema que aparece para los códigos de 16 K con un intercalador de bits de DVB-T2 de doce columnas. La Figura 16 ilustra un problema que aparece para los códigos de 16 K con un intercalador de bits de DVB-T2 de ocho columnas cuando se aplica giro de columna. La Figura 17 ilustra un problema que aparece para los códigos de 16 K con un intercalador de bits de DVB-T2 de doce columnas cuando se aplica giro de columna. Las Figuras 18A y 18B ilustran respectivamente una primera y segunda condiciones descubiertas por los inventores que posibilitan que se proporcione un intercalador extremadamente eficaz. La Figura 19 ilustra una función de mapeo mediante un intercalador que pertenece a una realización. La Figura 20 es un diagrama de bloques que muestra la configuración de un intercalador que pertenece a una realización. La Figura 21A es un diagrama de bloques que muestra la configuración de un permutador de sección que realiza la permutación de sección ilustrada en la Figura 20, y la Figura 21B ilustra una función de mapeo del permutador de sección mostrado en la Figura 21A. La Figura 22A es un diagrama de bloques que muestra una configuración alternativa de un permutador de sección que realiza la permutación de sección ilustrada en la Figura 20, y la Figura 22B ilustra una función de mapeo del permutador de sección mostrado en la Figura 22A. La Figura 23 es un diagrama de bloques que muestra la configuración de un intercalador que pertenece a otra realización. La Figura 24 es un diagrama de bloques que muestra la configuración del intercalador de bits mostrado en la Figura 23. La Figura 25 es un diagrama de bloques que muestra la configuración de un... [Seguir leyendo]

Reivindicaciones:

1. Un método de intercalación de bits para intercalar una palabra de código generada mediante una codificación de comprobación de paridad de baja densidad cuasi cíclica, QC LDPC, que emplea Q × Q matrices circulantes, incluyendo codificación QC LDPC de repetir-acumular, comprendiendo el método de intercalación de bits:

una etapa de permutación de bits para aplicar un proceso de permutación de bits a la palabra de código para redisponer bits de palabra de código, estando compuesta la palabra de código de N bloques cíclicos consistiendo cada uno en Q bits de bloques cíclicos; y una etapa de división para dividir la palabra de código, después del proceso de permutación de bits, en una pluralidad de palabras de constelación, estando compuesta cada una de las palabras de constelación de M bits, en donde F es un entero mayor de 1 y es un divisor de M y de Q, N no es un múltiplo de M/F, N es igual a (M/F) ×floor (N/ (M/F) ) , antes del proceso de permutación de bits, se dividen N bloques cíclicos entre los N bloques cíclicos en F×N/M secciones de repliegue, consistiendo cada una de las secciones de repliegue en M/F de los bloques cíclicos, y en la etapa de permutación de bits, para cada sección de repliegue, el proceso de permutación de bits se aplica a los Q× (M/F) bits de una sección de repliegue dada de manera que M bits, incluyendo F bits de bloques cíclicos de cada uno de los M/F bloques cíclicos diferentes, se asignan a una de las Q/F palabras de constelación asociadas a la sección de repliegue dada.

2. El método de intercalación de bits de la reivindicación 1, en el que la etapa de permutación de bits incluye adicionalmente aplicar un proceso de redisposición a un subconjunto de, o a la totalidad de, Q× (N-N) bits de bloques cíclicos, entre los Q×N bits de los N bloques cíclicos, que se excluyen de las secciones de repliegue.

3. El método de intercalación de bits de la reivindicación 1, en el que no se aplica un proceso de redisposición a Q× (N-N) bits de bloques cíclicos, entre los Q×N bits de los N bloques cíclicos, que se excluyen de las secciones de repliegue.

4. Un intercalador de bits (2000B) J para intercalar una palabra de código generada mediante codificación de comprobación de paridad de baja densidad cuasi cíclica, QC LDPC, que emplea Q × Q matrices circulantes, incluyendo codificación QC LDPC de repetir-acumular, comprendiendo el intercalador de bits:

una permutación de bits (2010A) para aplicar un proceso de permutación de bits a la palabra de código, para redisponer bits de la palabra de código, estando compuesta la palabra de código de N bloques cíclicos consistiendo cada uno en Q bits de bloques cíclicos, y emitir la palabra de código, después del proceso de permutación de bits, para división en una pluralidad de palabras de constelación, estando compuesta cada una de las palabras de constelación de M bits, en donde F es un entero mayor de 1, y es un divisor de M y de Q, N no es un múltiplo de M/F, N es igual a (M/F) ×floor (N/ (M/F) ) , antes del proceso de permutación de bits, N bloques cíclicos entre los N bloques cíclicos se dividen en F×N/M secciones de repliegue, incluyendo cada una de las secciones de repliegue M/F de los bloques cíclicos, y el proceso de permutación de bits se aplica, para cada sección de repliegue, a los Q× (M/F) bits de una sección de repliegue dada de manera que M bits, incluyendo F bits de bloques cíclicos de cada uno de los M/F bloques cíclicos diferentes, se asignan a una de las Q/F palabras de constelación asociadas a la sección de repliegue dada.

5. Un método para recibir una palabra de código generada mediante codificación de comprobación de paridad de baja densidad cuasi cíclica, QC LDPC, que emplea Q × Q matrices circulantes, incluyendo codificación QC LDPC de repetir-acumular, estando compuesta la palabra de código de N bloques cíclicos consistiendo cada uno en Q bits de bloques cíclicos, comprendiendo dicho método:

una etapa de demodulación para generar una señal demodulada demodulando una señal transmitida modulando M bits asignados a cada una de una pluralidad de palabras de constelación usando el método de intercalación de bits de la reivindicación 1; y una etapa de decodificación para realizar, en la señal demodulada, un proceso de inversión que cancela la permutación de bits de la reivindicación 1 y realizar un proceso de decodificación de LDPC, generando por lo tanto datos originales de acuerdo con la codificación QC LDPC.

6. Un aparato para recibir (2700A, 2800A) una palabra de código generada mediante codificación de comprobación de paridad de baja densidad cuasi cíclica, QC LDPC, que emplea Q × Q matrices circulantes, incluyendo codificación QC LDPC de repetir-acumular, estando compuesta la palabra de código de N bloques cíclicos consistiendo cada uno

en Q bits de bloques cíclicos, comprendiendo dicho aparato:

una unidad de demodulación (2710) para generar una señal demodulada demodulando una señal transmitida modulando M bits asignados a cada una de una pluralidad de palabras de constelación usando el intercalador de bits de la reivindicación 4; y una unidad de decodificación (2720, 2730A, 2740) para realizar, en la señal demodulada, un proceso de inversión que cancela la permutación de bits del intercalador de bits de la reivindicación 4, y realizar un proceso de decodificación de LDPC, generando por lo tanto datos originales de acuerdo con la codificación QC LDPC.

Patentes similares o relacionadas:

Procedimiento y aparato para inserción de índice de bloque de código en un sistema celular de comunicación inalámbrica, del 29 de Julio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un procedimiento de un terminal en un sistema de comunicación inalámbrica, comprendiendo el procedimiento: recibir, de una estación base, un bloque de información maestra, […]

Aparato de comunicación inalámbrica y procedimiento de generación de señales de referencia, del 29 de Julio de 2020, de Sun Patent Trust: Un aparato de comunicación para una estación base que comprende: un transmisor, el cual, en operación, transmite, a un terminal, información […]

Información de control en un sistema de comunicación inalámbrica, del 15 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para enviar datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar conformación de haces […]

Detección y comprobación de error de señalización de retroalimentación en sistemas de comunicación inalámbrica de MIMO, del 15 de Julio de 2020, de INTERDIGITAL TECHNOLOGY CORPORATION: Un método implementado en una unidad de transmisión recepción inalámbrica, WTRU, caracterizado por que el método comprende: proporcionar una pluralidad […]

Repetición de transmisiones de señales en sistemas de comunicación, del 15 de Julio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un procedimiento para que un equipo de usuario, UE, transmita una señal de acuse de recibo en un sistema de comunicación, comprendiendo el procedimiento: transmitir la señal […]

Método y dispositivo de codificación, del 15 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación, que comprende: realizar (S101), mediante un extremo de transmisión basado en un polinomio de verificación de redundancia cíclica, […]

Método y aparato para determinar el tamaño de bloque de transporte, del 1 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método para determinar un tamaño de bloque de transporte, que comprende: recibir (S24), mediante un dispositivo de terminal, información de control enviada […]

Tramas Wi-Fi que incluyen extensiones de trama, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: generar una trama para transmitir datos a uno o más nodos inalámbricos; […]