Modulación codificada de LDPC en combinación con 256QAM.

Un método de procesamiento de transmisión que comprende:

una etapa de codificación para codificar bits de información en una palabra de código de acuerdo con un código de comprobación de paridad de baja densidad con tasa de código de 7/15 y una longitud de palabra de código de 16200,

el código de comprobación de paridad de baja densidad se muestra en la Tabla 1-1:

una etapa de intercalación de bits para realizar intercalación de paridad e intercalación de columnas-filas en bits de la palabra de código obtenida en la etapa de codificación, realizándose la intercalación de columnas-filas con o sin giro;

una etapa de demultiplexación de bit-a-celda para demultiplexar una secuencia de bits intercalados en la etapa de intercalación de bits en 8 secuencias de bits Vi,j, donde i indica una de las ocho secuencias y el bit vi,j corresponde al bit vi+8xj de dicha secuencia de bits intercalados y realizar una permutación en las 8 secuencias de bits de acuerdo con una regla de permutación predeterminada para permutar cada conjunto de 8 bits (v0,q, v1,q, v2,q, v3,q, v4,q, v5,q, v6,q, v7,q) a un conjunto de 8 bits (b0,q, b1,q, b2,q, b3,q, b4,q, b5,q, b6,q, b7,q) para obtener 8 secuencias de bits permutados, donde q es un índice;

una etapa de mapeo para mapear cada una de las palabras de celda de 8 bits (y0,q, y1,q, y2,q, y3,q, y4,q, y5,q, y6,q, y7,q) cada una compuesta de un conjunto de 8 bits (b0,q, b1,q, b2,q, b3,q, b4,q, b5,q, b6,q, b7,q) de las 8 secuencias de bits permutados obtenidos en la etapa de demultiplexación de bit-a-celda, en una celda compleja (Re(Zq), Im(Zq)) de acuerdo con la constelación 256QAM (Modulación de Amplitud en Cuadratura) mostrada en las Tablas 1-2 y 1-3:

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/JP2012/003889.

Solicitante: PANASONIC CORPORATION.

Nacionalidad solicitante: Japón.

Dirección: 1006, OAZA KADOMA, KADOMA-SHI OSAKA 571-8501 JAPON.

Inventor/es: PETROV,MIHAIL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M13/19 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › Corrección de un sólo error sin usar propiedades particulares de los códigos cíclicos, p. ej. códigos Hamming, códigos Hamming extendidos o generalizados.

PDF original: ES-2500056_T3.pdf

Fragmento de la descripción:

Modulación codificada de LDPC en combinación con 256QAM

[Campo técnico]

La presente invención se refiere a un método para procesar una señal digital en un lado de transmisión, y en particular a patrones de permutación de bits aplicados a bits antes de introducirse al mapeador. Adicionalmente, la presente invención se refiere a un método para procesar una señal digital en un lado de recepción, y en particular a patrones de permutación de bits aplicados a bits después de emitirse mediante el desmapeador. Adicionalmente, la presente invención se refiere a un transmisor y un receptor para realizar los métodos.

[Técnica anterior]

En los últimos años, los transmisores se proporcionan con un codificador de codificación y modulación de intercalado de bits (BICM) (véase, por ejemplo, bibliografía distinta de patente 1) .

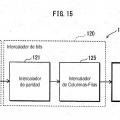

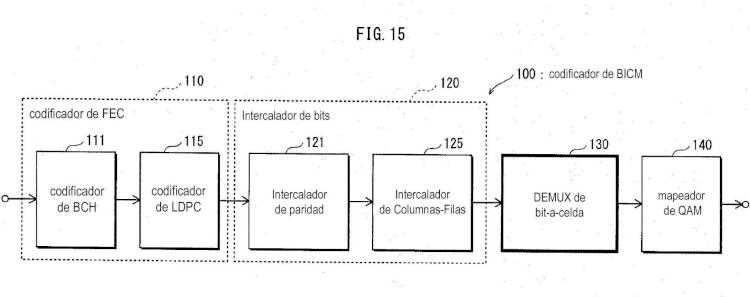

Un codificador de BICM, por ejemplo, realiza las siguientes etapas.

(1) Codificar bloques de datos, por ejemplo, usando un código de BCH (Bose-Chaudhuri-Hocquenghem) como un código exterior y un código de Comprobación de Paridad de Baja Densidad (LDPC) como un código interior.

(2) Aplicar intercalación de bits, que implica intercalación de paridad e intercalación de columnas-filas, a los bits

de palabra de código obtenidos como resultado de la codificación. 25

(3) Demultiplexar la palabra de código de intercalado de bits para obtener palabras de celda. La demultiplexación incluye el procesamiento equivalente a una permutación de las columnas de una matriz de intercalador usada en la intercalación de columnas-filas cuando el tipo de modulación que se está usando es, por ejemplo, 16QAM, 64QAM o 256QAM.

(4) Mapear las palabras de celda en constelaciones.

[Lista de citas]

[Bibliografía distinta de patente]

[Bibliografía distinta de patente 1] ETSI EN 302 755 V1.2.1 (norma DVB-T2) [Bibliografía distinta de patente 2] “New 16k LDPC codes for NGH” por Makiko Kan, con nombre de fichero: “TMNGH580_NGH_sony_New_16k_Codes.pdf’, ID de documento TM-H1115 y publicado en [Bibliografía distinta de patente 3] ETSI EN 302 307 V1.2.1 (norma DVB-T2)

Organización DVB: “TM-NGH643_20110120_sony_New_16k_codes2.pdf”, desvela diferentes códigos de LDPC.

El documento WO 2009 109830 A1 se refiere a métodos para procesamiento de señal digital y a sistemas de transmisión/recepción que utilizan dichos métodos; está basado en el uso de códigos de LDPC, en particular el código de LDPC con una tasa de código de 3/5, en combinación con una modulación 16QAM o 64QAM o 256QAM.

[Sumario de la invención]

[Problema técnico]

El rendimiento de recepción de un receptor puede mejorarse optimizando apropiadamente las reglas de permutaciones (incluyendo la intercalación de bits con número (2) anterior y la permutación llevada a cabo en la demultiplexación con número (3) anterior) aplicadas a los bits de palabras de código de LDPC antes de mapearse para ser adecuados para el código de LDPC y la constelación usada mediante el transmisor y el receptor.

La presente invención tiene por objeto proporcionar un método de procesamiento de transmisión y un método de procesamiento de recepción de acuerdo con que las reglas de permutación aplicadas a los bits de palabras de código de LDPC antes de mapearse se optimizan para los códigos y constelaciones de LDPC usados por el transmisor y el receptor, mejorando de esta manera el rendimiento de recepción del receptor. La presente invención tiene por objeto también proporcionar un transmisor y un receptor que ejecuten el método de procesamiento de 65 transmisión y el método de procesamiento de recepción, respectivamente.

[Solución al problema]

Para conseguir los objetivos anteriores, se especifica un método de procesamiento de transmisión de acuerdo con la presente invención en la reivindicación independiente 1. 5 [Sumario de la invención]

De acuerdo con el método de procesamiento de transmisión de la reivindicación 1, las reglas de permutación a aplicarse a los bits de palabras de código de LDPC antes de mapearse se optimizan para los códigos y constelaciones de LDPC usados por el transmisor y el receptor, que es ventajoso para mejorar el rendimiento de recepción del receptor.

[Breve descripción de los dibujos]

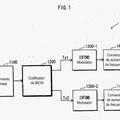

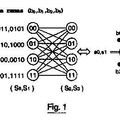

La Figura 1 es una vista general de un modulador de DVB-T2. La Figura 2 es un diagrama de bloques del codificador de BICM mostrado en la Figura 1. La Figura 3 muestra una palabra de código de LDPC, compuesta de una trama de banda base, parte de paridad de BCH y parte de paridad de LDPC. La Figura 4 ilustra el principio de trabajo del intercalador de columnas-filas con giro, llevado a cabo mediante el intercalador de columnas-filas mostrado en la Figura 2. La Figura 5A ilustra un proceso de escritura realizado mediante un intercalador de columnas-filas que tiene 8 columnas para escribir bits de una palabra de código de LDPC con una longitud de palabra de código de 16200 bits, y la Figura 5B ilustra un proceso de lectura realizado mediante el intercalador de columnas-filas para leer los bits de la palabra de código de LDPC escritos en el proceso ilustrado en la Figura 5A.

La Figura 6A ilustra un proceso de escritura realizado mediante un intercalador de columnas-filas que tiene 12 columnas para escribir bits de una palabra de código de LDPC con una longitud de palabra de código de 16200 bits, y la Figura 6B ilustra un proceso de lectura realizado mediante el intercalador de columnas-filas para leer los bits de la palabra de código de LDPC escritos en el proceso ilustrado en la Figura 6A. La Figura 7 ilustra la entrada y la salida del demultiplexor de bit-a-celda mostrado en la Figura 2. La Figura 8 es un diagrama de bloques de un demultiplexor de bit-a-celda para la constelación 16QAM. La Figura 9 es un diagrama de bloques de un demultiplexor de bit-a-celda para la constelación 64QAM. La Figura 10 es un diagrama de bloques de un demultiplexor de bit-a-celda para la constelación 256QAM. La Figura 11 muestra un mapeo de constelación particular para QPSK aplicable en DVB-T2 para transmisión y recepción de datos.

La Figura 12 muestra un mapeo de constelación particular para 16QAM aplicable en DVB-T2 para transmisión y recepción de datos. La Figura 13 muestra un mapeo de constelación particular para 64QAM aplicable en DVB-T2 para transmisión y recepción de datos. La Figura 14 muestra un mapeo de constelación particular para 256QAM aplicable en DVB-T2 para transmisión y recepción de datos. La Figura 15 es un diagrama de bloques de un codificador de BICM de acuerdo con una realización de la presente invención. La Figura 16 ilustra la entrada y la salida del demultiplexor de bit-a-celda mostrado en la Figura 15. La Figura 17 es un diagrama de bloques de un demultiplexor de bit-a-celda para la constelación 16QAM.

La Figura 18 es un diagrama de bloques de un demultiplexor de bit-a-celda para la constelación 64QAM. La Figura 19 es un diagrama de bloques de un demultiplexor de bit-a-celda para la constelación 256QAM. La Figura 20 es un diagrama de bloques de un decodificador de BICM de acuerdo con una realización de la presente invención. La Figura 21 ilustra la entrada y la salida del multiplexor de celda-a-bit mostrado en la Figura 20. La Figura 22 es un diagrama de bloques de un multiplexor de celda-a-bit para la constelación 16QAM. La Figura 23 es un diagrama de bloques de un multiplexor de celda-a-bit para la constelación 64QAM. La Figura 24 es un diagrama de bloques de un multiplexor de celda-a-bit para la constelación 256QAM. La Figura 25 muestra el código de LDPC para una longitud de palabra de código de 16200 bits y tasa de código de 7/15.

La Figura 26 muestra el código de LDPC para una longitud de palabra de código de 16200 bits y tasa de código de 8/15.

[Descripción de las realizaciones]

"Hallazgos por el presente inventor que conducen a la invención"

DBV-T2 (Difusión de Vídeo Digital -Terrestre de Segunda Generación) (ETSI EN 302 755: bibliografía distinta de patente 1) es la mejora de la DVB-T, que es la norma para televisión, y describe un sistema de transmisión de línea de base de segunda generación para televisión digital terrestre. Más específicamente, ETSI EN 302 755 (bibliografía 65 distinta de patente 1) describe los detalles del sistema de codificación/modulación de canal pretendido para servicios de televisión digital y flujos de datos genéricos.

La Figura 1 es una vista general de un modulador de DVB-T2 conforme con la arquitectura de sistema de la DVB-T2 (concepto de diseño fundamental) . El modulador 1000 de DVB-T2 incluye... [Seguir leyendo]

Reivindicaciones:

1. Un método de procesamiento de transmisión que comprende:

una etapa de codificación para codificar bits de información en una palabra de código de acuerdo con un código de comprobación de paridad de baja densidad con tasa de código de 7/15 y una longitud de palabra de código de 16200, el código de comprobación de paridad de baja densidad se muestra en la Tabla 1-1:

una etapa de intercalación de bits para realizar intercalación de paridad e intercalación de columnas-filas en bits de la palabra de código obtenida en la etapa de codificación, realizándose la intercalación de columnas-filas con o sin giro; una etapa de demultiplexación de bit-a-celda para demultiplexar una secuencia de bits intercalados en la etapa

de intercalación de bits en 8 secuencias de bits Vi, j, donde i indica una de las ocho secuencias y el bit vi, j corresponde al bit vi+8xj de dicha secuencia de bits intercalados y realizar una permutación en las 8 secuencias de bits de acuerdo con una regla de permutación predeterminada para permutar cada conjunto de 8 bits (v0, q, v1, q, v2, q, v3, q, v4, q, v5, q, v6, q, v7, q) a un conjunto de 8 bits (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) para obtener 8 secuencias de bits permutados, donde q es un índice;

una etapa de mapeo para mapear cada una de las palabras de celda de 8 bits (y0, q, y1, q, y2, q, y3, q, y4, q, y5, q, y6, q, y7, q) cada una compuesta de un conjunto de 8 bits (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) de las 8 secuencias de bits permutados obtenidos en la etapa de demultiplexación de bit-a-celda, en una celda compleja (Re (Zq) , Im (Zq) ) de acuerdo con la constelación 256QAM (Modulación de Amplitud en Cuadratura) mostrada en las Tablas 1-2 y 1-3:

[Tabla 1-2]

y0, q y2, q y4, q y6, q 1 0 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1 0 1 1 1 0 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0 0

Re (zq) -15 -13 -11 -9 -7 -5 -3 -1 1 3 5 7 9 11 13 15

[Tabla 1-3]

y1, q y3, q y5, q y7, q 1 0 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1 0 1 1 0 0 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0 0

Im (zq) -15 -13 -11 -9 -7 -5 -3 -1 1 3 5 7 9 11 13 15

donde (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) = (y0, q, y1, q, y2, q, y3, q, y4, q, y5, q, y6, q, y7, q) , y 5 la regla de permutación predeterminada es:

v0, q = b2, q, v1, q = b6, q, v2, q = b0, q, v3, q = b1, q, v4, q = b4, q, v5, q = b5, q, v6, q = b3, q, v7, q = b7, q.

2. Un transmisor (100) que comprende:

un codificador (110) adaptado para codificar bits de información en una palabra de código de acuerdo con un código de comprobación de paridad de baja densidad con tasa de código de 7/15 y una longitud de palabra de código de 16200, el código de comprobación de paridad de baja densidad se muestra en la Tabla 2-1:

un intercalador (120) de bits adaptado para realizar intercalación de paridad e intercalación de columnas-filas en bits de la palabra de código obtenida mediante el codificador, realizándose la intercalación de columnas-filas con o sin giro; un demultiplexor (130) adaptado para demultiplexar una secuencia de bits intercalados mediante el intercalador de bits en 8 secuencias de bits Vi, j, donde i indica una de las ocho secuencias y el bit vi, j corresponde al bit vi+8xj de dicha secuencia de bits intercalados y realizar una permutación en las 8 secuencias de bits de acuerdo con una regla de permutación predeterminada para permutar cada conjunto de 8 bits (v0, q, v1, q, v2, q, v3, q, v4, q, v5, q, v6, q,

v7, q) a un conjunto de 8 bits (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) para obtener 8 secuencias de bits permutados, donde q es un índice; un mapeador (140) adaptado para mapear cada una de las palabras de celda de 8 bits (y0, q, y1, q, y2, q, y3, q, y4, q, y5, q, y6, q, y7, q) cada una compuesta de un conjunto de 8 bits (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) de las 8 secuencias de bits permutados obtenidos mediante el demultiplexor de bit-a-celda, en una celda compleja (Re (Zq) , Im (Zq) ) de acuerdo con la constelación 256QAM (Modulación de Amplitud en Cuadratura) mostrada en las Tablas 2-2 y 2-3:

[Tabla 2-2]

y0, q y2, q y4, q y6, q 1 0 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1 0 1 1 1 0 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 1 0 1 0 0 0 1 1 0 0 0 1 0 0 0 0

Re (zq) -15 -13 -11 -9 -7 -5 -3 -1 1 3 5 7 9 11 13 15

[Tabla 2-3]

y1, q y3, q y6, q y7, q 1 0 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1 0 1 1 1 0 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

Im (zq) -15 -13 -11 -9 -7 -5 -3 -1 1 3 5 7 9 11 13 15

donde (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) = (y0, q, y1, q, y2, q, y3, q, y4, q, y5, q, y6, q, y7, q) , y

la regla de permutación predeterminada es: 10 v0, q = b2, q, v1, q = b6, q, v2, q = b0, q, v3, q = b1, q, v4, q = b4, q, v5, q b5, q, v6, q = b3, q, v7, q = b7, q.

3. Un método de procesamiento de recepción que comprende: 15 una etapa de desmapeo para desmapear celdas complejas (Re (Zq) , Im (Zq) ) de acuerdo con la constelación 256QAM (Modulación de Amplitud en Cuadratura) mostrada en las Tablas 3-1 y 3-2: [Tabla 3-1]

y0, q y2, q y4, q y6, q 1 0 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1 0 1 1 1 0 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0 0

Re (zq) -15 -13 -11 -9 -7 -5 -3 -1 1 3 5 7 9 11 13 15

[Tabla 3-2]

y1, q y3, q y5, q y7, q 1 0 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1 0 1 1 1 0 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0 0

Im (zq) -15 -13 -11 -9 -7 -5 -3 -1 1 3 5 7 9 11 13 15

una etapa de multiplexación de celda-a-bit para realizar una permutación en 8 secuencias de bits obtenidas como palabras de celda de 8 bits (y0, q, y1, q, y2, q, y3, q, y4, q, y5, q, y6, q, y7, q) en la etapa de desmapeo, de acuerdo con una regla de permutación predeterminada para permutar cada conjunto de 8 bits (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) de las 8 secuencias de bits a un conjunto de 8 bits (v0, q, v1, q, v2, q, v3, q, v4, q, v5, q, v6, q, v7, q) para obtener 8 secuencias de bits permutados vi, j, donde i indica una de las 8 secuencias y q y j son índices, y multiplexar las 8 secuencias de bits permutados obtenidos como resultado de la permutación en una secuencia de bits de manera que el bit vi+8xj de dicha una secuencia corresponde al bit vi, j;

una etapa de desintercalación de bits para realizar desintercalación de columnas-filas y desintercalación de paridad en la una secuencia de bits obtenida como resultado de la multiplexación, realizándose la desintercalación de columnas-filas con o sin giro; una etapa de decodificación para decodificar bits desintercalados en la etapa de desintercalación de bits, de acuerdo con un código de comprobación de paridad de baja densidad con tasa de código de 7/15 y una longitud

de palabra de código de 16200, el código de comprobación de paridad de baja densidad se muestra en la Tabla 3-3:

donde 5 (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) = (y0, q, y1, q, y2, q, y3, q, y4, q, y5, q, y6, q, y7, q) , y la regla de permutación predeterminada es: v0, q, = b2, q, v1, q = b6, q, v2, q = b0, q, v3, q = b1, q, v4, q = b4, q, v5, q = b5, q, v6, q = b3, q, v7, q = b7, q. 10

4. Un receptor (300) que comprende:

un desmapeador (310) adaptado para desmapear celdas complejas (Re (Zq) , Im (Zq) ) de acuerdo con la constelación 256QAM (Modulación de Amplitud en Cuadratura) mostrada en las Tablas 4-1 y 4-2; 15 [Tabla 4-1]

y0, q y2, q y4, q y6, q 1 0 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1 0 1 1 1 0 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0 0

Re (zq) -15 -13 -11 -9 -7 -5 -3 -1 1 3 5 7 9 11 13 15

[Tabla 4-2]

y1, q y3, q y5, q y7, q 1 0 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1 0 1 1 1 0 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0 0

Im (zq) -15 -13 -11 -9 -7 -5 -3 -1 1 3 5 7 9 11 13 15

un multiplexor (320) de celda-a-bit adaptado para realizar una permutación en 8 secuencias de bits obtenidas como las palabras de celda de 8 bits (y0, q, y1, q, y2, q, y3, q, y4, q, y5, q, y6, q, y7, q) mediante el desmapeador, de acuerdo con una regla de permutación predeterminada para permutar cada conjunto de 8 bits (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) a un conjunto de 8 bits (v0, q, v1, q, v2, q, v3, q, v4, q, v5, q, v6, q, v7, q) de las 8 secuencias de bits para obtener 8

secuencias de bits permutados vi, j, donde i indica una de las 8 secuencias y q y j son índices, y multiplexar las 8 secuencias de bits permutados obtenidos como resultado de la permutación en una secuencia de bits de manera que el bit vi+8xj de dicha una secuencia corresponde al bit vi, j; un desintercalador (330) de bits adaptado para realizar desintercalación de columnas-filas y desintercalación de paridad en la una secuencia de bits obtenida como resultado de la multiplexación, realizándose la

desintercalación de columnas-filas con o sin giro; un decodificador (340) adaptado para decodificar bits desintercalados mediante el desintercalador de bits, de acuerdo con un código de comprobación de paridad de baja densidad con tasa de código de 7/15 y una longitud de palabra de código de 16200, el código de comprobación de paridad de baja densidad se muestra en la Tabla 4-3;

donde 10 (b0, q, b1, q, b2, q, b3, q, b4, q, b5, q, b6, q, b7, q) = (y0, q, y1, q, y2, q, y3, q, y4, q, y5, q, y6, q. y7, q) , y la regla de permutación predeterminada es: v0, q = b2, q, v1, q= b6, q, v2, q= b0, q, v3, q= b1, q, v4, q= b4, q, v5, q= b5, q, v6, q= b3, q, v7, q= b7, q.

Patentes similares o relacionadas:

Uso de decisiones de bits fáciles para mejorar la desmodulación DPSK de datos SPS, del 30 de Abril de 2019, de QUALCOMM INCORPORATED: Un procedimiento de desmodulación de datos, dicho procedimiento que comprende: proporcionar una primera señal de entrada que comprende una palabra de […]

Aparato receptor, método de recepción, programa y sistema de recepción, del 31 de Mayo de 2017, de SONY CORPORATION: Un aparato receptor que comprende: un dispositivo de desintercalado configurado para recibir una señal (Sa) de datos codificados LDPC en conjuntos […]

Aparato y método de decodificación para un código LDPC de 64K y tasa 2/3, del 17 de Mayo de 2017, de SONY CORPORATION: Un aparto de decodificación para decodificar palabras de código codificadas con Comprobación de Paridad de Baja Densidad, LDPC, que comprende: una unidad de decodificación […]

Autentificación de URL de contenidos para dash, del 3 de Agosto de 2016, de Intel IP Corporation: Un dispositivo de cliente operativo de autentificación de un localizador uniforme de recursos de contenidos, URL, para transmisión continua adaptativa dinámica por protocolo […]

Notificación de congestión del plano de usuario, del 25 de Mayo de 2016, de INTEL CORPORATION: Un nodo de la red de acceso radio RAN operable para notificar una congestión del plano de usuario UPCON, teniendo el nodo RAN una circuitería computacional […]

Transmisión continua de video mejorada con corrección de errores hacia delante en la capa de aplicación, del 18 de Mayo de 2016, de INTEL CORPORATION: Un procedimiento para reconstrucción de video siguiendo descodificación de corrección de errores hacia delante en la capa de aplicación, AL-FEC, , comprendiendo el procedimiento: […]

Método de intercalación y método de desintercalación, del 2 de Marzo de 2016, de PANASONIC CORPORATION: Un método de intercalación realizado mediante un transmisor para un sistema de comunicación con códigos de comprobación de paridad de baja densidad cuasi cíclicos que incluye […]

Método de intercalación y método de desintercalación, del 2 de Marzo de 2016, de PANASONIC CORPORATION: Un método de intercalación realizado mediante un transmisor para un sistema de comunicación con códigos de comprobación de paridad de baja densidad cuasi cíclicos que incluye […]

CODIFICACION Y DECODIFICACION UTILIZANDO UN CODIGO CONSTRUIDO SOBRE UN TRELLIS CUYAS SECCIONES ESTAN BASADAS EN CODIGOS EN BLOQUE A BUENA DISTANCIA, del 16 de Diciembre de 2007, de FRANCE TELECOM: Procedimiento de codificación corrector de error, caracterizado porque implementa al menos dos secciones distintas de un código elemental predeterminado, asociando […]

CODIFICACION Y DECODIFICACION UTILIZANDO UN CODIGO CONSTRUIDO SOBRE UN TRELLIS CUYAS SECCIONES ESTAN BASADAS EN CODIGOS EN BLOQUE A BUENA DISTANCIA, del 16 de Diciembre de 2007, de FRANCE TELECOM: Procedimiento de codificación corrector de error, caracterizado porque implementa al menos dos secciones distintas de un código elemental predeterminado, asociando […]