ETAPA DE SALIDA LOGICA DE CIRCUITO INTEGRADO PROTEGIDA CONTRA UNA INVERSION DE BATERIA.

Etapa de salida lógica de un circuito integrado de tecnología CMOS,

que comprende una entrada (E) para una señal lógica de entrada, dos transistores (T1, T2) en serie que funcionan en push-pull bajo el control de la señal lógica de entrada, estando conectado un primer transistor (T1) a un terminal de alimentación alta (A) del circuito integrado y el segundo (T2) a un terminal de alimentación baja (M), y una salida (B) conectada al punto de unión de los dos transistores, caracterizada porque los dos transistores son transistores PMOS y porque un circuito de control de conducción (CCC), adecuado para aplicar a la puerta del segundo transistor (T2) una tensión negativa con respecto al terminal de alimentación baja cuando la señal lógica de entrada pasa a un nivel que tiende a bloquear el primer transistor, se interpone entre la entrada y la puerta del segundo transistor

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2007/061740.

Solicitante: E2V SEMICONDUCTORS.

Nacionalidad solicitante: Francia.

Dirección: AVENUE DE ROCHEPLEINE,38120 SAINT EGREVE.

Inventor/es: MASSON,THIERRY, COQUILLE,PIERRE.

Fecha de Publicación: .

Fecha Concesión Europea: 20 de Enero de 2010.

Clasificación Internacional de Patentes:

- H03K19/003C

Clasificación PCT:

- H02H11/00 ELECTRICIDAD. › H02 PRODUCCION, CONVERSION O DISTRIBUCION DE LA ENERGIA ELECTRICA. › H02H CIRCUITOS DE PROTECCION DE SEGURIDAD (indicación o señalización de condiciones de trabajo indeseables G01R, p. ej. G01R 31/00, G08B; localización de defectos a lo largo de las líneas G01R 31/08; dispositivos de protección H01H). › Circuitos de protección de seguridad para evitar la conmutación de puesta en servicio en el caso de que pudiera resultar una condición eléctrica de trabajo indeseada.

- H03K19/003 H […] › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › Modificaciones para aumentar la fiabilidad.

Fragmento de la descripción:

Etapa de salida lógica de circuito integrado protegida contra una inversión de batería.

La invención se refiere a los circuitos electrónicos integrados de tecnología MOS que deben alimentarse mediante una pila o una batería que puede tener una tensión relativamente elevada susceptible de destruir el circuito en caso de error de conexión de la batería. El error considerado en este caso es concretamente una conexión equivocada de una tensión negativa en una salida del circuito integrado cuyo sustrato está a un potencial más positivo (una referencia de masa por ejemplo).

A modo de ejemplo, en las aplicaciones para automóviles, la tensión clásica de alimentación la proporciona una batería de 12 voltios que se recarga de manera permanente a través de un regulador. En caso de error de derivación de la batería en el vehículo (conexión del terminal negativo en una salida de circuito integrado no destinada a recibir esta conexión) se puede admitir, como mucho, que las diversas instalaciones electrónicas dejan de funcionar, pero no puede admitirse que estén destruidas. Se ve no solamente que resisten a -12 voltios sino incluso por seguridad hasta -16 voltios (normalmente).

Un terminal de salida lógica comprende a menudo una etapa de salida push-pull que comprende un transistor PMOS y un transistor NMOS en serie, estando conectada la salida de la etapa al punto de unión de los dos transistores. Por etapa push-pull, se entiende un montaje de dos transistores en serie entre los terminales de alimentación, haciendo que uno de los transistores sea conductor mientras que el otro está bloqueado y viceversa, en función del estado lógico de la entrada de la etapa.

Por tanto, en este tipo de etapa, la salida está conectada al drenador del transistor MOS de canal N; o este drenador es una zona semiconductora dopada de tipo N que forma con el sustrato de tipo P (o con una cavidad de tipo P al potencial del sustrato) una unión NP.

Esta unión se polariza de manera directa si se aplica una tensión de alimentación negativa por error en la salida, mientras que el sustrato está a una tensión más positiva (cero). La unión se parte y se destruye el circuito inte- grado.

Las soluciones existentes para evitar este riesgo consisten esencialmente en prever un diodo en serie con la salida lógica, en el sentido inverso de la unión mencionada anteriormente. Este diodo impide el paso de corriente inversa en caso de conexión equivocada del terminal negativo de la batería en esta entrada. Pero este diodo no es fácil de integrar en el sustrato del circuito integrado y además introduce una caída de tensión de aproximadamente 0,7 voltios en la conexión de salida en régimen normal, lo que es perjudicial ya que la salida debe estar a un nivel lógico bajo. Además, es necesario polarizar el diodo en el sentido directo para estar seguro de que no introduce una caída de tensión incluso superior, por tanto, un consumo indeseable de corriente.

Asimismo se ha propuesto utilizar no un diodo en serie sino una resistencia en serie. Siguen existiendo los mismos inconvenientes: por ejemplo, con una corriente de salida nominal de 10 mA y una resistencia de limitación de corriente de al menos 50 ohmios (para evitar la destrucción de la unión en caso de conexión incorrecta), se produce una caída de tensión de 0,5 voltios en régimen normal, degradando el nivel lógico bajo que puede proporcionar la salida del circuito integrado.

Para resolver este problema, la invención propone modificar la etapa de salida para sustituir el conjunto en serie de un transistor NMOS y de un transistor PMOS por un conjunto en serie de dos transistores PMOS, controlados por niveles lógicos invertidos, teniendo el transistor PMOS conectado al potencial más bajo de la alimentación su puerta controlada por un circuito (una especie de bomba de carga) que proporciona una tensión inferior al potencial más bajo cuando el transistor debe hacerse conductor.

Dicho de otro modo, la invención propuesta es una etapa de salida lógica de un circuito integrado de tecnología CMOS, que comprende una entrada para una señal lógica de entrada, dos transistores en serie que funcionan en push-pull bajo el control de la señal lógica de entrada, estando conectado un primer transistor a un terminal de alimentación alta y el segundo a un terminal de alimentación baja, y una salida conectada al punto de unión de los dos transistores, caracterizada porque los dos transistores son transistores PMOS y porque un circuito de control de conducción, adecuado para aplicar a la puerta del segundo transistor una tensión negativa con respecto al terminal de alimentación baja cuando la señal lógica de entrada pasa a un nivel que tiende a bloquear el primer transistor, se interpone entre la entrada y la puerta del segundo transistor.

Preferiblemente, el circuito de control de conducción comprende un tercer y un cuarto transistor PMOS en serie, estando el tercer transistor conectado al terminal de alimentación alta y el cuarto al terminal de alimentación baja, y estando conectado el punto de unión de los transistores tercero y cuarto a la puerta del segundo transistor, estando controlada la puerta del cuarto transistor por una señal lógica inversa de la señal de entrada, comprendiendo el circuito además un condensador cuyo primer terminal está conectado al punto de unión de los transistores tercero y cuarto y un segundo terminal recibe una señal correspondiente a la señal de control del cuarto transistor retardada por un elemento de retardo.

Se prevé preferiblemente que un quinto transistor PMOS esté colocado en paralelo con el segundo, estando controlada la puerta del quinto transistor por un segundo circuito de control de conducción idéntico al primero, estando accionados los dos circuitos alternativamente bajo el control de un reloj que permite el funcionamiento de uno mientras que impide el funcionamiento del otro y viceversa.

El segundo y el quinto transistor están colocados ventajosamente en una misma cavidad de tipo opuesto al sustrato del circuito integrado.

En un perfeccionamiento, el segundo transistor está colocado en una cavidad de tipo N cuyo potencial se fija, mediante un circuito de polarización de cavidad, al valor del potencial de la salida si este potencial es positivo con respecto al sustrato y a un valor de potencial próximo al del sustrato si un potencial negativo con respecto al sustrato se aplica a la salida.

La etapa de salida según la invención es particularmente ventajosa cuando la salida está directamente conectada a un terminal de conexión exterior del circuito integrado.

Otras características y ventajas de la invención resultarán de la lectura de la descripción detallada que sigue, realizada en referencia a los dibujos adjuntos en los que:

- la figura 1 representa el principio de partida de una etapa de salida según la presente invención;

- la figura 2 representa la etapa de salida con su circuito de control de conducción;

- la figura 3 representa la etapa de salida con el detalle del circuito de control de conducción;

- la figura 4 representa el cronograma de las señales del circuito de la figura 3;

- la figura 5 ilustra el cronograma en el caso en el que la entrada permanece durante mucho tiempo al nivel alto;

- la figura 6 representa una modificación de la etapa de salida para permitir que la entrada permanezca durante mucho tiempo al nivel alto;

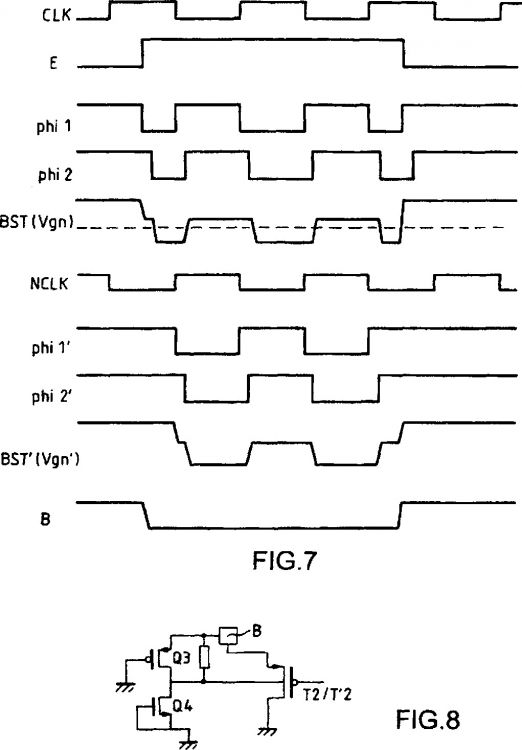

- la figura 7 representa un cronograma del circuito de la figura 6;

- la figura 8 representa un circuito de polarización de la cavidad del segundo transistor del conjunto push-pull conectado a la salida.

En la figura 1, se representa de forma simplificada el principio básico de una etapa de salida lógica según la invención.

El circuito integrado en sí mismo, con sus diferentes funcionalidades, no se representa y se supone que debe proporcionar a un terminal B de salida exterior una señal Vout lógica de nivel alto o bajo según el nivel lógico Vin bajo o alto que esta etapa recibe en una entrada E.

La etapa de salida comprende dos transistores PMOS T1 y T2 en serie entre los terminales de alimentación alta y baja, A y M, del circuito integrado. Estos terminales están destinados a recibir respectivamente un potencial de referencia nulo (terminal M) y un potencial de alimentación positivo Vdd (terminal A), por ejemplo de 12 voltios en una aplicación para automóvil. Los transistores están montados en lógica...

Reivindicaciones:

1. Etapa de salida lógica de un circuito integrado de tecnología CMOS, que comprende una entrada (E) para una señal lógica de entrada, dos transistores (T1, T2) en serie que funcionan en push-pull bajo el control de la señal lógica de entrada, estando conectado un primer transistor (T1) a un terminal de alimentación alta (A) del circuito integrado y el segundo (T2) a un terminal de alimentación baja (M), y una salida (B) conectada al punto de unión de los dos transistores, caracterizada porque los dos transistores son transistores PMOS y porque un circuito de control de conducción (CCC), adecuado para aplicar a la puerta del segundo transistor (T2) una tensión negativa con respecto al terminal de alimentación baja cuando la señal lógica de entrada pasa a un nivel que tiende a bloquear el primer transistor, se interpone entre la entrada y la puerta del segundo transistor.

2. Etapa de salida según la reivindicación 1, caracterizada porque el circuito de control de conducción comprende un tercer y un cuarto transistor PMOS en serie, estando el tercer transistor (Q1) conectado al terminal de alimentación alta y el cuarto (Q2) al terminal de alimentación baja, y estando conectado el punto de unión de los transistores tercero y cuarto a la puerta del segundo transistor (T2), estando controlada la puerta del cuarto transistor por una señal (phi1) lógica inversa de la señal de entrada, comprendiendo el circuito además un condensador (C) cuyo primer terminal está conectado al punto de unión de los transistores tercero y cuarto y un segundo terminal recibe una señal (phi2) correspondiente a la señal de control del cuarto transistor retardada por un elemento de retardo (DL).

3. Etapa de salida según una de las reivindicaciones 1 y 2, caracterizada porque un quinto transistor (T2') PMOS está colocado en paralelo con el segundo (T2), estando controlada la puerta del quinto transistor por un segundo circuito de control de conducción (CCC') idéntico al primero (CCC), estando accionados los dos circuitos alternativamente bajo el control de un reloj que permite el funcionamiento de uno mientras que impide el funcionamiento del otro y viceversa.

4. Etapa de salida según la reivindicación 3, caracterizada porque el segundo y el quinto transistor (T2, T2') están colocados en una misma cavidad de tipo opuesto al sustrato del circuito integrado.

5. Etapa de salida según una de las reivindicaciones 1 a 4, caracterizada porque el segundo transistor (T2) está colocado en una cavidad de tipo N cuyo potencial se fija al valor del potencial de la fuente de este transistor si este potencial es positivo con respecto al sustrato y a un valor de potencial próximo al del sustrato si un potencial negativo con respecto al sustrato se aplica a la salida (B).

6. Etapa de salida según la reivindicación 5, caracterizada porque comprende un circuito (Q3, Q4) de polarización de la cavidad del segundo transistor, que comprende un transistor PMOS (Q3) que tiene su fuente conectada a la salida (B), su puerta al sustrato y su drenador conectado a la cavidad así como al drenador de un transistor (Q4) NMOS que tiene su fuente y su puerta conectadas al sustrato, estando conectados los drenadores unidos de estos dos transistores a la cavidad del segundo transistor.

7. Etapa de salida según una de las reivindicaciones anteriores, caracterizada porque la salida (B) es un terminal de conexión exterior del circuito integrado.

Patentes similares o relacionadas:

Protección contra batería invertida para dispositivos alimentados por batería, del 1 de Julio de 2020, de Ascensia Diabetes Care Holdings AG: Un circuito de protección contra batería invertida que comprende: un primer MOSFET de canal P (1132a) que tiene una puerta, un drenaje y una fuente; […]

Dispositivo de conmutación de protección DI y procedimiento de funcionamiento para identificar una tensión en el conductor PEN, del 10 de Junio de 2020, de Heinrich Kopp GmbH: Dispositivo de conmutación de protección DI con un transformador de corriente total para detectar corrientes de defecto en un conductor de fase y un conductor […]

Sistemas, procedimientos y aparatos para detectar el robo y el estado de la energía eléctrica, del 19 de Junio de 2019, de ACLARA METERS LLC: Un procedimiento para detectar el robo y el estado de la energía eléctrica, comprendiendo el procedimiento: supervisar, mediante uno o más sensores, […]

Unidad de suministro de energía para proporcionar al menos una salida de energía conmutable, del 19 de Junio de 2019, de PHOENIX CONTACT GMBH & CO. KG: Unidad de suministro de energía para proporcionar al menos una salida de energía conmutable (Uout1, Uout2, ..., UoutN) • al menos una entrada de energía […]

Aparato de alimentación de CC, del 3 de Junio de 2019, de SAMSUNG ELECTRONICS CO., LTD.: Un aparato de alimentación de corriente continua (CC), que comprende: una unidad de entrada configurada para recibir una alimentación de CC externa; […]

Dispositivo y procedimiento de seguridad para instalación eléctrica, del 24 de Abril de 2019, de SCHNEIDER ELECTRIC INDUSTRIES SAS: Dispositivo de seguridad (16, 16a, 16b, 16c, 16d, 16e, 40) apto para conectarse entre un dispositivo disyuntor (14, 14a, 14b, 14c, 14d, 14e) y una instalación […]

Sistema y dispositivo de impulso de una pluralidad de unidades de alta potencia, del 17 de Abril de 2019, de Opulent Electronics International PTE Ltd: Un controlador único que comprende un lado primario y un lado secundario, comprendiendo el lado primario del controlador único un controlador digital […]

Inversor para módulos fotovoltaicos, del 17 de Mayo de 2017, de LSIS Co., Ltd: Un inversor fotovoltaico, que comprende: una unidad de entrada que tiene una primera unidad de entrada y una segunda unidad […]