ARQUITECTURA DE CIRCUITO INTEGRADO QUE TIENE UNA AGRUPACION DE CELULAS DE PRUEBA QUE PROPORCIONAN UN CONTROL ABSOLUTO PARA LA VERIFICACION DE CIRCUITOS AUTOMATICOS.

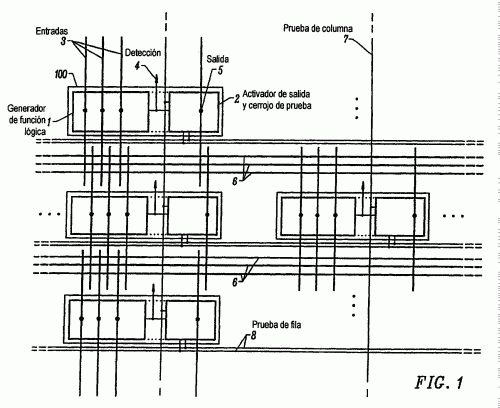

Circuito integrado, que consta de: una matriz o red de células lógicas prefabricada (100),

que puede combinarse para formar un circuito arbitrario, en el cual una pluralidad de células lógicas (100) en dicha matriz incluyen cada una: una salida de célula (5); un generador de función lógica (1); y un circuito de prueba (2), conectado de manera operativa a dicha salida de célula y a dicho generador de función lógica (1), en el que el circuito de prueba (2) comprende una primera entrada de prueba (8) dispuesta para recibir una señal de selección de modo (CMD0), y una segunda entrada de prueba (8) dispuesta para recibir un valor lógico de prueba (CMD1), y el circuito de prueba (2) puede operarse en un primer modo de operación para pasar dicho valor lógico de prueba (CMD1) a dicha salida de célula (5) y operable en un segundo modo de operación para pasar un valor lógico generado desde dicho generador de función lógica (1) a dicha salida de célula (5), estando determinado el modo de operación de dicho circuito de prueba (2) por dicha señal de selección de modo (CMD0), y en el que dicho circuito de prueba (2) forma parte de cada una de la mencionada pluralidad de células lógicas (100) en dicha matriz de células lógicas prefabricada antes de conectar dicha matriz para formar dicho circuito arbitrario y con independencia de que éste se forme finalmente conectando dicha matriz de células lógicas prefabricada, caracterizado porque dicho circuito de prueba (2) comprende además una unidad de almacenamiento (14, 17) y una tercera entrada de prueba (7) dispuesta para recibir una señal de retención, estando dispuesta dicha unidad de almacenamiento (14, 17) para almacenar, en respuesta a dicha señal de retención, dicha señal de selección de modo (CMD0) y dicho valor lógico de prueba (CMD1), de tal modo que el circuito de prueba (2) en algunas células lógicas de dicha matriz de células lógicas sea operable en dicho primer modo de operación mientras que, simultáneamente, el circuito de prueba (2) en otras células lógicas de dicha matriz de células lógicas sea operable en dicho segundo modo de operación.

Tipo: Resumen de patente/invención.

Solicitante: LIGHTSPEED SEMICONDUCTORS CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 1151 SONORA COURT,SUNNYVALE, CA 94086.

Inventor/es: OSANN, ROBERT, JR.

Fecha de Publicación: .

Fecha Solicitud PCT: 2 de Abril de 1998.

Fecha Concesión Europea: 12 de Marzo de 2003.

Clasificación Internacional de Patentes:

- G06F11/267 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Reconfiguración para pruebas, p. ej. LSSD, partición.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Finlandia, Chipre, Oficina Europea de Patentes.

Patentes similares o relacionadas:

Procedimiento para la verificación de al menos una unidad de cálculo integrada en un aparato de control, del 25 de Diciembre de 2013, de ROBERT BOSCH GMBH: Procedimiento para la verificación de unidades de cálculo incorporadas en un aparato de control,presentando el aparato de control una interfaz […]

Procedimiento para la verificación de al menos una unidad de cálculo integrada en un aparato de control, del 25 de Diciembre de 2013, de ROBERT BOSCH GMBH: Procedimiento para la verificación de unidades de cálculo incorporadas en un aparato de control,presentando el aparato de control una interfaz […]

SISTEMA Y METODO DE DIAGNOSTICO REMOTO., del 1 de Noviembre de 2003, de RICOH COMPANY: SE DESCRIBE UN SISTEMA DE DIAGNOSTICO REMOTO QUE INCLUYE UN SISTEMA DE ORDENADOR CENTRAL QUE RECIBE DATOS DE USUARIO RELACIONADOS CON UNA PETICION DEL USUARIO, […]

CIRCUITO INTEGRADO DE APLICACION ESPECIFICA (ASIC) CON MICROPROCESADOR QUE INCORPORA MEDIOS DE PRUEBA, del 16 de Junio de 1998, de SOCIETE D'APPLICATIONS GENERALES D'ELECTRICITE ET DE MECANIQUE SAGEM: CIRCUITO INTEGRADO DE APLICACION ESPECIFICA (ASIC), QUE COMPRENDE UN MICROPROCESADOR , EN EL CUAL AL MENOS UNA ENTRADA FUNCIONAL ESTA UNIDA A UNA […]

PROCEDIMIENTO PARA ENSAYAR UN BUS DE DIRECCIONES EN UN MÓDULO LÓGICO, del 29 de Julio de 2011, de ROBERT BOSCH GMBH: Procedimiento para el ensayo de un bus de direcciones en un módulo lógico , en el que en el módulo lógico está previsto al […]

SISTEMA Y METODO DE SOBREDIVISION EN PARTICIONES PARA INCREMENTAR LOS PUNTOS DE CONTROL EN APLICACIONES PARALELAS BASADAS EN PROGRAMAS COMPONENTES, del 16 de Octubre de 2007, de AB INITIO SOFTWARE CORPORATION: SE DESCRIBEN DOS PROCEDIMIENTOS PARA SEGMENTAR EL TRABAJO QUE DEBE SER REALIZADO POR UN PROGRAMA DE ORDENADOR EN PARTES MAS PEQUEÑAS DE MANERA QUE […]

SISTEMA Y METODO DE SOBREDIVISION EN PARTICIONES PARA INCREMENTAR LOS PUNTOS DE CONTROL EN APLICACIONES PARALELAS BASADAS EN PROGRAMAS COMPONENTES, del 16 de Octubre de 2007, de AB INITIO SOFTWARE CORPORATION: SE DESCRIBEN DOS PROCEDIMIENTOS PARA SEGMENTAR EL TRABAJO QUE DEBE SER REALIZADO POR UN PROGRAMA DE ORDENADOR EN PARTES MAS PEQUEÑAS DE MANERA QUE […]