Turbo codificación con intercaladores QPP de libre contención.

Un método para operar un turbo codificador, el método que comprende los pasos de:

recibir un bloque de entrada de tamaño K'; y codificar el bloque de entrada usando un intercalador (201) de tamaño K' y una permutación T (i) = (f1 x i + f2 x i2) mod K', donde 0< i< K'-1 es el índice secuencial de las posiciones de símbolo después de intercalar, T (i) es el índice de símbolo antes del intercalado correspondiente a la posición i, K' es el tamaño del intercalador en símbolos y f1 y f2 son los factores que definen el intercalador (201) y en donde los valores de K', f1, f2 se toman de al menos una fila de la siguiente tabla:

K' f1 f2 40 37 20 56 19 42 72 19 60 104 45 26 120 103 90 136 19 102 152 135 38 168 101 84 192 85 24 216 13 36 248 33 62 280 103 210 320 21 120 368 25 138 384 25 240 416 77 52 472 175 118 544 35 68 624 41 234 704 155 44 800 207 80 912 85 114 1056 229 132 1184 217 148 1344 211 252 1536 71 48 1728 127 96 1984 185 124 2240 209 420 2304 253 216 2560 39 240 2944 231 184 3328 51 104 3776 179 236 4096 95 192 4352 477 408 4992 233 312 5632 45 176 6144 263 480 7296 137 456 8192 417 448

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2007/084390.

Solicitante: Motorola Mobility, Inc.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 600 North US Highway 45 Libertyville, IL 60048 ESTADOS UNIDOS DE AMERICA.

Inventor/es: CLASSON,BRIAN K, BLANKENSHIP,Yufei W, NIMBALKER,Ajit.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M13/27 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › usando técnicas de entrelazado.

- H03M13/29 H03M 13/00 […] › combinando dos o más códigos o estructuras de códigos, p. ej. códigos de productos, códigos de producto generalizados, códigos concatenados, códigos internos y externos.

PDF original: ES-2381595_T3.pdf

Fragmento de la descripción:

Turbo codificación con intercaladores QPP de libre contención.

Campo de la Invención La presente invención se refiere de manera general a codificación y descodificación de datos y en particular, a un método y aparato para turbo codificación y turbo descodificación.

Antecedentes de la Invención

Las transmisiones de datos digitales sobre enlaces cableados e inalámbricos pueden estar dañadas, por ejemplo, por ruido en el enlace o canal, por interferencia de otras transmisiones, o por otros factores ambientales. Para combatir los errores introducidos por el canal, muchos sistemas de comunicación emplean técnicas de corrección de errores para ayudar en la comunicación.

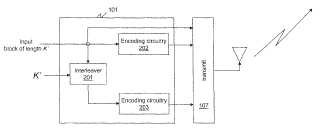

Una técnica utilizada para corrección de errores es la turbo codificación de un bloque de información antes de que este sea transmitido sobre el canal. Utilizando tal técnica, un codificador dentro del transmisor de un sistema de comunicación codificará un bloque de entrada u de longitud K' bits en un bloque de palabra de código x de N bits. El bloque de palabra de código es transmitido entonces sobre el canal, posiblemente después de procesamiento adicional tal como el intercalado de canal como se define en las especificaciones IEEE 802.16e. En el receptor, el turbo descodificador toma el vector de señal recibido y de longitud N como entrada, y genera una estimación û del vector u.

Típicamente el turbo codificador está compuesto de dos codificadores convolucionales constituyentes. El primer codificador constituyente toma el bloque de entrada u como entrada en su orden original, y el segundo codificador constituyente toma el bloque de entrada u en su orden intercalado después de pasar u a través de un turbo intercalador J . La salida del turbo codificador x está compuesta de los bits sistemáticos (igual al bloque de entrada u) , los bits de paridad del primer codificador constituyente, y los bits de paridad del segundo codificador constituyente.

De la misma manera el turbo decodificador dentro del receptor del sistema de comunicación está compuesto de dos decodificadores convolucionales constituyentes, uno para cada código constituyente. Los descodificadores J-1

constituyentes son separados por el intercalador J y el correspondiente desintercalador . Los mensajes en el formato de relaciones logarítmicas de verosimilitud (LLR) se pasan entre los descodificadores constituyentes iterativamente. La decisión û se toma después de varias iteraciones.

El turbo intercalador J es el componente clave en el diseño de turbo código. Es responsable de aleatorizar el bloque de entrada u de una manera pseudo-aleatoria, proporcionando de esta manera las palabras de código x con buena distribución de peso, y por lo tanto buenas capacidades de corrección de errores. Además del rendimiento de descodificación, la definición del turbo intercalador J afecta extremadamente la implementación del turbo decodificador dentro del receptor. Para permitir alto nivel de procesamiento en paralelo sin contenciones de acceso a memoria, el turbo intercalador J necesita tener propiedades de libre contención.

ERICSSON: "Intercaladores Polinómicos de Permutación Cuadrática para Turbo Codificación en LTE" TDOC R1063137 DE LA REUNIÓN #47 DEL TSG RAN WG 1 DEL 3GPP, [En línea] 10 de noviembre del 2006 () , páginas 1-5, XP002473949 Riga, Letonia Recuperado de Internet: URL: http://www.3gpp.org/ftp/tsg_ran/WG1_RL1/TSGR1_47/Docs/> [recuperada el 26] propone intercaladores basados en polinomios de permutación cuadrática.

MOTOROLA: "Segmentación de Bloques de Código para Turbo Intercaladores de Libre Contención" TDOC R1063062 DE LA REUNIÓN #47 DEL TSG RAN WG 1, [En línea] 10 de noviembre del 2006 () , páginas 1-4, XP002473950 Riga, Letonia Recuperado de Internet: URL: http://www.3gpp.org/ftp/tsg_ran/WG1_RL1/TSGR1_47/Docs/> [recuperada el ] propone una regla de segmentación de bloques de código modificada para turbo codificación EUTRA.

ROSNES E Y OTROS: "Intercaladores basados en polinomios de permutación cuadrática de distancia óptima paraturbo códigos" Actas del SIMPOSIO INTERNACIONAL SOBRE TEORÍA DE LA INFORMACIÓN DEL IEEE EN 2006, 9 de Julio 2006 () , -14 de Julio 2006 () páginas 1988-1992, XP002473952 Seattle, USA ISBN: 1-4244-0504-1 considera en detalle la distancia mínima de intercaladores basados en QPP de turbo códigos.

TAKESHITA O Y: "En intercaladores de libre contención y polinomios de permutación sobre anillos enteros"TRANSACCIONES DEL IEEE SOBRE TEORÍA DE LA INFORMACIÓN IEEE USA, vol.52, nº 3, marzo de 2006 (032006) , páginas 1249-1253, XP002473953 ISSN: 0018-9448 expresa que muestra que los polinomios de permutación generan intercaladores de libre contención máximos.

Breve Descripción de los Dibujos

La FIG. 1 es un diagrama de bloques de un transmisor. La FIG.2 es un diagrama de bloques del codificador turbo de la FIG.1. La FIG.3 es un diagrama de bloques de un receptor. La FIG.4 es un diagrama de bloques del turbo descodificador de la FIG.4. La FIG.5 es un diagrama de flujo que muestra el funcionamiento del transmisor de la FIG.1. La FIG.6 es un diagrama de flujo que muestra el funcionamiento del receptor de la FIG.3.

Descripción Detallada de los Dibujos Para abordar la necesidad mencionada anteriormente para intercaladores de libre contención, se proporciona aquí dentro un método y aparato para seleccionar tamaños de intercalador para turbo códigos.

Durante el funcionamiento se recibe un bloque de información de tamaño K. Un intercalador de tamaño K' se determina donde K' está relacionada con K'' donde K'' es de un conjunto de tamaños; en el que el conjunto de tamaños comprende K''= ap x f , p : p : p ; f : f : f , en donde a es un entero, f es un entero min max min max continuo entre fmin y fmax , y p toma valores enteros entre pmin y pmax , a>1, pmax > pmin , pmin >1. El bloque de información de tamaño K se rellena en un bloque de entrada de tamaño K'. El bloque de entrada se intercala usando un intercalador de tamaño K'. El bloque de entrada original y el bloque de entrada intercalado son codificados para obtener un bloque de palabra de código. El bloque de palabra de código es transmitido a través del canal. En una realización adicional de la presente invención el paso de determinar el tamaño del intercalador K' que está relacionado con K'' comprende el paso de usar K'=K''.

Aún en otra realización de la presente invención el paso de determinar el tamaño del intercalador K' que está

m

relacionado con K'' comprende el paso de usar K'=K'' cuando K'' no es un múltiplo de (2 -1) ; de otro modo m

usando K'=K''+5 (K'') cuando K'' es un múltiplo de (2 -1) , en donde m es la longitud de memoria del codificador convolucional constituyente, y 5 (K'') es un entero pequeño positivo o negativo distinto a un múltiplo de m

(2 -1) . En una realización m=3.

En un ejemplo ARP útil para entender la presente invención el paso de intercalar el bloque de entrada comprende el paso de usar una permutación J (i) = (iP + A + d (i) ) modK', donde 0 : i: K '-1 es el índice

secuencial de las posiciones de símbolo después de intercalar, J (i) es el índice del símbolo antes del intercalamiento correspondiente a la posición i, K' es el tamaño del intercalador en símbolos, P es un número que es relativamente primo con K', A es una constante, C es un pequeño número que divide K', y d (i) es un vector oscilatorio de pequeña amplitud de la forma d (i) =P (i modC) + P xa (i modC) donde a (.) y P (.) son

vectores cada uno de longitud C, aplicados periódicamente para 0 : i : K '-1 . En aún otra realización de la presente invención el paso de intercalar el bloque de entrada comprende el paso de usar una permutación J (i) = (f x i + f x i ) modK', donde 0: i : K'-1es el índice secuencial de las posiciones de los símbolos después de intercalar, J (i) es el índice del símbolo antes del intercalamiento correspondiente a la posición i, K' es el tamaño del intercalador en símbolos, y f y f son los factores que definen el intercalador.

Anterior a describir la codificación y descodificación de datos, se proporcionan las siguientes definiciones para establecer los conocimientos necesarios:

• K indica el tamaño de un bloque de información.

• K' indica un tamaño de intercalador (es decir, el tamaño de bloque de entrada para el cual se define un turbo código intercalador) .

•... [Seguir leyendo]

Reivindicaciones:

1. Un método para operar un turbo codificador, el método que comprende los pasos de:

recibir un bloque de entrada de tamaño K'; y codificar el bloque de entrada usando un intercalador (201) de tamaño K' y una permutación T (i) = (f1 x i + f2 x i2) mod K', donde 0 < i < K'-1 es el índice secuencial de las posiciones de símbolo después de intercalar, T (i) es el índice de símbolo antes del intercalado correspondiente a la posición i, K' es el tamaño del intercalador en símbolos y f1 y f2 son los factores que definen el intercalador (201) y en donde los valores de K', f1, f2 se toman de al menos una fila de la siguiente tabla:

K' f1 f2 40 37 20 56 19 42 72 19 60 104 45 26 120 103 90 136 19 102 152 135 38 168 101 84 192 85 24 216 13 36 248 33 62 280 103 210 320 21 120 368 25 138 384 25 240 416 77 52 472 175 118 544 35 68 624 41 234 704 155 44 800 207 80 912 85 114 1056 229 132 1184 217 148 1344 211 252 1536 71 48 1728 127 96 1984 185 124 2240 209 420 2304 253 216 2560 39 240 2944 231 184 3328 51 104 3776 179 236 4096 95 192 4352 477 408 4992 233 312 5632 45 176 6144 263 480 7296 137 456 8192 417 4482. Un aparato para operar un turbo codificador (101) , el aparato que comprende los pasos de:

una circuitería de recepción que recibe un bloque de entrada de tamaño K'; y un codificador que codifica el bloque de entrada usando un intercalador (201) de tamaño K' y una permutación T (i) = (f1 x i + f2 x i2) mod K', donde 0 < i < K'-1 es el índice secuencial de las posiciones de símbolo después de intercalar, T (i) es el índice de símbolo antes del intercalado correspondiente a la posición i, K' es el tamaño del intercalador en símbolos y f1 y f2 son los factores que definen el intercalador (201) y en donde los valores de K', f1, f2 se toman de al menos una fila de la siguiente tabla:

K' f1 f2 40 37 20 56 19 42 72 19 60 104 45 26 120 103 90 136 19 102 152 135 38 168 101 84 192 85 24 216 13 36 248 33 62 280 103 210 320 21 120 368 25 138 384 25 240 416 77 52 472 175 118 544 35 68 624 41 234 704 155 44 800 207 80 912 85 114 1056 229 132 1184 217 148 1344 211 252 1536 71 48 1728 127 96 1984 185 124 2240 209 420 2304 253 216 2560 39 240 2944 231 184 3328 51 104 3776 179 236 4096 95 192 4352 477 408 4992 233 312 5632 45 176 6144 263 480 7296 137 456 8192 417 448

Patentes similares o relacionadas:

Método y dispositivo de codificación, del 15 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación, que comprende: realizar (S101), mediante un extremo de transmisión basado en un polinomio de verificación de redundancia cíclica, […]

Método y aparato para la transmisión inalámbrica de datos sujeta a bloqueos de señal periódicos, del 23 de Octubre de 2019, de Hughes Network Systems, LLC: Un método para la transmisión inalámbrica de una primera corriente de datos, estando la transmisión sujeta a bloqueos periódicos, el método que comprende: segmentar una […]

Procedimiento y sistema para generar códigos de canal, en particular, para un encabezamiento de trama, del 11 de Septiembre de 2019, de POLITECNICO DI TORINO: Un procedimiento para generar un código de canal, en particular, para un encabezamiento de trama, para codificar una señal en la que el valor objetivo […]

Intercalador de bits para un sistema de BICM con códigos de QC-LDPC, del 3 de Julio de 2019, de PANASONIC CORPORATION: Un procedimiento de intercalación de bits para intercalar bits de una palabra de código generada en base a un esquema de codificación de comprobación de paridad de baja densidad […]

Aparato de transmisión de CDMA y método de transmisión de CDMA, del 19 de Junio de 2019, de INVT SPE LLC: Un aparato de transmisión de CDMA que comprende: una sección de control que reconoce tipos de datos incluidos en una pluralidad de elementos de datos y emite: […]

Procedimiento, sistema y dispositivo para detección de errores en redes de comunicación inalámbrica OFDM sin decodificación de corrección de errores hacia delante completa, del 26 de Abril de 2019, de TELEFONICA, S.A.: Un procedimiento para detectar errores en un paquete de información recibido por un receptor OFDM en un sistema de multiplexación por división de frecuencias ortogonales, […]

Intercalador de bits para un sistema de BICM con códigos QC LDPC, del 6 de Marzo de 2019, de PANASONIC CORPORATION: Un procedimiento de entrelazado de bits para entrelazar bits de una palabra de código generada basándose en un esquema de codificación de verificación de paridad de baja densidad […]

Entrelazador de bits para un sistema BICM con códigos QC LDPC, del 28 de Febrero de 2019, de PANASONIC CORPORATION: Un método de entrelazado de bits para entrelazar bits de una palabra de código generada en base a un esquema de codificación con comprobación de paridad de baja densidad […]