TEST DE MEMORIA.

Procedimiento para accionar y/o evaluar memorias (2) con células de memoria (1),

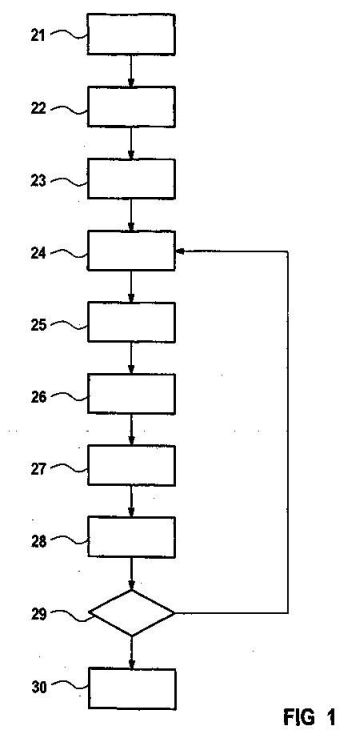

en el cual se forma, para las células de memoria (1), una primera información de test, dependiendo de una paridad variable (VP) asignada a la célula de memoria (1) respectiva, y de un contenido de la célula de memoria (1) respectiva, caracterizado porque en varios ciclos de test: - en cada caso, en una primera fase: - es leído en cada caso un contenido de las células de memoria (1), - para las células de memoria (1), se forma, en cada caso, una primera información de test, dependiendo de la paridad variable asignada a la célula de memoria respectiva (1) y el contenido de la célula de memoria respectiva (1) leído en la primera fase, - se amplían en cada caso las células de memoria (1) con el contenido leído en la primera fase, y se describe la primera información de test, y - en cada caso, en una segunda fase se lee el contenido de las células de memoria (1) para reconocer errores en el procedimiento de direccionamiento, se forma una segunda información de test a partir del contenido leído en la segunda fase teniendo en cuenta la paridad variable, y se compara la segunda información de test con la primera información de test para la célula de memoria respectiva (1) formada en la primera fase, asimismo está prevista una cantidad de ciclos de test correspondiente a una cantidad de bits de dirección (7) de una dirección de memoria representada en forma binaria, y en cada ciclo de test se utiliza, en cada caso, otro bit de dirección (7) para la variación de la paridad variable.

Tipo: Resumen de patente/invención.

Solicitante: SIEMENS AKTIENGESELLSCHAFT.

Nacionalidad solicitante: Alemania.

Dirección: WITTELSBACHERPLATZ 2,80333 MUNCHEN.

Inventor/es: MAYER, FRANK, MERCHANT, KAMAL.

Fecha de Publicación: .

Clasificación PCT:

- G06F11/10 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › añadiendo cifras binarias o símbolos especiales a los datos expresados según un código, p. ej. control de paridad, exclusión de los 9 o de los 11.

- G06F11/22 G06F 11/00 […] › Detección o localización de hardware defectuoso efectuando pruebas durante las operaciones de espera (standby) o durante los tiempos muertos, p. ej. pruebas de arranque.

- G11C29/00 G […] › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › Verificación del funcionamiento correcto de memorias; Ensayo de memorias durante su funcionamiento fuera de línea (offline")o en espera ("standby").

Patentes similares o relacionadas:

Vigilancia a distancia de un sistema de procesamiento de datos mediante una red de comunicaciones, del 30 de Octubre de 2018, de Accenture Global Services Limited: Un sistema de procesamiento de datos a distancia que comprende: un receptor de datos para recibir un mensaje de datos; una […]

uso de toma de huellas digitales de potencia (pfp) para monitorizar la integridad y potenciar la seguridad de sistemas informáticos, del 22 de Febrero de 2017, de VIRGINIA TECH INTELLECTUAL PROPERTIES, INC.: Método para realizar una estimación de integridad en tiempo real de ejecución de una rutina en una plataforma de procesamiento informático, que comprende: (a) […]

SISTEMA Y PROCEDIMIENTO PARA DETECTAR UN DEFECTO EN LAS INTERCONEXIONES DE GRAN LONGITUD DE UN CIRCUITO DIGITAL AVANZADO, del 7 de Mayo de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sistema y procedimiento para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado.

La invención […]

SISTEMA Y PROCEDIMIENTO PARA DETECTAR UN DEFECTO EN LAS INTERCONEXIONES DE GRAN LONGITUD DE UN CIRCUITO DIGITAL AVANZADO, del 7 de Mayo de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sistema y procedimiento para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado.

La invención […]

DISPOSITIVO DE IMPRESION, METODO DE DIAGNOSTICO PARA DISPOSITIVO DE IMPRESION Y PROGRAMA DE DIAGNOSTICO PARA DISPOSITIVO DE IMPRESION., del 1 de Junio de 2007, de SEIKO EPSON CORPORATION: Una impresora adaptada a usar una pluralidad de canales (1ch, ....8ch) para realizar la comunicación inalámbrica, que comprende; unos medios de salida […]

SISTEMA Y METODO PARA EL DIAGNOSTICO EN SERVICIO DEL SOFTWARE DE UN SISTEMA DE DISPOSITIVO DE COMUNICACIONES SIN CABLES., del 16 de Diciembre de 2006, de KYOCERA WIRELESS CORPORATION: Método para diagnóstico en servicio de software de sistema en un dispositivo de comunicaciones sin cables, cuyo método comprende: ejecutar el software del sistema […]

PRUEBA AUTOMATICA INTEGRADA JERARQUICA., del 1 de Diciembre de 2006, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un aparato para proporcionar autocomprobación integrada jerárquica para un sistema con chip, comprendiendo dicho aparato: un controlador BIST […]

PROCEDIMIENTO PARA LA VERIFICACION DE UN NUCLEO DE ORDENADOR DE UN MICROPROCESADOR O DE UN MICRO CONTROLADOR., del 1 de Noviembre de 2006, de ROBERT BOSCH GMBH: Procedimiento para la creación de una prueba automática para la verificación de la función correcta de un núcleo de ordenador de […]

APARATO Y METODO PARA RECUPERAR DATOS A DISTANCIA., del 16 de Noviembre de 2004, de ONTRACK DATA INTERNATIONAL, INC.: La invención se refiere a un aparato y a un procedimiento para recuperar a distancia datos inaccesibles sobre dispositivos informáticos de almacenamiento. El […]