Tarjeta de microprocesador.

Tarjeta (105, 705) de microprocesador que incluye un primer microprocesador (110) para ejecutar primeras aplicaciones,

caracterizada porque dicha tarjeta de microprocesador comprende además un segundo microprocesador (210) para ejecutar segundas aplicaciones, incluyendo dicho primer microprocesador medios para transmitir al segundo microprocesador comandos procedentes desde el exterior (300) de la tarjeta y para transmitir al exterior de la tarjeta respuestas a esos comandos procedentes del segundo microprocesador, estando adaptado el primer microprocesador para utilizar un nivel de capacidad para resistir ataques, fallos o pérdidas de datos inferior al del segundo microprocesador.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E08290289.

Solicitante: OBERTHUR TECHNOLOGIES.

Nacionalidad solicitante: Francia.

Dirección: 50, QUAI MICHELET 92300 LEVALLOIS-PERRET FRANCIA.

Inventor/es: Stranges,Lorenzo, Chamley,Olivier.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06K19/07 FISICA. › G06 CALCULO; CONTEO. › G06K RECONOCIMIENTO DE DATOS; PRESENTACION DE DATOS; SOPORTES DE REGISTROS; MANIPULACION DE SOPORTES DE REGISTROS (impresión per se B41J). › G06K 19/00 Soportes de registro para utilización con máquinas y con al menos una parte prevista para soportar marcas digitales. › con chips de circuito integrado.

PDF original: ES-2380750_T3.pdf

Fragmento de la descripción:

Tarjeta de microprocesador

Descripción

La presente invención se refiere a una tarjeta de microprocesador. Más en particular, se refiere a tarjetas de microprocesador conformes a la norma ISO 7816 y a tarjetas de microprocesador conformes a la norma MMC (MultiMedia Card, tarjeta multimedia) .

Algunas tarjetas de microprocesador pueden contener múltiples aplicaciones almacenadas en una memoria no volátil, por ejemplo una ROM o una EEPROM, es decir, su microprocesador contiene en memoria códigos ejecutables (o interpretables) de múltiples aplicaciones de procesamiento de datos y está adaptado para ejecutarlos. En algunos casos, las tarjetas de microprocesador pueden incluir al mismo tiempo una aplicación con un alto requisito de seguridad y una aplicación con requisito de seguridad moderado.

Aplicaciones con un alto requisito de seguridad son normalmente aplicaciones de pago, por ejemplo, o aplicaciones que identifican al titular (pasaporte, carné de identidad) . Los clientes exigen un alto nivel de seguridad en estas aplicaciones y esto necesita evaluaciones particularmente lentas y costosas, por ejemplo según criterios comunes, realizadas por una organización certificada independiente. Algunas evaluaciones de un diseño de una tarjeta con procesador pueden tardar más de un año y costar decenas de miles de euros. Si la aplicación evoluciona se requiere una evaluación adicional, posiblemente a menor escala.

Aplicaciones con un requisito de seguridad moderado incluyen, por ejemplo, aplicaciones de telefonía móvil (por ejemplo, identificación de abonado de red de telefonía móvil) y aplicaciones de transporte (por ejemplo, acceso a una red pública de transporte) . Estas aplicaciones no necesitan generalmente una certificación o necesitan una certificación que es mucho menos lenta y costosa que las mencionadas anteriormente.

Si estos dos tipos de aplicación coexisten en el mismo microprocesador de tarjeta inteligente, las aplicaciones con requisitos de seguridad moderados deben evaluarse y certificarse según los mismos criterios que las aplicaciones con un alto requisito de seguridad, lo que da lugar a altos costes y largos retrasos.

Además, los lectores de tarjeta de microprocesador están adaptados generalmente para leer una tarjeta con microprocesador a través de contactos previstos para este fin en la superficie de la tarjeta con microprocesador, cuya función está generalmente predeterminada y no cambia durante la vida útil del lector. Para adaptarse a una nueva función de un contacto, generalmente es necesario modificar los componentes electrónicos del lector, lo que generalmente no es posible (a un coste razonable) por parte de los consumidores que utilizan estos lectores.

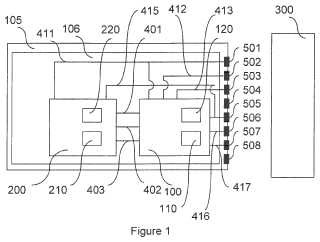

Además, el número de contactos según la norma ISO 7816 está limitada a ocho, cinco de los cuales se utilizan para el protocolo que se ajusta a la norma ISO 7816 (c1, c2, c3, c5, c7) , dos pueden usarse para un protocolo USB de alta velocidad (por ejemplo, c4 y c8) , o tres en el caso de un protocolo MMC, lo que limita la capacidad de evolución de las tarjeta de microprocesador.

La presente invención tiene como objetivo eliminar estos inconvenientes.

A partir de las publicaciones FR 2680262, EP 0779598 y NL 9301540 se conocen tarjetas con múltiples chips en las que se recibe una señal de selección para conmutar medios de conmutación de la tarjeta, de manera que el contacto de E/S de la tarjeta se conecta directamente al chip seleccionado.

En el documento DE 4406704, una unidad de conexión de un microcontrolador decide qué microcontrolador de una tarjeta con múltiples chips va a utilizarse.

Para este fin, un primer aspecto de la presente invención está dirigido a una tarjeta de microprocesador, como se define en la reivindicación 1.

Gracias a estas aportaciones, un lector de tarjeta de microprocesador puede enviar comandos a los dos microprocesadores sin ser necesaria la utilización de contactos adicionales en comparación con la situación en la que solo se controla a un microprocesador. Además, la seguridad del primer y del segundo microprocesador puede certificarse de manera independiente.

Según características particulares, el primer microprocesador está adaptado para ejecutar un primer software de aplicación que determina los comandos de microprocesador que van a transmitirse al segundo microprocesador.

Según características particulares, la tarjeta según la presente invención comprende contactos eléctricos externos destinados a transportar señales de control, estando conectados dichos contactos eléctricos externos solamente al primer microprocesador.

Según características particulares, el primer microprocesador comprende medios para controlar el segundo microprocesador mediante comandos conformes a la norma ISO 7816.

Gracias a estas aportaciones, un lector puede enviar comandos APDU (Application Protocol Data Unit, unidad de datos de protocolo de aplicación) a ambos microprocesadores.

Según características particulares, la tarjeta según la presente invención comprende al menos una línea de entrada/salida según la norma ISO 7816 que conecta los dos microprocesadores y se utiliza para intercambiar información entre los dos microprocesadores.

Según características particulares, una conexión de reloj conecta los dos microprocesadores, suministrando el primer microprocesador al segundo microprocesador, en conformidad con la norma ISO 7816, una señal de reloj en función de una señal de reloj interna al primer microprocesador.

Gracias a estas aportaciones, los dos microprocesadores pueden funcionar con diferentes relojes, por ejemplo sincronizados a diferentes frecuencias.

Según características particulares, el primer microprocesador comprende medios para inhibir dicha señal de reloj suministrada al segundo microprocesador.

Gracias a estas aportaciones, si el segundo microprocesador comprende medios para seleccionar un modo en espera en ausencia de señales de reloj, en particular para economizar la corriente suministrada por el lector, lo que puede ser particularmente crítico cuando el lector está en un objeto portátil alimentado por batería, tal como un teléfono móvil, el primer microprocesador puede ordenar a todo o a parte del segundo microprocesador que pase a un modo en espera.

Según características particulares, el primer microprocesador está adaptado para suministrar una señal de reinicio al segundo microprocesador en conformidad con la norma ISO 7816.

La conexión de señal de reinicio corresponde al contacto c2 de la norma ISO 7816.

Según características particulares, los dos microprocesadores están conectados en paralelo a dos contactos de alimentación enrasados.

Según la norma ISO 7816, el contacto c1 "Vcc" y el contacto c5 "GND" suministran energía a una tarjeta de microprocesador.

Gracias a estas aportaciones, es sencillo suministrar energía a ambos microprocesadores.

Según características particulares, los dos microprocesadores son partes de dos microcircuitos diferentes.

Gracias a estas aportaciones, al menos uno de los dos microprocesadores puede ser un microprocesador ya existente o un microprocesador utilizado de manera independiente, posiblemente solo, en otras tarjetas, lo que permite utilizar un microprocesador que ya esté certificado y/o de menor coste.

Según características particulares, el primer microprocesador utiliza un nivel de seguridad inferior al del segundo microprocesador.

Gracias a estas aportaciones, un lector de tarjeta de microprocesador que implementa solamente el nivel de seguridad del primer microprocesador puede hacer funcionar al primer microprocesador. Además, el segundo microprocesador puede haber aumentado su seguridad porque sus comandos provienen exclusivamente del primer microprocesador.

Los expertos en la materia conocen ampliamente los niveles de seguridad. En particular, los microprocesadores y aplicaciones bancarias se certifican generalmente mediante el procedimiento de criterios comunes (correspondiente a la norma ISO 15408) en un nivel igual o superior al EAL4 (Evaluation Assurance Level 4, nivel 4 de garantía de evaluación) , normalmente en el nivel EAL4+. Por otro lado, los microprocesadores y las aplicaciones de telefonía móvil no se certifican generalmente según los... [Seguir leyendo]

Reivindicaciones:

1. Tarjeta (105, 705) de microprocesador que incluye un primer microprocesador (110) para ejecutar primeras aplicaciones, caracterizada porque dicha tarjeta de microprocesador comprende además un segundo microprocesador (210) para ejecutar segundas aplicaciones, incluyendo dicho primer microprocesador medios para transmitir al segundo microprocesador comandos procedentes desde el exterior (300) de la tarjeta y para transmitir al exterior de la tarjeta respuestas a esos comandos procedentes del segundo microprocesador, estando adaptado el primer microprocesador para utilizar un nivel de capacidad para resistir ataques, fallos o pérdidas de datos inferior al del segundo microprocesador.

2. Tarjeta (105, 705) según la reivindicación 1, en la que el primer microprocesador está adaptado para utilizar un nivel de capacidad para resistir ataques procedentes de partes no autorizadas inferior al del segundo microprocesador.

3. Tarjeta (105, 705) según cualquiera de las reivindicaciones 1 ó 2, en la que el segundo microprocesador proporciona al menos un nivel de seguridad EAL4 (nivel 4 de garantía de evaluación) definido por la norma ISO 15408.

4. Tarjeta (105, 705) según una de las reivindicaciones 1 a 3, caracterizada porque el primer microprocesador está adaptado para ejecutar un primer software (120) de aplicación que determina los comandos de microprocesador que van a transmitirse al segundo microprocesador.

5. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 4, caracterizada porque comprende contactos eléctricos externos (502, 503, 504, 506, 507, 508) destinados a transmitir señales de control, estando conectados dichos contactos eléctricos externos solamente al primer microprocesador.

6. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 5, caracterizada porque el primer microprocesador comprende medios para controlar el segundo microprocesador mediante comandos conformes a la norma ISO 7816.

7. Tarjeta (105, 705) según la reivindicación 6, caracterizada porque comprende al menos una línea (401) de entrada/salida según la norma ISO 7816 que conecta los dos microprocesadores y que se utiliza para intercambiar información entre los dos microprocesadores.

8. Tarjeta (105, 705) según cualquiera de las reivindicaciones 6 ó 7, caracterizada porque una conexión (402) de reloj conecta los dos microprocesadores, suministrando el primer microprocesador al segundo microprocesador, en conformidad con la norma ISO 7816, una señal de reloj en función de una señal de reloj interna al primer microprocesador.

9. Tarjeta (105, 705) según la reivindicación 8, caracterizada porque el primer microprocesador comprende medios para inhibir dicha señal de reloj suministrada al segundo microprocesador.

10. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 6 a 9, caracterizada porque el primer microprocesador está adaptado para suministrar una señal de reinicio (403) al segundo microprocesador en conformidad con la norma ISO 7816.

11. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 10, caracterizada porque los dos microprocesadores están conectados en paralelo a dos contactos de alimentación enrasados.

12. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 11, caracterizada porque los dos microprocesadores son partes de dos microcircuitos diferentes.

13. Tarjeta según una cualquiera de las reivindicaciones 1 a 12, caracterizada porque el primer microprocesador implementa una aplicación de identificación de abonado de red de telefonía móvil.

14. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 13, caracterizada porque el segundo microprocesador implementa una aplicación de pago.

15. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 14, caracterizada porque el segundo microprocesador se ajusta a la norma Europay Mastercard Visa (EMV) .

16. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 15, caracterizada porque el primer microprocesador comprende medios para la comunicación con una interfaz de comunicaciones inalámbricas de un

lector (300) de tarjeta.

17. Tarjeta (105, 705) según la reivindicación 16, caracterizada porque dichos medios de comunicación utilizan un protocolo de cable único (SWP) como el protocolo de comunicaciones.

18. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 17, caracterizada porque el primer microprocesador comprende medios para la comunicación con el exterior de la tarjeta a través de contactos enrasados de la tarjeta.

19. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 18, caracterizada porque el primer microprocesador comprende medios para la comunicación con el exterior de la tarjeta que incluyen una interfaz de comunicaciones inalámbricas.

20. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 19, caracterizada porque el primer microprocesador comprende medios para identificar un comando destinado al primer microprocesador y para identificar un comando destinado al segundo microprocesador.

21. Tarjeta (105, 705) según la reivindicación 20, caracterizada porque los medios de identificación están adaptados para identificar, en cada comando destinado al segundo microprocesador, datos que indican que dicho comando está destinado al segundo microprocesador.

22. Tarjeta (105, 705) según la reivindicación 20, caracterizada porque los medios de identificación están adaptados para conmutar el modo de funcionamiento del primer microprocesador entre:

- un primer modo de funcionamiento en el que todos los comandos procedentes del lector se transmiten por el primer microprocesador al segundo microprocesador, y

- un segundo modo de funcionamiento en el que el primer microprocesador no transmite al segundo microprocesador ningún comando procedente del lector.

23. Procedimiento de comunicación para una tarjeta (105, 705) de microprocesador que incluye un primer microprocesador (110) , incluyendo el procedimiento una etapa de ejecución de una primera aplicación (120) por parte del primer microprocesador, caracterizado porque dicho procedimiento comprende además:

- una etapa (617) en la que el primer microprocesador reenvía a un segundo microprocesador (210) para la ejecución de segundas aplicaciones de la tarjeta un comando procedente del exterior (300) de la tarjeta,

- una etapa (619) en la que el primer microprocesador envía al exterior de la tarjeta una respuesta a un comando procedente del segundo microprocesador,

- una etapa (614) en la que el primer microprocesador procesa comandos recibidos desde el exterior de la tarjeta y una etapa (618) en la que el segundo microprocesador procesa comandos recibidos desde el primer microprocesador, donde el procesamiento por parte del primer microprocesador utiliza un nivel de capacidad para resistir ataques, fallos o pérdidas de datos inferior al del procesamiento por parte del segundo microprocesador.

24. Procedimiento según la reivindicación 23, caracterizado porque comprende además una etapa (610) en la que el primer microprocesador determina, según un primer software de aplicación, los comandos de microprocesador que van a transmitirse al segundo microprocesador.

25. Procedimiento según cualquiera de las reivindicaciones 23 ó 24, caracterizado porque, durante la etapa de transmisión por parte del primer microprocesador al segundo microprocesador, el primer microprocesador controla al segundo microprocesador mediante comandos conformes a la norma ISO 7816.

26. Procedimiento según cualquiera de las reivindicaciones 23 a 25, caracterizado porque comprende una etapa en la que el primer microprocesador suministra al segundo microprocesador, de acuerdo con la norma ISO 7816, una señal (402) de reloj en función de una señal de reloj interna al primer microprocesador.

27. Procedimiento según la reivindicación 26, caracterizado porque comprende una etapa de inhibición (612) de la señal de reloj suministrada al segundo microprocesador en función de comandos recibidos desde el exterior de la tarjeta por el primer microprocesador.

28. Procedimiento según una cualquiera de las reivindicaciones 23 a 27, caracterizado porque comprende una etapa

(606) en la que el primer microprocesador suministra una señal de reinicio al segundo microprocesador según la norma ISO 7816.

29. Procedimiento según una cualquiera de las reivindicaciones 23 a 28, caracterizado porque comprende una etapa en la que el primer microprocesador ejecuta una aplicación de identificación de abonado de red de telefonía móvil.

30. Procedimiento según una cualquiera de las reivindicaciones 23 a 29, caracterizado porque comprende una etapa en la que el segundo microprocesador ejecuta una aplicación de pago.

31. Procedimiento según una cualquiera de las reivindicaciones 23 a 30, caracterizado porque, durante la etapa de transmisión al exterior de la tarjeta, el primer microprocesador utiliza medios para la comunicación con una interfaz de comunicaciones inalámbricas de un lector de tarjeta.

32. Procedimiento según la reivindicación 31, caracterizado porque, durante la etapa de transmisión al exterior de la tarjeta, el primer microprocesador utiliza un protocolo de cable único (SWP) como el protocolo de comunicaciones.

33. Procedimiento según una cualquiera de las reivindicaciones 23 a 32, caracterizado porque durante al menos una etapa de transmisión, el primer microprocesador utiliza al menos un contacto enrasado de la tarjeta para comunicarse con un lector de tarjeta de microprocesador.

34. Procedimiento según una cualquiera de las reivindicaciones 23 a 33, caracterizado porque, durante al menos una etapa de transmisión, el primer microprocesador utiliza medios de comunicación que incluyen una interfaz de comunicaciones inalámbricas.

35. Procedimiento según una cualquiera de las reivindicaciones 23 a 34, caracterizado porque comprende una etapa de identificación de un comando destinado al primer microprocesador y/o de un comando destinado al segundo microprocesador.

36. Procedimiento según la reivindicación 35, caracterizado porque, durante la etapa de identificación, se procesan datos en cada comando destinado al segundo microprocesador y que indican que dicho comando está destinado al segundo microprocesador.

37. Procedimiento según la reivindicación 35, caracterizado porque, durante la etapa de identificación, el modo de funcionamiento del primer microprocesador conmuta entre:

- un primer modo de funcionamiento en el que todos los comandos procedentes del lector se reenvían por el primer microprocesador al segundo microprocesador, y

- un segundo modo de funcionamiento en el que el primer microprocesador no reenvía al segundo microprocesador ningún comando procedente del lector.

38. Lector (300) de tarjeta de microprocesador que incluye medios para la comunicación con un primer microprocesador (110) de una tarjeta (105, 705) , caracterizado porque dichos medios de comunicación están adaptados además para transmitir al primer microprocesador un comando procedente del exterior de la tarjeta y destinado a un segundo microprocesador y para recibir una respuesta a un comando desde el segundo microprocesador a través del primer microprocesador, utilizando dicho lector de tarjeta un nivel de capacidad para resistir ataques, fallos o pérdidas de datos, con una aplicación del primer microprocesador, inferior al utilizado con una aplicación del segundo microprocesador.

39. Lector (300) de tarjeta según la reivindicación 38, caracterizado porque utiliza un nivel de capacidad para resistir ataques procedentes de partes no autorizadas, con una aplicación del primer microprocesador, inferior al utilizado con una aplicación del segundo microprocesador.

40. Lector (300) de tarjeta según cualquiera de las reivindicaciones 38 ó 39, caracterizado porque comprende medios para controlar al segundo microprocesador a través del primer microprocesador mediante comandos conformes a la norma ISO 7816.

41. Lector (300) de tarjeta según cualquiera de las reivindicaciones 38 a 40, caracterizado porque comprende medios para identificar un comando destinado al microprocesador y medios para identificar un comando destinado al segundo microprocesador.

42. Lector (300) de tarjeta según la reivindicación 41, caracterizado porque comprende medios para introducir en cada comando destinado al segundo microprocesador datos que permiten al primer microprocesador detectar que es un comando destinado al segundo microprocesador.

43. Lector (300) de tarjeta según la reivindicación 41, caracterizado porque comprende medios para conmutar el modo de funcionamiento del primer microprocesador entre:

- un primer modo de funcionamiento en el que todos los comandos procedentes del lector se reenvían por el primer microprocesador al segundo microprocesador, y

- un segundo modo de funcionamiento en el que el primer microprocesador no reenvía al segundo microprocesador ningún comando procedente del lector.

44. Lector (300) de tarjeta según una cualquiera de las reivindicaciones 38 a 43, caracterizado porque utiliza junto con el primer microprocesador una aplicación de identificación de abonado de red de telefonía móvil.

45. Lector (300) de tarjeta según una cualquiera de las reivindicaciones 38 a 44, caracterizado porque utiliza junto con el segundo microprocesador una aplicación de pago.

46. Lector (300) de tarjeta según una cualquiera de las reivindicaciones 38 a 45, caracterizado porque comprende medios de comunicaciones inalámbricas para la comunicación con el primer microprocesador.

47. Lector (300) de tarjeta según la reivindicación 46, caracterizado porque dichos medios de comunicación utilizan el protocolo de cable único (SWP) como el protocolo de comunicaciones.

48. Lector (300) de tarjeta según una cualquiera de las reivindicaciones 38 a 47, caracterizado porque comprende medios de comunicaciones inalámbricas para la comunicación con un lector externo.

49. Lector (300) de tarjeta según la reivindicación 48, caracterizado porque los medios de comunicaciones inalámbricas para la comunicación con un lector externo utilizan un protocolo de comunicación de campo cercano.

50. Teléfono móvil (340) , caracterizado porque comprende un lector de tarjeta según una cualquiera de las reivindicaciones 38 a 49.

51. Procedimiento para proporcionar una tarjeta (105, 705) de microprocesador que incluye un primer microprocesador (110) , caracterizado porque dicho procedimiento comprende una etapa de certificación de un segundo microprocesador (210) y una etapa de asociación del primer y del segundo microprocesador en una tarjeta, asociación en la que dicho primer microprocesador comprende medios para reenviar al segundo microprocesador comandos procedentes del exterior (300) de la tarjeta y para transmitir al exterior de la tarjeta respuestas a esos comandos procedentes del segundo microprocesador, en el que el primer microprocesador está adaptado para utilizar un nivel de capacidad para resistir ataques, fallos o pérdidas de datos inferior al del segundo microprocesador.

Patentes similares o relacionadas:

TÚNEL DE ELEVADA VELOCIDAD PARA LECTURA Y CODIFICACIÓN MASIVA DE ETIQUETAS RFID CONTENIDAS EN UN PAQUETE, del 8 de Julio de 2020, de Rielec Automatización Industrial S.L: 1. Túnel de elevada velocidad para lectura y codificación masiva de etiquetas RFID contenidas en un paquete que comprende, al menos: - Medios de transporte por los […]

Un sistema de etiquetas electrónicas de precios, del 1 de Julio de 2020, de MariSense Oy: Un procedimiento para un sistema de etiquetas electrónicas de precios que comprende al menos una estación base y una pluralidad de etiquetas electrónicas […]

Sistema de sellado y método para instalar un sistema de sellado, del 3 de Junio de 2020, de THE EUROPEAN ATOMIC ENERGY COMMUNITY (EURATOM), REPRESENTED BY THE EUROPEAN COMMISSION: Sistema de sellado para contenedores nucleares, que sella una tapa de contenedor de un contenedor nuclear a un cuerpo de contenedor de dicho contenedor nuclear, dicho […]

Seguimiento de posición en eventos deportivos, del 3 de Junio de 2020, de race result AG: Transpondedor móvil para el cronometraje y el seguimiento de ubicación, con: una unidad de recepción para recibir un mensaje […]

Sistema de distribución de contenido para una función de tarjeta sin contacto y método de distribución de contenido para una función de tarjeta sin contacto, del 27 de Mayo de 2020, de NTT DOCOMO, INC.: Sistema para distribuir contenidos para una función de tarjeta de proximidad, que comprende: un aparato de proveedor de información, un primer aparato (1A) de terminal […]

Sistema para el control de la humedad que comprende un paquete humectante relleno con un material humectante que comprende glicerol y agua, del 27 de Mayo de 2020, de Desiccare, Inc: Un sistema para el control de la humedad que comprende: un paquete humectante hecho de un material poroso que es permeable al vapor, pero impermeable a líquido, […]

Sistema RFID para identificación de pajillas criogénicas, del 6 de Mayo de 2020, de Viking Genetics FmbA: Una pajilla criogénica que comprende un sistema de identificación por radiofrecuencia , el sistema de identificación por radiofrecuencia comprende : […]

Antena para etiqueta de identificación y etiqueta de identificación con antena, del 6 de Mayo de 2020, de Datamars S.A: Una etiqueta de identificación de frecuencia ultra alta para acoplarse a un animal, comprendiendo dicha etiqueta de identificación: un cuerpo (12, 14, 112, […]