SISTEMA DE COMPUTADORES TOLERANTE A FALLOS, METODO PARA LA RESINCRONIZACION DEL MISMO Y PROGRAMA PARA SU RESINCRONIZACION.

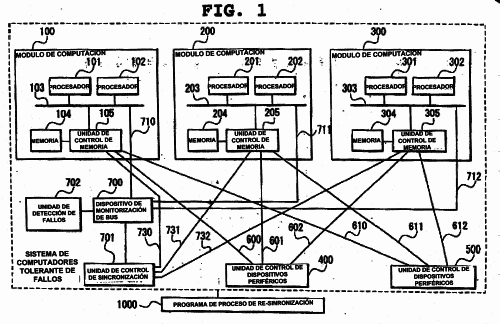

Un sistema de computadores tolerante de fallos con sincronización por paso de bloqueo que incluye una pluralidad de módulos (100,

200, 300) de computación que tienen un procesador (101, 102, 201, 202, 301, 302) y una memoria (104, 204, 304), en el que cada módulo (100, 200, 300) de computación procesa la misma cadena de instrucciones con sincronización entre sí, y que además comprende un detector (702) de fallos que monitoriza la existencia/no existencia de un fallo en todo el sistema, un dispositivo (700) de monitorización de bus que monitoriza un acceso del procesador de cada uno de dichos módulos (100, 200, 300) de computación a un bus (103, 203, 303) externo y cuando detecta discrepancia en la salida entre los respectivos módulos (100, 200, 300) de computación, notifica una interrupción a cada uno de dichos procesadores, y un controlador (701) de sincronización que re- sincroniza cada módulo (100, 200, 300) de computación ajustando la temporización de una respuesta a un acceso desde cada uno de dichos procesadores que es causada por dicha interrupción, caracterizado porque dicho dispositivo (700) de monitorización de bus notifica dicha interrupción a cada uno de dichos procesadores, encolando así una tarea predeterminada que es una tarea que consiste en ejecutar un acceso a un recurso predeterminado en dicho controlador (701) de sincronización, para re-sincronizar los módulos (100, 200, 300) de computación, si dicho detector (702) de fallos no detecta ningún fallo, y porque dicho controlador (701) de sincronización transmite una respuesta a todos los módulos (100, 200, 300) de computación simultáneamente, cuando se reciben accesos a dicho recurso desde todos los procesadores.

Tipo: Resumen de patente/invención.

Solicitante: NEC CORPORATION.

Nacionalidad solicitante: Japón.

Dirección: 7-1, SHIBA 5-CHOME, MINATO-KU,TOKYO.

Inventor/es: AINO, SHIGEYUKI, YAMAZAKI, SHIGEO.

Fecha de Publicación: .

Fecha Concesión Europea: 28 de Septiembre de 2005.

Clasificación Internacional de Patentes:

- G06F11/16 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Detección o corrección de errores en un dato por redundancia en el hardware.

Patentes similares o relacionadas:

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Procedimiento de parada de emergencia y sistema de seguridad asociado, del 20 de Mayo de 2020, de CLEARSY: Procedimiento de parada de emergencia de un elemento de seguridad de un conjunto de seguridad , comprendiendo el conjunto de seguridad […]

Actualización de software de componentes no críticos en sistemas distribuidos críticos para la seguridad dual, del 13 de Mayo de 2020, de Siemens Mobility GmbH: Procedimiento para el funcionamiento de un sistema crítico para la seguridad con al menos un primer dispositivo de datos con un software aprobado y relevante […]

Sistemas críticos de seguridad ferroviaria con redundancia de tareas y capacidad de comunicaciones asimétricas, del 22 de Enero de 2020, de Siemens Mobility, Inc: Sistema de control para un sistema de aplicación crítico de seguridad ferroviaria, que comprende: al menos un controlador, que comprende un procesador […]

Circuito integrado digital protegido contra errores transitorios, del 9 de Octubre de 2019, de THALES: Circuito integrado digital que comprende un conjunto lógico que comprende un bloque lógico funcional, una unidad lógica de detección […]

Circuito de generación de reloj y procedimiento de generación de la señal de reloj, del 12 de Junio de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un circuito de generación de reloj , que comprende una primera fuente de reloj , una segunda fuente de reloj y un circuito de puerta lógica , […]

Sistema informático de seguridad de tipo relevante, del 7 de Mayo de 2019, de Siemens Mobility GmbH: Sistema informático de seguridad de tipo relevante, particularmente un sistema de seguridad ferroviario, con al menos dos canales hardware (A; B), en donde los […]

Método, ordenador y aparato para migrar datos de memoria, del 6 de Marzo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un ordenador, que comprende: un procesador ; un sistema básico de entrada/salida ; una memoria principal , configurada para cargar […]