RED NEURAL PARA RECONOCIMIENTO Y AUTENTIFICACION DE BILLETES DE BANCO.

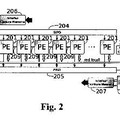

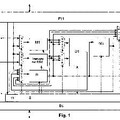

UNA RED NEURONAL PROBABILISTICA (PNN) COMPRENDE UNA CAPA L1 DE NODOS DE ENTRADA,

UNA CAPA L2 DE NODOS DE ORIGINALES, UNA CAPA L3 DE NODOS PRIMARIOS PARZEN, UNA CAPA L4 DE NODOS DE SUMA, Y OPCIONALMENTE UNA CAPA L5 DE NODOS DE SALIDA. CADA NODO DE ORIGINALES DETERMINA EL GRADO DE ADAPTACION ENTRE UN VECTOR ORIGINAL RESPECTIVO Y UN VECTOR DE ENTRADA Y ALIMENTA A UN NODO PARZEN PRIMARIO RESPECTIVO. LOS NODOS DE ORIGINAL Y PARZEN PRIMARIO ESTAN AGRUPADOS EN CLASES DE DISEÑO, CON UN NODO DE SUMA PARA CADA CLASE QUE COMBINA LAS SALIDAS DE LOS NODOS PARZEN PRIMARIOS PARA LA CLASE Y ALIMENTA UN CORRESPONDIENTE NODO DE SALIDA. LA RED INCLUYE PARA CADA NODO PARZEN PRIMARIO (P.EJ. L3-2-3P) PARA LAS CLASES DE DISEÑO UN SEGUNDO NODO PARZEN (L-3-2-3S) SECUNDARIO, TODOS LOS NODOS PARZEN SECUNDARIOS ALIMENTAN UN NODO (L4-0) DE SUMA DE CLASE NULA. CADA NODO PARZEN SECUNDARIO TIENE UNA FUNCION PARZEN CON UNA AMPLITUD DE PICO INFERIOR Y UNA EXTENSION MAS AMPLIA QUE EL CORRESPONDIENTE NODO PARZEN PRIMARIO, Y ES ALIMENTADO DESDE EL NODO DE ORIGINALES POR EL NODO PARZEN PRIMARIO. EL NODO PARZEN SECUNDARIO DETECTA EN EFECTO VECTORES DE ENTRADA QUE SON "SUFICIENTEMENTE DIFERENTES" DE LAS CLASES DE DISEÑO - QUE SON, VECTORES DE CLASE NULA. LA RED ES APLICABLE A RECONOCIMIENTO Y AUTENTIFICACION DE BILLETES, LA CLASE NULA CORRESPONDE A BILLETES FALSIFICADOS.

Tipo: Resumen de patente/invención.

Solicitante: NCR INTERNATIONAL INC..

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 1700 SOUTH PATTERSON BOULEVARD,DAYTON, OHIO 45479.

Inventor/es: ECCLES, NICHOLAS JOHN.

Fecha de Publicación: .

Fecha Concesión Europea: 24 de Marzo de 1999.

Clasificación Internacional de Patentes:

- G06F15/80 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 15/00 Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general. › que comprenden un conjunto de unidades de procesamiento con control común, p. ej. varios procesadores de datos de instrucción única (G06F 15/82 tiene prioridad).

- G07D7/00 G […] › G07 DISPOSITIVOS DE CONTROL. › G07D MANIPULACION DE MONEDAS O DE PAPELES DE VALOR, p. ej. VERIFICACION, CLASIFICACION POR DENOMINACION, CONTEO, DISPENSACION, CAMBIO O DEPOSITO. › Verificación especialmente adaptada a la determinación de la identidad o la autenticidad de papeles de valor o para separar aquellos que son inaceptables, p. ej. billetes o papel moneda extranjeros.

Patentes similares o relacionadas:

Procesador digital de señales y dispositivo de comunicación de banda base, del 5 de Noviembre de 2018, de MediaTek Sweden AB: Una unidad de ejecución de vectores para su uso en un procesador digital de señales que tiene un núcleo de procesador, […]

Procesador digital de señales y método para direccionar una memoria en un procesador digital de señales, del 18 de Octubre de 2017, de MediaTek Sweden AB: Un procesador digital de señales que comprende al menos una unidad funcional, que puede ser una unidad de ejecución de vectores , o un acelerador, […]

Procesador de señal digital y dispositivo de comunicación de banda base, del 16 de Agosto de 2017, de MediaTek Sweden AB: Un procesador de señal digital que comprende: - un núcleo de procesador que incluye una unidad de ejecución de enteros […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]

ARQUITECTURA HÍBRIDA SIMD/MIMD DINÁMICAMENTE RECONFIGURABLE DE UN COPROCESADOR PARA SISTEMAS DE VISIÓN, del 29 de Noviembre de 2012, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), […]

ARQUITECTURA HÍBRIDA SIMD/MIMD DINÁMICAMENTE RECONFIGURABLE DE UN COPROCESADOR PARA SISTEMAS DE VISIÓN, del 29 de Noviembre de 2012, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), […]

Dispositivo de direccionamiento para procesador paralelo, del 15 de Agosto de 2012, de THALES: Procesador paralelo que comprende procesadores elementales que comprenden cada uno al menos unaunidad de cálculo y al menos una memoria que incluye palabras […]

SISTEMA DE PROCESAMIENTO DE DATOS Y DISPOSITIVO DE COMPUTACIÓN, del 12 de Marzo de 2012, de STARLAB BARCELONA SL: Sistema de procesamiento de datos y dispositivo de computación.

El sistema comprende:

- unos dispositivos de computación que procesan en paralelo […]

SISTEMA DE PROCESAMIENTO DE DATOS Y DISPOSITIVO DE COMPUTACIÓN, del 12 de Marzo de 2012, de STARLAB BARCELONA SL: Sistema de procesamiento de datos y dispositivo de computación.

El sistema comprende:

- unos dispositivos de computación que procesan en paralelo […]

REDES NEURONALES., del 1 de Enero de 2004, de BRITISH AEROSPACE: Dispositivo para tratar datos que representan una pluralidad de ejemplos, con lo que se determina una plantilla genérica que representa dichos ejemplos, donde dicho dispositivo […]