PROCEDIMIENTOS Y APARATOS PARA LA CONVERSIÓN ANALÓGICO-DIGITAL.

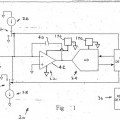

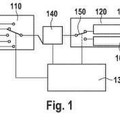

Un circuito (20, 120) para la conversión de analógica a digital (A/D) de una señal de entrada,

incluyendo el circuito (20, 120) un integrador (22), incluyendo el integrador (22) un condensador (40) y un amplificador (42), estando el condensador (40) conectado a una toma de entrada del amplificador (42), un convertidor A/D (24) conectado a una toma de salida del amplificador (42) para proporcionar señales de salida, una fuente (26, 28, 126, 128) de referencia para cambiar una cantidad de carga almacenada en el condensador (40) con una tasa temporal conocida, al menos un conmutador (30, 32, 34, 132, 134, 154, 156) para conectar alternativamente la fuente (26, 28, 126, 128) de referencia y la señal de entrada al condensador (40), y un procesador (38) para controlar sucesivos ciclos de conversión A/D del convertidor A/D (24) y para controlar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156), caracterizado porque el procesador (38) está configurado para sumar las señales de salida del convertidor (A/D) (24) durante los sucesivos ciclos de conversión A/D y dividir las señales de salida sumadas en ciclos sucesivos de conversión A/D por el número de señales de salida sumadas, y porque el amplificador (42) comprende un amplificador (42) de vídeo

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2001/042103.

Solicitante: RADIAN RESEARCH, INC.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 3852 FORTUNE DRIVE LAFAYETTE, IN 47905 ESTADOS UNIDOS DE AMERICA.

Inventor/es: MAYFIELD,GLENN,A.

Fecha de Publicación: .

Fecha Solicitud PCT: 11 de Septiembre de 2001.

Clasificación Internacional de Patentes:

- H03M1/10C1M

Clasificación PCT:

- H03M1/10 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 1/00 Conversión analógica/digital; Conversión digital/analógica (conversión de valores analógicos en, o a partir de una modulación diferencial H03M 3/00). › Calibración o ensayos.

Clasificación antigua:

- H03M1/12 H03M 1/00 […] › Convertidores analógico/digitales (H03M 1/02 - H03M 1/10 tienen prioridad).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

PDF original: ES-2356520_T3.pdf

Fragmento de la descripción:

Campo de la invención

La presente invención versa acerca de convertidores analógico/digitales. Se da a conocer en el contexto de los convertidores analógico/digitales para su uso en instrumentos de medición de la potencia. Sin embargo, se cree que también es útil en otras aplicaciones. 5

Antecedentes de la invención

Existen muchas variaciones en las técnicas de conversión analógico/digitales (en lo sucesivo a veces A/D). La mayoría de las implementaciones pueden agruparse en una de seis categorías. Estas son de aproximaciones sucesivas, de flash, de tensión-frecuencia, de doble pendiente, de equilibrio de carga y delta-sigma.

Los convertidores de aproximaciones sucesivas emplean generalmente un circuito de muestreo y retención, un 10 comparador, un convertidor digital/analógico y alguna lógica de control. La señal de entrada en capturada en primer lugar por el circuito de muestreo y retención y luego se ejecuta un patrón de búsqueda usando un patrón de búsqueda usando el convertidor digital/analógico y el comparador. Para la optimización de la velocidad, el patrón de búsqueda es normalmente de un tipo binomial. La señal de entrada se gradúa para que esté en algún punto dentro del intervalo de la salida del convertidor digital/analógico. En el patrón de búsqueda binomial, el convertidor 15 digital/analógico está configurado a media escala y se usa el comparador para determinar si la señal de entrada capturada es mayor o menor que la salida del convertidor digital/analógico. Esto elimina la mitad de los resultados posible y determina así el bit más significativo de la conversión. El convertidor digital/analógico es reconfigurado entonces para que divida por la mitad el intervalo de tensión restante, y vuelve a usarse el comparador para determinar en qué mitad reside la tensión de entrada. Esto determina el siguiente bit más significativo. El proceso se 20 repite hasta que se logra el número de bits requeridos. Un convertidor de doce bits requiere doce comparaciones tales.

Los convertidores de flash hacen uso de una escalera divisora, múltiples comparadores y lógica de decodificación para llevar a cabo la conversión A/D. Existen tantos comparadores y tomas en la escalera divisora como códigos en el convertidor A/D. Un convertidor de 8 bits requiere 256 comparadores y 256 tomas en el divisor. Un convertidor de 25 12 bits, si se produjera, requeriría el valor pasmoso de 4096. A continuación, los comparadores comparan la señal entrante con sus respectivas tensiones de toma. Los comparadores con tensiones de toma por encima de la tensión de entrada adoptan un primer estado. Los que tienen tensiones de toma por debajo de la tensión de entrada adoptan un segundo estado. Las salidas de todos los comparadores se suministran a la lógica de decodificación para crear la salida. Dado que llevan a cabo todas las comparaciones de una vez, los convertidores de flash son generalmente 30 considerados los más rápidos de estos seis tipos de convertidores A/D.

Los convertidores de doble pendiente son una forma de convertidor integrador. Funcionan midiendo la carga acumulada en un condensador. Si no es ya una corriente, la señal de entrada es convertida en una corriente y es aplicada a un condensador descargado durante un periodo fijo de tiempo. Se usa con frecuencia un circuito integrador basado en un amplificador operacional, en lo sucesivo amp op, para proporcionar un régimen sumamente 35 bajo a la fuente de corriente de entrada. Puesto que la corriente multiplicada por el tiempo es la carga y dado que el tiempo de carga está fijado, la carga que se pone en el condensador es proporcional a la corriente media de entrada. Cuando se aplica la carga, la tensión del condensador se incrementa. Esta es la primera pendiente a la que se refiere el nombre de convertidor de doble pendiente. A continuación, se lleva a cabo la segunda etapa de medición de esta carga. Para medir la carga acumulada, se pone término al proceso de carga y se aplica una corriente 40 calibrada de descarga. Se mide el tiempo requerido para devolver el condensador al estado descargado. Al eliminarse la carga, la tensión entre los extremos del condensador vuelve a descender hasta cero. Cuando la tensión del condensador vuelve a cero, se ha eliminado exactamente la cantidad de carga que resultó de la corriente de entrada. Esta es la segunda pendiente a la que se refiere el nombre de doble pendiente. Puesto que se conocen tanto la corriente aplicada de descarga como el tiempo que se aplicó, también se conoce la carga que se eliminó del 45 condensador y, por lo tanto, la carga que se acumuló en el condensador resultante de la señal de entrada. Si esta carga se divide a continuación por el tiempo requerida para que la corriente de entrada lo cargara, se calcula la corriente media de entrada para el periodo de la medición.

Un convertidor de equilibrio de carga es otra forma de convertidor integrador. Los convertidores de equilibrio de carga son similares a los convertidores de doble pendiente, porque la señal de entrada al convertidor de equilibrio de 50 carga es una corriente o se convierte en una corriente, y se mide la carga que se está acumulando en un condensador. Difieren fundamentalmente en cómo se mide y se elimina la carga. En un convertidor de equilibrio de carga, la carga se acumula continuamente en el condensador mientras se elimina simultáneamente en cuantos discretos. La tensión entre los extremos del condensador se mide periódicamente. Si se ha acumulado suficiente carga, se elimina un paquete de carga. Esto se logra normalmente aplicando una corriente calibrada durante un 55 periodo de tiempo específico. Para cada periodo de muestro cuando se elimina un paquete de carga, el convertidor produce un impulso. Si no se elimina carga durante el periodo de muestreo, no se produce ningún impulso. Cuando están presentes, los impulsos aparecen en límites periódicos. Entonces se mide la frecuencia de los impulsos para completar la conversión.

Un convertidor de tensión-frecuencia es otra forma de convertidor integrador. Los convertidores de tensión-frecuencia son similares a los convertidores de doble pendiente y de equilibrio de carga, porque la entrada es una corriente o se convierte en una corriente a partir de una tensión y se mide la carga acumulada en el condensador. Difieren de los convertidores de doble pendiente y de equilibrio de carga en cómo se elimina la carga. Como en los convertidores de equilibrio de carga, en los convertidores de tensión-frecuencia la carga es eliminada en cuantos 5 discretos. A diferencia de los convertidores de equilibrio de carga, los convertidores de tensión-frecuencia eliminan la carga siempre que se ha acumulado un cuanto o paquete completo. Así, en los convertidores tensión-frecuencia, la carga no se elimina en límites periódicos. Esto hace que el convertidor proporcione una frecuencia de salida que es proporcional a la corriente aplicada de entrada. La familia LM131 de National Semiconductor de convertidores de tensión-frecuencia es un buen ejemplo de este tipo de convertidor A/D. 10

El convertidor delta-sigma es otra forma adicional de convertidor integrador. Los convertidores delta-sigma son una forma altamente especializada de convertidor de equilibrio de carga, pero aquí los presentamos aparte. El convertidor delta-sigma puede ser considerado como dos componentes: un modulador y un filtro digital. El modulador contiene la porción integradora del convertidor y una porción de eliminación de carga. El modulador funciona efectivamente como un digitalizador de 1 bit de muy alta velocidad, con un espectro de ruido del todo 15 excepcional. Este digitalizador de 1 bit muestrea a una frecuencia que es varios órdenes de magnitud más elevada que la banda de la frecuencia de interés. Debido a su construcción excepcional. El espectro de ruido que produce está distribuido de manera no uniforme y el grueso de la energía acústica está fuera de la banda de frecuencias de interés. Así, mediante el debido filtrado, puede eliminarse gran parte de este ruido. Esta es una función realizada por el filtro digital. El modulador es interesante porque puede llevar a cabo la conversión tensión-corriente como parte 20 inherente de su función y, así, desde la perspectiva del usuario, la entrada el convertidor es normalmente una tensión en vez de una corriente. El filtro digital realiza dos funciones. Funciona como una versión muy sofisticada del contador en el convertidor de equilibrio de carga, así como un filtro digital para extraer un resultado de resolución más alta a una tasa de datos inferior a la del digitalizador de 1 bit.

La medición... [Seguir leyendo]

Reivindicaciones:

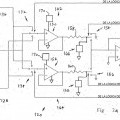

1. Un circuito (20, 120) para la conversión de analógica a digital (A/D) de una señal de entrada, incluyendo el circuito (20, 120) un integrador (22), incluyendo el integrador (22) un condensador (40) y un amplificador (42), estando el condensador (40) conectado a una toma de entrada del amplificador (42), un convertidor A/D (24) conectado a una toma de salida del amplificador (42) para proporcionar señales de salida, una fuente (26, 28, 126, 128) de referencia para cambiar una cantidad de carga almacenada en el condensador (40) con una tasa 5 temporal conocida, al menos un conmutador (30, 32, 34, 132, 134, 154, 156) para conectar alternativamente la fuente (26, 28, 126, 128) de referencia y la señal de entrada al condensador (40), y un procesador (38) para controlar sucesivos ciclos de conversión A/D del convertidor A/D (24) y para controlar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156), caracterizado porque el procesador (38) está configurado para sumar las señales de salida del convertidor (A/D) (24) durante los sucesivos ciclos de conversión A/D y dividir 10 las señales de salida sumadas en ciclos sucesivos de conversión A/D por el número de señales de salida sumadas, y porque el amplificador (42) comprende un amplificador (42) de vídeo.

2. El circuito de la reivindicación 1 en el que el procesador (38) está configurado para sumar las señales de salida de dos ciclos consecutivos y dividir por dos.

3. El circuito de la reivindicación 1 en el que el procesador (38) está configurado para sumar las señales de salida 15 de cuatro ciclos consecutivos y dividir por cuatro.

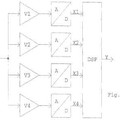

4. El circuito de la reivindicación 1 en el que el amplificador (42) de vídeo comprende múltiples amplificadores (42) en configuración de cascada.

5. El circuito de la reivindicación 4 en el que los múltiples amplificadores (42) incluyen múltiples amplificadores (42) de vídeo. 20

6. El circuito de cualquier reivindicación precedente en el que el procesador (38) está configurado para controlar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) para proporcionar carga al integrador (22) y para controlar el convertidor A/D (24) para la conversión A/D de una señal de salida del integrador antes y después de la aplicación de la carga.

7. El circuito de la reivindicación 6 que además incluye un generador (36) de base de tiempos conectado al 25 procesador (38), estando configurado el procesador (38) para accionar periódicamente el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) para eliminar periódicamente la señal de entrada del integrador (22), conectar periódicamente la fuente (26, 28, 126, 128) de referencia al integrador (22) y proporcionar periódicamente carga al integrador (22), estando configurado el convertidor A/D (24) para la conversión A/D de la señal de salida del integrador antes y después de la aplicación periódica de carga al integrador (22). 30

8. El circuito de la reivindicación 6 en el que el procesador (38) está configurado para determinar, a partir de la señal de salida del integrador con conversión A/D, antes y después de la introducción de carga, una capacidad efectiva de la combinación del integrador (22) y del convertidor A/D (24).

9. El circuito de la reivindicación 8 en el que se conoce un coeficiente de temperatura del condensador (40), estando configurado el procesador (38) para determinar un cambio en la capacidad efectiva de la combinación 35 del integrador (22) y del convertidor A/D (24) y determinar, a partir del cambio en la capacidad efectiva de la combinación del integrador (22) y del convertidor A/D (24) y el coeficiente de temperatura del condensador (40), la temperatura del condensador (40).

10. El circuito de cualquier reivindicación precedente en el que el integrador (22) que incluye el condensador (40) y el amplificador (42) incluye un primer integrador (22) que incluye un primer condensador (40) y un primer 40 amplificador (42) y un segundo integrador (22) que incluye un segundo condensador (40) y un segundo amplificador (42), estando orientados de tal modo los condensadores (40) primero y segundo que sus temperaturas permanecen sustancialmente iguales durante la operación del circuito, estando configurado el procesador (38) para determinar, a partir de la señal de salida del primer integrador (22) con conversión A/D, antes y después de la introducción de la carga, una capacidad efectiva de la combinación del primer integrador 45 (22) y del convertidor A/D (24).

11. El circuito de la reivindicación 1 en el que la fuente (26, 28, 126, 128) de referencia incluye una primera fuente (26, 126) de referencia y una segunda fuente (28, 128) de referencia, incluyendo el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) al menos un primer conmutador (30, 32, 132) para desconectar selectivamente la señal de entrada del integrador (22) y conectar la primera fuente (26, 126) de referencia al integrador (22) y 50 al menos un segundo conmutador (30, 34, 134) para conectar selectivamente la segunda fuente (28, 128) de referencia al integrador (22), estando configurado el procesador (38) para controlar el al menos primer conmutador (30, 32, 132) para proporcionar una primera carga al integrador (22), controlar el convertidor A/D (24) para la conversión A/D de la señal de salida del integrador después de la introducción de la primera carga, controlar el al menos segundo conmutador (30, 34, 134) para retirar del integrador (22) una segunda carga 55

calculada para que sea igual a la primera carga, y controlar el convertidor A/D (24) para la conversión A/D de la señal de salida del integrador después de retirar del integrador (22) la segunda carga.

12. El circuito de la reivindicación 1 en el que el al menos un interruptor (30, 32, 34, 132, 134, 154, 156) incluye además al menos un primer conmutador (30, 32, 132) para desconectar selectivamente la señal de entrada del integrador (22) y descargar el integrador (22), estando configurado el procesador (38) para controlar el 5 convertidor A/D (24) para la conversión A/D de la señal de salida del integrador después de que el integrador (22) se descarga y calcular una corriente de polarización del amplificador (42) a partir de la señal de salida del convertidor A/D (24) después de que el integrador (22) se ha descargado.

13. El circuito de la reivindicación 1 que incluye un generador (36) de base de tiempos conectado al procesador (38), estando configurado el procesador (38) además para controlar el convertidor A/D (24) para controlar la 10 conversión A/D de la señal de salida del integrador después de que el condensador (40) del integrador (22) se carga para determinar la fuga del condensador (40) del integrador (22).

14. El circuito de la reivindicación 1 en el que el procesador (38) está configurado para controlar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) para proporcionar una carga conocida al integrador (22), controlando el procesador (38) además el convertidor A/D (24) para controlar la conversión A/D de la señal de 15 salida del integrador antes y después de la introducción de la carga, incluyendo el procesador (38) una tabla de valores para compensar la señal de salida del integrador (22) con conversión A/D en una diferencia entre la señal de salida del integrador con conversión A/D y la carga conocida.

15. El circuito de la reivindicación 1 en el que el procesador (38) está configurado para accionar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) un número menor de veces para cargar el condensador (40) hasta 20 un valor calculado, estando configurado el convertidor A/D (24) para la conversión A/D de una primera señal de salida del integrador (22), estando configurado el procesador (38) para accionar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) un número mayor de veces que el número menor de veces para cargar el condensador (40) hasta el valor calculado, estando configurado el convertidor A/D (24) para la conversión A/D de una segunda señal de salida del integrador (22), estando configurado el procesador (38) para determinar una 25 diferencia entre la primera señal de salida con conversión A/D y la segunda señal de salida con conversión A/D, dividir la diferencia entre la primera señal de salida con conversión A/D y la segunda señal de salida con conversión A/D por la diferencia entre el número mayor y el número menor; y almacenar un cociente de la división de la diferencia entre la primera señal de salida con conversión A/D y la segunda señal de salida con conversión A/D por la diferencia entre el número mayor y el número menor. 30

16. El circuito de la reivindicación 15 en el que el procesador (38), para accionar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) el número menor de veces para cargar el condensador (40) hasta el valor calculado, está configurado para accionar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) una vez para cargar el condensador (40) hasta el valor calculado.

17. El circuito de la reivindicación 15 en el que el procesador (38), para accionar el al menos un conmutador (30, 32, 35 34, 132, 134, 154, 156) el número mayor de veces para cargar el condensador (40) hasta el valor calculado, está configurado para accionar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) el mayor número de veces, que es, al menos, cien veces el menor número de veces.

18. El circuito de la reivindicación 1 en el que la fuente (26, 28, 126, 128) de referencia incluye una primera fuente (26, 126) de referencia para cambiar la cantidad de carga almacenada en el condensador (40) con una primera 40 tasa temporal conocida y una segunda fuente (28, 128) de referencia para cambiar la cantidad de carga almacenada en el condensador (40) con una segunda tasa temporal conocida, conectando selectivamente el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) la primera fuente (26, 126) de referencia al integrador (22) para cargar el condensador (40) una primera cantidad conocida y desconectando la segunda fuente (28, 128) de referencia del integrador (22) y desconectando la primera fuente (26, 126) de referencia del integrador 45 (22) y conectando la segunda fuente (28, 128) de referencia al integrador (22) para cargar el condensador (40) una segunda cantidad conocida, estando configurado el procesador (38) para comparar las cantidades conocidas primera y segunda para calibrar la segunda fuente (28, 128) de referencia con respecto a la primera fuente (26, 126) de referencia.

19. El circuito de la reivindicación 18 en el que la primera fuente (26, 126) de referencia tiene una primera polaridad, 50 y la segunda fuente (28, 128) de referencia tiene una segunda polaridad opuesta, incluyendo la carga del condensador (40) hasta la segunda cantidad conocida la descarga de la primera cantidad conocida del condensador (40).

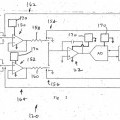

20. El circuito de la reivindicación 1 en el que el integrador (22) comprende un primer integrador (22), incluyendo el primer integrador (22) un primer condensador (40) y un primer amplificador (42), estando conectado el primer 55 condensador (40) a una toma de entrada del primer amplificador (42), el convertidor A/D (24) comprende un primer convertidor A/D (24), incluyendo además el circuito (20, 120) un segundo integrador (22) que incluye un segundo condensador (40) y un segundo amplificador (42), estando conectado el segundo condensador (40) a

una toma de entrada del segundo amplificador (42), y un segundo convertidor A/D (24), conectando selectivamente el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) la fuente (26, 28, 126, 128) de referencia al primer integrador (22) o al segundo integrador (22), estando configurado el procesador (38) para controlar un ciclo de conversión A/D del convertidor A/D (24) para controlar el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) y para controlar un primer ciclo de conversión A/D del primer convertidor A/D (24) para 5 producir una señal de salida del primer convertidor A/D (24) y para controlar un segundo ciclo de conversión A/D del segundo convertidor A/D (24) para producir una señal de salida del segundo convertidor A/D (24).

21. El circuito de la reivindicación 1 en el que la señal de entrada comprende una señal de corriente de entrada y la fuente (26, 28, 126, 128) de referencia comprende una fuente (26, 28) de referencia de corriente.

22. El circuito de la reivindicación 1 en el que la señal de entrada comprende una señal de tensión de entrada y que 10 además incluye un segundo amplificador (150, 152) y una resistencia (158, 160) para convertir la señal de tensión de entrada en una señal equivalente de corriente de entrada.

23. El circuito de la reivindicación 22 en el que la fuente de referencia incluye una primera fuente (126) de referencia de tensión para cambiar la cantidad de carga almacenada en el condensador (40) con una primera tasa temporal conocida y una segunda fuente (128) de referencia de tensión para cambiar la cantidad de carga 15 almacenada en el condensador (40) con una segunda tasa temporal conocida, conectando selectivamente el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) la primera fuente (126) de referencia de tensión al integrador (22) para cargar el condensador (40) hasta una primera cantidad conocida y desconectando la segunda fuente (128) de referencia de tensión del integrador (22), y desconectando la primera fuente (126) de referencia de tensión del integrador (22) y conectando la segunda fuente (128) de referencia de tensión al 20 integrador (22) para cargar el condensador (40) hasta una segunda cantidad conocida.

24. El circuito de la reivindicación 23 en el que el segundo amplificador (150, 152) y la resistencia (158, 160) para convertir la señal de tensión de entrada en una señal equivalente de corriente de entrada incluye un segundo amplificador (150) y una primera resistencia (158) para convertir una de entre la señal de tensión de entrada, la primera fuente (126) de referencia de tensión y la segunda fuente (128) de referencia de tensión en una primera 25 señal equivalente de corriente de entrada, y un tercer amplificador (152) y una segunda resistencia (160) para convertir una de entre la señal de tensión de entrada, la primera fuente (126) de referencia de tensión y la segunda fuente (128) de referencia de tensión en una segunda señal equivalente de corriente de entrada, estando configurado el procesador (38) para controlar un ciclo de conversión A/D del convertidor A/D (24) para conectar alternativamente dicha una de entre la señal de tensión de entrada, la primera fuente (126) de 30 referencia de tensión y la segunda fuente (128) de referencia de tensión por medio del segundo amplificador (150) para producir una señal de salida del primer convertidor A/D (24) y por medio del tercer amplificador (152) para producir una señal de salida del segundo convertidor A/D (24), y promediar la señal de salida del primer convertidor A/D (24) y la señal de salida del segundo convertidor A/D (24).

25. El circuito de la reivindicación 24 en el que el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) incluye 35 al menos un primer conmutador (30, 132, 134) que tiene una posición en la que no hay presente ninguna señal de entrada, estando configurado el procesador (38) para almacenar la señal de salida del convertidor A/D (24) cuando el al menos primer conmutador (30, 132, 134) está en la posición en la cual no hay presente ninguna señal de entrada.

26. El circuito de las reivindicaciones 23 o 24 en el que la primera fuente (126) de referencia tiene una primera 40 polaridad y la segunda fuente (128) de referencia tiene una segunda polaridad opuesta, incluyendo la carga del condensador (40) hasta la segunda cantidad conocida la descarga de la primera cantidad conocida del condensador (40).

27. El circuito de la reivindicación 22 en el que el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) incluye un primer conmutador (132, 134) para conectar alternativamente la fuente (126, 128) de referencia y la señal de 45 entrada al segundo amplificador (150, 152), y un segundo conmutador (154, 156) para conectar y desconectar alternativamente el segundo amplificador (150, 152) al condensador (40), teniendo el segundo conmutador (154, 156) una primera resistencia (158, 160), incluyendo además el aparato un dispositivo (166, 168) de resistencia negativa que tiene una segunda resistencia cuya magnitud es sustancialmente una magnitud de la primera resistencia (158, 160) para conectarla en circuito con la primera resistencia (158, 160). 50

28. El circuito de la reivindicación 1 en el que el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) incluye al menos un primer conmutador (30, 132, 134) que tiene una posición en la que no hay presente ninguna señal de entrada, estando configurado el procesador (38) para almacenar la señal de salida del convertidor A/D (24) cuando el al menos primer conmutador (30, 132, 134) está en la posición en la cual no hay presente ninguna señal de entrada. 55

29. El circuito de la reivindicación 1 que además incluye una fuente (170) de alimentación para proporcionar energía para al menos uno de entre el integrador (22), el convertidor A/D (24), la fuente (26, 28, 126, 128) de referencia, el al menos un conmutador (30, 32, 34, 132, 134, 154, 156) y el procesador (38), generando la fuente (170) de

alimentación señales periódicas durante su funcionamiento, estando configurado el procesador (38) para sincronizar el ciclo de conversión A/D y las señales periódicas para que el efecto de las señales periódicas en la señal de salida del convertidor A/D (24) sea sustancialmente constante.

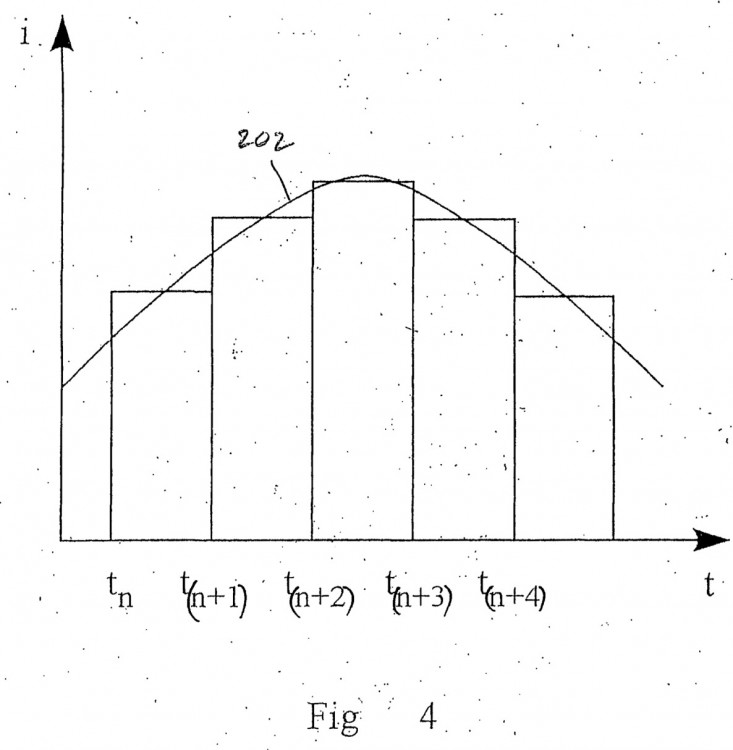

30. El circuito de la reivindicación 1 en el que el procesador (38) para controlar el ciclo de conversión A/D del convertidor A/D (24) está configurado para ajustar la señal de salida del convertidor A/D (24) durante un ciclo de 5 conversión A/D en una cantidad relacionada con la señal de salida del convertidor A/D (24) durante al menos un ciclo precedente de conversión A/D y con la señal de salida del convertidor A/D (24) durante al menos un ciclo sucesivo de conversión A/D.

31. El circuito de la reivindicación 30 en el que el procesador (38) está configurado para ajustar la señal de salida del convertidor A/D (24) durante un ciclo de conversión A/D en una cantidad relacionada con la señal de salida 10 del convertidor A/D (24) durante al menos el ciclo de conversión A/D inmediatamente anterior y con la señal de salida del convertidor A/D (24) durante al menos el ciclo de conversión A/D inmediatamente posterior.

32. El circuito de la reivindicación 30 en el que el procesador (38) está configurado para ajustar la señal de salida del convertidor A/D (24) durante un ciclo de conversión A/D en una cantidad relacionada con la señal de salida del convertidor A/D (24) durante al menos los dos ciclos de conversión A/D inmediatamente anteriores y con la 15 señal de salida del convertidor A/D (24) durante al menos los dos ciclos de conversión A/D inmediatamente posteriores.

Patentes similares o relacionadas:

Compensación de deriva, del 20 de Noviembre de 2019, de Teledyne Signal Processing Devices Sweden AB: Un método asociado a un diseño de circuito eléctrico predefinido, en donde cada circuito eléctrico fabricado de acuerdo con el diseño de circuito […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal, del 1 de Agosto de 2013, de ROBERT BOSCH GMBH: Procedimiento para la corrección de un error de offset de un convertidor de señal , en donde elprocedimiento presenta los siguientes […]

Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal, del 1 de Agosto de 2013, de ROBERT BOSCH GMBH: Procedimiento para la corrección de un error de offset de un convertidor de señal , en donde elprocedimiento presenta los siguientes […]

PROCEDIMIENTO ADAPTATIVO DE CALIBRACIÓN DÍGITAL CONCURRENTE DEL OFFSET EN COMPARADORES EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS), del 18 de Diciembre de 2012, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): El objeto de la presente invención es un procedimiento adaptativo para la calibración del offset de comparadores en convertidores analógico-digitales […]

PROCEDIMIENTO ADAPTATIVO PARA LA ESTIMACIÓN DE LA INL EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS), del 3 de Diciembre de 2012, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): Procedimiento adaptativo para la estimación de la INL en convertidores analógico-digitales (ADCs). Permite caracterizar y testar los convertidores analógico-digitales mediante […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

CIRCUITO MULTIPLICADOR DE UN UNICO BIT CON FUNCION DE AJUSTE DE FASE, del 8 de Abril de 2011, de OSAKI ELECTRIC CO., LTD: Circuito multiplicador de un único bit con función de ajuste de fase.Aumenta la resolución del ajuste de fase. Incluye un elemento aritmético […]

EMPAREJAMIENTO DINAMICO DE ELEMENTOS PARA CONVERTIDORES A/D., del 16 de Marzo de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON: Un método para un emparejamiento dinámico de elementos para un subconvertidor D/A de una etapa de convertidor A/D, caracterizado porque en ese dicho método se incluye el paso […]