Procedimiento para la verificación de al menos una unidad de cálculo integrada en un aparato de control.

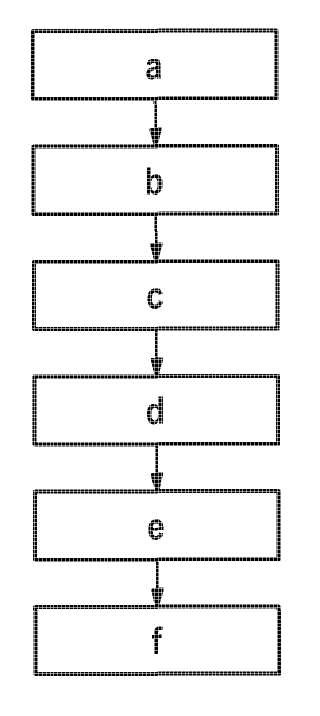

Procedimiento para la verificación de unidades de cálculo (2, 3) incorporadas en un aparato de control,presentando el aparato de control una interfaz de aparato de control, al menos dos unidades de cálculo (2, 3), quepresentan, respectivamente, una cadena de escaneo (4, 5) y al menos dos unidades de memoria (6, 7), con lasetapas:

a) carga de primeros datos de ensayo por medio de la interfaz de aparatos de control para la verificación deuna primera unidad de cálculo (2);

b) registro en memoria de los primeros datos de ensayo cargados en una segunda unidad de memoria (7) deuna segunda unidad de cálculo (3);

c) conmutación de la primera unidad de cálculo (2) a un modo de ensayo, en el que una primera cadena deescaneo (4) de la primera unidad de cálculo (2) es accesible, por medio de la segunda unidad de cálculo(3);

d) lectura de los primeros datos de ensayo desde la segunda unidad de cálculo (7) por medio de la segundaunidad de cálculo (3);

e) desplazamiento de los primeros datos de ensayo leídos a través de la primera cadena de escaneo (4) a laprimera unidad de cálculo (2) conmutada al modo de ensayo, por medio de la segunda unidad de cálculo(3) para la preparación de datos de resultados de ensayo para la primera unidad de cálculo (2);

f) verificación de la verosimilitud de los datos de resultados de ensayo acondicionados por medio de lasegunda unidad de cálculo (3) para la preparación de un resultado de ensayo para la primera unidad decálculo (2);

g) carga de segundos datos de ensayo para la verificación de la segunda unidad de cálculo (3), en el que lossegundos datos de ensayo son cargados por medio de la interfaz de aparatos de control o los primerosdatos de ensayo registrados en la segunda unidad de memoria (7) son cargados como segundos datos deensayo a través de una interfaz interna del aparato de control (1);

h) registro en memoria de los segundos datos de ensayo cargados en una primera unidad de memoria (6) dela primera unidad de cálculo (2);

i) conmutación de la segunda unidad de cálculo (3) a un modo de ensayo, en el que una segunda cadena deescaneo (5) de la segunda unidad de cálculo (3) es accesible, por medio de la primera unidad de cálculo(2);

j) lectura de los segundos datos de ensayo desde la primera unidad de memoria (6) por medio de la primeraunidad de cálculo (2);

k) desplazamiento de los segundos datos de ensayo leídos a través de la segunda cadena de escaneo (5) dela segunda unidad de cálculo (3) conmutada al modo de ensayo por medio de la primera unidad de cálculo(2) para la preparación de datos de resultados de ensayo para la segunda unidad de cálculo (5); y

l) verificación de factibilidad de los datos de resultados de ensayo acondicionados por medio de la primeraunidad de cálculo (2) para la preparación de un resultado de ensayo para la segunda unidad de cálculo (3).

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2007/051802.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20 70442 STUTTGART ALEMANIA.

Inventor/es: AUE,AXEL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F11/267 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Reconfiguración para pruebas, p. ej. LSSD, partición.

PDF original: ES-2444371_T3.pdf

Fragmento de la descripción:

Procedimiento para la verificación de al menos una unidad de cálculo integrada en un aparato de control

Estado de la técnica

La presente invención se refiere a un procedimiento para la verificación de al menos una unidad de cálculo incorporada en un aparato de control, en el que el aparato de control está incorporado especialmente en un automóvil.

El aparato técnico de la invención se refiere a la verificación de circuitos integrados, en particular su unidad de cálculo o unidades de cálculo. A continuación se utilizan de forma similar una unidad de cálculo, un mecanismo de cálculo, un dispositivo de cálculo y un núcleo digital y se designan de la misma manera.

Se conoce verificar circuitos integrados o bien su mecanismo de cálculo o mecanismos de cálculo en un estado no montado. A este respecto, estado no motado significa que el circuito integrado o bien el mecanismo de cálculo o los mecanismos de cálculo no están montados o incorporados, en particular todavía no en un aparato de control, en un dispositivo de control o similar. Esta verificación es realizada especialmente por el fabricante de semiconductores del circuito integrado. Ejemplos de tales ensayos son el llamado ensayo-Stuck-At y el ensayo-Path-Delay. Por medio del ensayo Stuck-At se verifica un cortocircuito potencial de una señal después de la tensión de alimentación o masa, por ejemplo en una cadena de escaneo o en una trayectoria de escaneo de la unidad de cálculo correspondiente. Por medio del ensayo-Path-Delay se verifican los tiempos de propagación de las señales por ejemplo a través de las cadenas de escaneo o de las trayectorias de escaneo. Descripciones detalladas del ensayo-Stuck-At y del ensayoPath-Delay se conocen a partir del documento EP 0548585 A2.

Se conoce a partir del documento US 2004/064 757 A1 otro procedimiento para la verificación de un aparato de control.

El procedimiento de acuerdo con la invención para la verificación de una unidad de cálculo incorporada al menos en un aparato de control con las características de la reivindicación 1 presenta frente a los principios de solución conocidos la ventaja de que también se pueden verificar unidades de cálculo en un estado montado o incorporado y en particular también en el aparato de control cerrado. De esta manera es posible de acuerdo con la invención verificar una unidad de cálculo o varias unidades de cálculo de un aparato de control, que está montado, por ejemplo, en un lugar discrecional de un automóvil. En particular, de acuerdo con la invención, en el aparato de control montado se pueden realizar el ensayo-Stuck-At y el ensayo-Path-Delay.

A través del procedimiento de acuerdo con la invención se asegura, por lo tanto, que el aparato de control y en particular sus unidades de cálculo se puedan verificar después de esfuerzo de tensión o después de la utilización de la misma manera (y, por lo tanto, con buena cobertura de ensayo comparativamente similar) como en el fabricante correspondiente de semiconductores. De ello resulta especialmente una capacidad de análisis mejorada de retornos de campo. En particular, se eleva la probabilidad de que un fallo determinado, que podría encontrarse por el fabricante de semiconductores en el estado no montado, no se encentra en el estado montado.

La idea en la que se basa la presente invención consiste esencialmente en preparar un procedimiento con las siguientes etapas para la verificación de al menos una unidad de cálculo incorporada en un aparato de control, presentando el aparato de control una interfaz de aparato de control, al menos dos unidades de cálculo, que presentan, respectivamente, una cadena de escaneo (o bien el comienzo de un circuito, que interconecta las cadenas de escaneo internas) , y presenta al menos una unidad de memoria:

- carga de primeros datos de ensayo por medio de la interfaz de aparatos de control para la verificación de una primera unidad de cálculo;

- registro en memoria de los primeros datos de ensayo cargados en una segunda unidad de memoria de una segunda unidad de cálculo;

- conmutación de la primera unidad de cálculo aun modo de ensayo, en el que una primera cadena de escaneo de la primera unidad de cálculo es accesible, por medio de la segunda unidad de cálculo;

- lectura de los primeros datos de ensayo desde la segunda unidad de cálculo por medio de la segunda unidad de cálculo;

- desplazamiento de los primeros datos de ensayo leídos a través de la primera cadena de escaneo a la primera unidad de cálculo conmutada al modo de ensayo, por medio de la segunda unidad de cálculo para la preparación de datos de resultados de ensayo para la primera unidad de cálculo;

- verificación de la verosimilitud de los datos de resultados de ensayo acondicionados por medio de la

segunda unidad de cálculo para la preparación de un resultado de ensayo para la primera unidad de 2

cálculo.

De acuerdo con la invención, el procedimiento de acuerdo con la invención presenta, además, las siguientes etapas:

- carga de segundos datos de ensayo para la verificación de la segunda unidad de cálculo, en el que los segundos datos de ensayo son cargados por medio de la interfaz de aparatos de control o los primeros datos de ensayo registrados en la segunda unidad de memoria son cargados como segundos datos de ensayo a través de una interfaz interna del aparato de control;

- registro en memoria de los segundos datos de ensayo cargados en una primera unidad de memoria de la primera unidad de cálculo;

- conmutación de la segunda unidad de cálculo a un modo de ensayo, en el que una segunda cadena de escaneo de la segunda unidad de cálculo es accesible, por medio de la primera unidad de cálculo;

- lectura de los segundos datos de ensayo desde la primera unidad de memoria por medio de la primera unidad de cálculo;

- desplazamiento de los segundos datos de ensayo leídos a través de la segunda cadena de escaneo de la segunda unidad de cálculo conmutada al modo de ensayo por medio de la primera unidad de cálculo para la preparación de datos de resultados de ensayo para la segunda unidad de cálculo; y

- verificación de factibilidad de los datos de resultados de ensayo acondicionados por medio de la primera unidad de cálculo para la preparación de un resultado de ensayo para la segunda unidad de cálculo.

En las reivindicaciones dependientes se encuentran desarrollos y configuraciones ventajosos del procedimiento indicado en la reivindicación 1 para la verificación de al menos una unidad de cálculo incorporada en un aparato de control.

De acuerdo con un desarrollo preferido de la invención, los datos de ensayo leídos desde la segunda unidad de memoria son desplazados por medio de la segunda unidad de cálculo a través de una primera interfaz dedicada, por medio de la cual se acopla la segunda unidad de cálculo con la primera cadena de escaneo, a través de la primera cadena de escaneo.

De acuerdo con otro desarrollo preferido, los segundos datos de ensayo leídos desde la primera unidad de memoria son desplazados por medio de la primera unidad de cálculo a través de una segunda interfaz dedicada, por medio de la cual se acopla la primera unidad de cálculo con la segunda cadena de escaneo, a través de la segunda cadena de escaneo.

De acuerdo con otro desarrollo preferido, el aparato de control está provisto con un generador de pulsos de reloj para el acondicionamiento de un pulso de reloj predeterminable y el desplazamiento de los datos de ensayo leídos en cada caso se realiza a través de la cadena de escaneo respectiva para la realización de un ensayo-Path-Delay utilizando el pulso de reloj acondicionado.

De acuerdo con una configuración preferida de la invención, la primera interfaz dedicada y/o la segunda interfaz dedicada están configuradas, respectivamente, como un registro de corredera o una interfaz-ASC o una interfaz-SPI.

De acuerdo con otra configuración preferida, la interfaz de aparatos de control está configurada como bus-CAN o como Bus-FlexRay o bus-K-Line o Bus-LIN.

De acuerdo con otra configuración preferida, los datos de resultados de ensayo acondicionados en cada caso y/o los resultados de ensayos acondicionados en cada caso son registrados en al menos una unidad de memoria de la primera unidad de cálculo o de la segunda unidad de cálculo y/o son acondicionados por medio de la interfaz de aparatos de control para la exportación.

De acuerdo con otra configuración preferida, el pulso de reloj del generador de pulsos de reloj se ajusta a través de la interfaz de aparatos de control.

De acuerdo con otro desarrollo preferido, la primera unidad... [Seguir leyendo]

Reivindicaciones:

1. Procedimiento para la verificación de unidades de cálculo (2, 3) incorporadas en un aparato de control, presentando el aparato de control una interfaz de aparato de control, al menos dos unidades de cálculo (2, 3) , que presentan, respectivamente, una cadena de escaneo (4, 5) y al menos dos unidades de memoria (6, 7) , con las etapas:

a) carga de primeros datos de ensayo por medio de la interfaz de aparatos de control para la verificación de una primera unidad de cálculo (2) ;

b) registro en memoria de los primeros datos de ensayo cargados en una segunda unidad de memoria (7) de una segunda unidad de cálculo (3) ;

c) conmutación de la primera unidad de cálculo (2) a un modo de ensayo, en el que una primera cadena de escaneo (4) de la primera unidad de cálculo (2) es accesible, por medio de la segunda unidad de cálculo (3) ;

d) lectura de los primeros datos de ensayo desde la segunda unidad de cálculo (7) por medio de la segunda unidad de cálculo (3) ;

e) desplazamiento de los primeros datos de ensayo leídos a través de la primera cadena de escaneo (4) a la primera unidad de cálculo (2) conmutada al modo de ensayo, por medio de la segunda unidad de cálculo (3) para la preparación de datos de resultados de ensayo para la primera unidad de cálculo (2) ;

f) verificación de la verosimilitud de los datos de resultados de ensayo acondicionados por medio de la segunda unidad de cálculo (3) para la preparación de un resultado de ensayo para la primera unidad de 20 cálculo (2) ;

g) carga de segundos datos de ensayo para la verificación de la segunda unidad de cálculo (3) , en el que los segundos datos de ensayo son cargados por medio de la interfaz de aparatos de control o los primeros datos de ensayo registrados en la segunda unidad de memoria (7) son cargados como segundos datos de ensayo a través de una interfaz interna del aparato de control (1) ;

h) registro en memoria de los segundos datos de ensayo cargados en una primera unidad de memoria (6) de la primera unidad de cálculo (2) ;

i) conmutación de la segunda unidad de cálculo (3) a un modo de ensayo, en el que una segunda cadena de escaneo (5) de la segunda unidad de cálculo (3) es accesible, por medio de la primera unidad de cálculo (2) ;

j) lectura de los segundos datos de ensayo desde la primera unidad de memoria (6) por medio de la primera unidad de cálculo (2) ;

k) desplazamiento de los segundos datos de ensayo leídos a través de la segunda cadena de escaneo (5) de la segunda unidad de cálculo (3) conmutada al modo de ensayo por medio de la primera unidad de cálculo (2) para la preparación de datos de resultados de ensayo para la segunda unidad de cálculo (5) ; y

l) verificación de factibilidad de los datos de resultados de ensayo acondicionados por medio de la primera unidad de cálculo (2) para la preparación de un resultado de ensayo para la segunda unidad de cálculo (3) .

2. Procedimiento de acuerdo con la reivindicación 1, caracterizado porque los primeros datos de ensayo leídos desde la segunda unidad de memoria (7) son desplazados por medio de la segunda unidad de cálculo (3) a través de una primera interfaz dedicada (8) , por medio de la cual se acopla la segunda unidad de cálculo (3) con la primera cadena de escaneo (4) , a través de la primera cadena de escaneo (4) .

3. Procedimiento de acuerdo con la reivindicación 2, caracterizado porque la primera interfaz dedicada (8) está configurada como un registro de corredera o una interfaz-ASC o una interfaz-SPI.

4. Procedimiento de acuerdo con la reivindicación 2, caracterizado porque los segundos datos de ensayo leídos desde la primera unidad de memoria (6) son desplazados por medio de la primera unidad de cálculo (2) a través de 45 una segunda interfaz dedicada (9) , por medio de la cual se acopla la primera unidad de cálculo (2) con la segunda cadena de escaneo (5) , a través de la segunda cadena de escaneo (5) .

5. Procedimiento de acuerdo con la reivindicación 4, caracterizado porque la primera interfaz dedicada (8) y/o la segunda interfaz dedicada (9) están configuradas, respectivamente, como un registro de corredera o una interfaz-ASC o una interfaz-SPI.

6. Procedimiento de acuerdo con una o varias de las reivindicaciones 1 a 5, caracterizado porque el aparato de control (1) es provisto con un generador de pulsos de reloj (10) para el acondicionamiento de un pulso de reloj predeterminable y el desplazamiento de los datos de ensayo leídos en cada caso se realiza a través de la cadena de escaneo (4, 5) respectiva para la realización de un ensayo-Path-Delay utilizando el pulso de reloj acondicionado.

7. Procedimiento de acuerdo con la reivindicación 6, caracterizado porque el pulso de reloj del generador de pulsos de reloj (10) se ajusta a través de la interfaz del aparato de control.

8. Procedimiento de acuerdo con una o varias de las reivindicaciones 1 a 5, caracterizado porque la interfaz de aparatos de control está configurada como bus-CAN o como Bus-FlexRay o bus-K-Line o Bus-LIN.

9. Procedimiento de acuerdo con una o varias de las reivindicaciones 1 a 5, caracterizado porque los datos de resultados de ensayo acondicionados en cada caso y/o los resultados de ensayos acondicionados en cada caso son registrados en al menos una unidad de memoria (6, 7) de la primera unidad de cálculo (2) o de la segunda unidad de cálculo (3) y/o son acondicionados por medio de la interfaz de aparatos de control para la exportación.

10. Procedimiento de acuerdo con una o varias de las reivindicaciones 1 a 5, caracterizado porque la primera unidad de cálculo (2) y la segunda unidad de cálculo (3) están integradas en un único circuito integrado, en el que aquellas trayectorias-Stuck-At del circuito integrado, que no pertenecen a la primera unidad de cálculo (2) o a la segunda unidad de cálculo (3) , son verificadas por medio de la primera unidad de cálculo (2) o de la segunda unidad de cálculo (3) .

Patentes similares o relacionadas:

ARQUITECTURA DE CIRCUITO INTEGRADO QUE TIENE UNA AGRUPACION DE CELULAS DE PRUEBA QUE PROPORCIONAN UN CONTROL ABSOLUTO PARA LA VERIFICACION DE CIRCUITOS AUTOMATICOS., del 1 de Diciembre de 2003, de LIGHTSPEED SEMICONDUCTORS CORPORATION: Circuito integrado, que consta de: una matriz o red de células lógicas prefabricada , que puede combinarse para formar un circuito arbitrario, […]

SISTEMA Y METODO DE DIAGNOSTICO REMOTO., del 1 de Noviembre de 2003, de RICOH COMPANY: SE DESCRIBE UN SISTEMA DE DIAGNOSTICO REMOTO QUE INCLUYE UN SISTEMA DE ORDENADOR CENTRAL QUE RECIBE DATOS DE USUARIO RELACIONADOS CON UNA PETICION DEL USUARIO, […]

CIRCUITO INTEGRADO DE APLICACION ESPECIFICA (ASIC) CON MICROPROCESADOR QUE INCORPORA MEDIOS DE PRUEBA, del 16 de Junio de 1998, de SOCIETE D'APPLICATIONS GENERALES D'ELECTRICITE ET DE MECANIQUE SAGEM: CIRCUITO INTEGRADO DE APLICACION ESPECIFICA (ASIC), QUE COMPRENDE UN MICROPROCESADOR , EN EL CUAL AL MENOS UNA ENTRADA FUNCIONAL ESTA UNIDA A UNA […]

PROCEDIMIENTO PARA ENSAYAR UN BUS DE DIRECCIONES EN UN MÓDULO LÓGICO, del 29 de Julio de 2011, de ROBERT BOSCH GMBH: Procedimiento para el ensayo de un bus de direcciones en un módulo lógico , en el que en el módulo lógico está previsto al […]

SISTEMA Y METODO DE SOBREDIVISION EN PARTICIONES PARA INCREMENTAR LOS PUNTOS DE CONTROL EN APLICACIONES PARALELAS BASADAS EN PROGRAMAS COMPONENTES, del 16 de Octubre de 2007, de AB INITIO SOFTWARE CORPORATION: SE DESCRIBEN DOS PROCEDIMIENTOS PARA SEGMENTAR EL TRABAJO QUE DEBE SER REALIZADO POR UN PROGRAMA DE ORDENADOR EN PARTES MAS PEQUEÑAS DE MANERA QUE […]

SISTEMA Y METODO DE SOBREDIVISION EN PARTICIONES PARA INCREMENTAR LOS PUNTOS DE CONTROL EN APLICACIONES PARALELAS BASADAS EN PROGRAMAS COMPONENTES, del 16 de Octubre de 2007, de AB INITIO SOFTWARE CORPORATION: SE DESCRIBEN DOS PROCEDIMIENTOS PARA SEGMENTAR EL TRABAJO QUE DEBE SER REALIZADO POR UN PROGRAMA DE ORDENADOR EN PARTES MAS PEQUEÑAS DE MANERA QUE […]