PROCEDIMIENTO Y DISPOSITIVO DE GENERACION DE SEÑALES BINARIAS DESFASADAS Y SU UTILIZACION.

Procedimiento de generación de señales binarias desfasadas (So1,

So2,So3) de un ángulo de desfase de control (&966;) continuamente variable con respecto a al menos una señal binaria de sincronización de un conjunto de señales binarias de sincronización (Si1,Si2,Si3) que tienen un mismo periodo (&916;Ttotal) variable, del tipo de los consistente en elaborar los flancos de subida (8) y de bajada (12) de dichas señales desfasadas (So1,So2,So3) calculando al menos un retraso de conmutación de nivel (&916;T1) a partir de flancos de sincronización, de subida (2,3,5,6) o de bajada (1,4,7), de dicha señal binaria de sincronización (Si1,Si2,Si3) al menos, en función al menos de dicho ángulo de desfase de control (&966;), caracterizado por el hecho de que al menos un flanco de referencia (4,5,7) se escoge de entre dichos flancos de sincronización (17) de manera que dicho retraso (&916;T1) sea mínimo

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/FR2007/051180.

Solicitante: VALEO EQUIPEMENTS ELECTRIQUES MOTEUR.

Nacionalidad solicitante: Francia.

Dirección: 2, RUE ANDRE BOULLE, 94046 CRETEIL CEDEX.

Inventor/es: ROUIS,OUSSAMA.

Fecha de Publicación: .

Fecha Concesión Europea: 18 de Agosto de 2010.

Clasificación Internacional de Patentes:

- H03K5/13D

Clasificación PCT:

- H03K5/13 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 5/00 Manipulación de impulsos no cubiertos por ninguno de los otros grupos principales de la presente subclase (circuitos de realimentación H03K 3/00, H03K 4/00; utilizando dispositivos magnéticos o eléctricos no lineales H03K 3/45). › Disposiciones que tienen una salida única y transforman la señal de entrada en impulsos transmitidos en intervalos de tiempo deseados.

Fragmento de la descripción:

La presente invención se refiere a un procedimiento y a un dispositivo de generación de señales binarias que tienen un desfase regulable basadas en un componente programable.

ANTECEDENTES TECNOLÓGICOS DE LA INVENCIÓN.

Los circuitos desfasadores se utilizan en numerosas aplicaciones de la electrónica, tanto en tratamiento de la señal como en electrónica de potencia. En general, un circuito está concebido para realizar un desfase determinado a una frecuencia determinada. El circuito debe ser modificado para otro ángulo de fase, u otra frecuencia. [0003] Los circuitos y los procesos descritos en el documento US6744296 han cambiado esta situación, puesto que el ángulo de desfase puede ser continuamente ajustado por una tensión independientemente de la frecuencia. [0004] Sin embargo los componentes analógicos utilizados en parte en los circuitos precedentes no garantizan la generación de desfases muy precisos requeridos por determinadas aplicaciones. [0005] Es el caso en especial en aplicaciones al automóvil, como los encendidos electrónicos descritos por ejemplo en el documento DE 41 28 909 A1, o el pilotaje de los motores/ generadores eléctricos sin escobillas. [0006] Así, el documento US4788957, por ejemplo, propone mejorar los dispositivos de control del punto de encendido de los motores de combustión interna empleando un circuito de desfase y un detector de autoencendido constituidos por un ordenador. [0007] Un obstáculo a la generalización de los métodos totalmente numéricos en el sector, aunque sean muy ventajosos desde el punto de vista de la versatilidad de implementación y de los costes, con respecto a los procesos analógicos, ha sido la gran potencia de cálculo necesaria para seguir las variaciones rápidas de las señales. [0008] La aparición en el mercado de los componentes de microcontroladores multiprocesadores permite evitar esta restricción, con la condición de que sean programados de manera apropiada.

El documento US5317248 divulga precisamente una manera de programar un microcontrolador MC68332 de la empresa MOTOROLA para generar los impulsos de control, modulados en anchura, de máquinas eléctricas polifásicas. [0010] El microcontrolador MC68332 tiene, aparte de una unidad central de tratamiento, o CPU (CPU es el acrónimo inglés de Central Processing Unit), una unidad de cálculo dedicada a los acontecimientos temporales, o TPU (TPU es el acrónimo inglés de Time Processor Unit). La TPU tiene unos circuitos retardadores programables (conocidos por el experto en la materia por el vocablo inglés « timer ») y unos módulos de modulación de anchura de impulsos programables, llamados módulos PWM (PWM es el acrónimo inglés de Pulse Width Modulation). [0011] La TPU genera una señal de sincronización y unos impulsos centrados en los flancos de esta señal. [0012] Los algoritmos descritos en el documento US5317248 se proponen limitar los retardos de tránsito y la fluctuación de la señal, pero el método utilizado solamente parece aplicable en el caso en que las señales generadas solamente están desfasadas con respecto a una única señal de sincronización, proveniente de un único sensor de posición del rotor de la máquina. [0013] Sin embargo, se sabe que es preferible que una máquina eléctrica polifásica comprenda un sensor de posición para cada fase con el fin de detectar rápidamente las variaciones de velocidad del rotor.

DESCRIPCIÓN GENERAL DE LA INVENCIÓN.

La presente invención se propone por lo tanto dar remedio a esta carencia suministrando un procedimiento de generación de señales binarias desfasadas con respecto a al menos una señal binaria de sincronización de un conjunto de señales binarias de sincronización. El ángulo de desfase de control es continuamente variable, y las señales de sincronización tienen un mismo periodo variable. [0015] Este procedimiento es del tipo de los consistentes en elaborar los flancos de subida y de bajada de las señales desfasadas calculando al menos un retraso de conmutación de nivel a partir de flancos de sincronización, de subida o de bajada, de la señal binaria de sincronización al menos, en función al menos del ángulo de desfase de control.

El procedimiento según la invención es destacable por el hecho de que al menos un flanco de referencia se escoge de entre los flancos de sincronización de manera tal que este retraso de conmutación de nivel sea mínimo. [0017] Preferentemente, el número de las señales desfasadas y el número de las señales de sincronización son iguales a un número de fases predeterminado. Las señales de sincronización tienen ventajosamente una relación cíclica igual a 0,5 y están desfasadas entre sí de un ángulo de desfase nominal en grados igual a 360° dividido por este número de fases. Una característica adicional del procedimiento según la invención consiste entonces en medir un intervalo de tiempo comprendido entre dos flancos de sincronización sucesivos, siendo uno de subida y el otro de bajada. [0018] El retraso de conmutación de nivel se calcula para una señal binaria de sincronización corriente entre las señales binarias de sincronización, con vistas a elaborar el flanco correspondiente de la señal binaria desfasada corriente asociada, preferentemente por la expresión siguiente:

**(Ver fórmula)**

- ΔTpn es el intervalo de tiempo medido anteriormente; -φ es el ángulo de fase de control expresado en grados; -Δφref es el desfase φ0 -φr, expresado en grados, entre un flanco inicial de ángulo de fase inicial φ0 de la señal binaria de sincronización corriente y el flanco de referencia de ángulo de fase de referencia φr de una señal binaria de sincronización de referencia escogido entre las señales de sincronización; -Np es igual al doble del número de fases.

Se aprovecha el hecho de que un valor interflanco del intervalo de tiempo comprendido entre dos flancos de sincronización sucesivos, resulta de un conteo mediante un circuito retardador programable de medida, que tiene una frecuencia de incremento de medida predeterminada, que está asociado a las señales binarias de sincronización. [0020] En este caso, un valor corriente del retraso de conmutación de nivel se calcula para una señal binaria de sincronización corriente entre las señales binarias de

sincronización, con vistas a elaborar el flanco correspondiente de la señal binaria desfasada corriente asociada, preferentemente por la expresión siguiente:

**(Ver fórmula)**

donde: -VΔTpn es el valor interflanco; -φ es el ángulo de fase de control expresado en grados; -Δφref es el desfase φ0 -φr, expresado en grados, entre un flanco inicial de ángulo de fase inicial φ0 de la señal binaria de sincronización corriente y el flanco de referencia de ángulo de fase de referencia φr de una señal binaria de sincronización de referencia escogido entre las señales binarias de sincronización; -Np es igual al doble del número de fases.

Llegados a este punto, el procedimiento de generación de señales binarias desfasadas según la invención comprende muy ventajosamente las etapas siguientes:

- se suministra la frecuencia de incremento corriente de un circuito retardador programable corriente asociado a la señal binaria de sincronización corriente igual a la frecuencia de incremento de medida; -se asocia una línea de salida corriente al circuito retardador programable corriente; -se carga el valor corriente VΔT1 del retraso de conmutación en el circuito retardador programable corriente; -se configura este circuito retardador programable corriente de manera que la línea de salida corriente efectúe

una primera transición de un nivel alto hacia un nivel bajo, o bien una segunda transición de un nivel bajo hacia un nivel alto, cuando un contador corriente del retardador programable corriente alcanza el valor corriente VΔT1; -se genera la señal binaria desfasada corriente mediante la línea de salida corriente.

Como alternativa a las etapas anteriores, el procedimiento de generación de señales binarias desfasadas según la invención comprende también ventajosamente como variante las etapas siguientes:

- se suministra la frecuencia de incremento corriente de un circuito retardador programable corriente asociado a la señal binaria de sincronización corriente igual a la frecuencia de incremento de medida; -se carga el valor corriente VΔT1 del retraso de conmutación en el circuito retardador programable corriente; -se activa una interrupción corriente asociada al circuito retardador...

Reivindicaciones:

1. Procedimiento de generación de señales binarias desfasadas (So1,So2,So3) de un ángulo de desfase de control (φ) continuamente variable con respecto a al menos una señal binaria de sincronización de un conjunto de señales binarias de sincronización (Si1,Si2,Si3) que tienen un mismo periodo (ΔTtotal) variable, del tipo de los consistente en elaborar los flancos de subida (8) y de bajada (12) de dichas señales desfasadas (So1,So2,So3) calculando al menos un retraso de conmutación de nivel (ΔT1) a partir de flancos de sincronización, de subida (2,3,5,6) o de bajada (1,4,7), de dicha señal binaria de sincronización (Si1,Si2,Si3) al menos, en función al menos de dicho ángulo de desfase de control (φ), caracterizado por el hecho de que al menos un flanco de referencia (4,5,7) se escoge de entre dichos flancos de sincronización (17) de manera que dicho retraso (ΔT1) sea mínimo.

2. Procedimiento de generación de señales binarias desfasadas (So1,So2,So3) según la reivindicación 1, caracterizado por el hecho de que siendo el número de dichas señales desfasadas (So1,So2,So3) y el número de dichas señales de sincronización (Si1,Si2,Si3) iguales a un número de fases predeterminado, y teniendo dichas señales de sincronización (Si1,Si2,Si3) una relación cíclica igual a 0,5 y estando desfasadas entre sí de un ángulo de desfase nominal (Ф) en grados igual a 360° dividido por dicho número de fases, se mide un intervalo de tiempo (ΔTpn) comprendido entre dos de dichos flancos de sincronización (1-7) sucesivos, siendo uno de subida y el otro de bajada.

3. Procedimiento de generación de señales binarias desfasadas (So1,So2,So3) según la reivindicación 2, caracterizado por el hecho de que dicho retraso (Δ1T) se calcula para una señal binaria de sincronización corriente (Si1) entre dichas señales binarias de sincronización (Si1,Si2,Si3) con vistas a elaborar el flanco (8,12) correspondiente de la señal binaria desfasada corriente (So1) asociado por la expresión siguiente:

**(Ver fórmula)**

donde:

- ΔTpn es dicho intervalo de tiempo; -φ es dicho ángulo de fase de control comprendido entre -180° y +180;

- Δφref es el desfase φ0 -φr, expresado en grados, entre un flanco inicial (5) de ángulo de fase inicial φ0 de dicha señal binaria de sincronización corriente (Si1) y dicho flanco de referencia (4,5,7) de ángulo de fase de referencia φr de una señal binaria de sincronización de referencia escogido entre dichas señales de sincronización (Si1,Si2,Si3); -Np es igual al doble de dicho número de fases.

4. Procedimiento de generación de señales binarias desfasadas (So1,So2,So3) según la reivindicación 2, caracterizado por el hecho de que un valor interflanco (VΔTpn) de dicho intervalo de tiempo (ΔTpn) resulta de un conteo mediante un circuito retardador programable de medida (TIMERM, 34) asociado a dichas señales binarias de sincronización (Sil, Si2,Si3) que tienen una frecuencia de incremento de medida (FTIMERM) predeterminada.

5. Procedimiento de generación de señales binarias desfasadas (So1,So2,So3) según la reivindicación 4, caracterizado por el hecho de que un valor corriente (VΔT1) de dicho retraso (ΔT1) se calcula para una señal binaria de sincronización corriente (Si1) entre dichas señales binarias de sincronización (Si1,Si2,Si3) con vistas a elaborar el flanco correspondiente (8,12) de la señal binaria desfasada corriente (So1) asociada por la expresión siguiente:

donde: -VΔTpn es dicho valor interflanco; -φ es dicho ángulo de fase de control comprendido entre -180° y +180; -Δφref es el desfase φ0 -φr, expresado en grados, entre un flanco inicial (5) de ángulo de fase inicial φ0 de dicha señal binaria de sincronización corriente (Si1) y dicho flanco de referencia (4,5,7) de ángulo de fase de referencia φr de una señal binaria de sincronización de referencia escogido entre dichas señales binarias de sincronización (Si1,Si2,Si3); -Np es igual al doble de dicho número de fases.

6. Procedimiento de generación de señales binarias desfasadas (So1,So2,So3) según la reivindicación 5, caracterizado por el hecho de que comprende las etapas siguientes:

- se suministra la frecuencia de incremento corriente (FTIMER1) de un circuito retardador programable corriente (TIMER1,35,36,37) asociado a dicha señal binaria de sincronización corriente (Si1) igual a dicha frecuencia de incremento de medida (FTIMERM); -se asocia una línea de salida corriente (OUTPIN1) a dicho circuito retardador programable corriente (TIMER1,35,36,37); -se carga el valor corriente (VΔT1) de dicho retraso (ΔT1) en dicho circuito retardador programable corriente (TIMER1,35,36,37); -se configura dicho circuito retardador programable corriente (TIMER1,35,36,37) de manera que dicha línea de salida corriente (OUTPIN1) efectúa una primera transición de un nivel alto hacia un nivel bajo, o bien una segunda transición de un nivel bajo hacia un nivel alto, cuando un contador corriente de dicho retardador programable corriente (TIMER1,35,36,37) alcanza dicho valor corriente (VΔT1); -se genera dicha señal binaria desfasada corriente (So1) mediante dicha línea de salida corriente (OUTPIN1).

7. Procedimiento de generación de señales binarias desfasadas (So1,So2,So3) según la reivindicación 5, caracterizado por el hecho de que comprende las etapas siguientes:

**(Ver fórmula)**

- se suministra la frecuencia de incremento corriente (FTIMER1) de un circuito retardador programable corriente (TIMER1,35,36,37) asociado a dicha señal binaria de sincronización corriente (Si1) igual a dicha frecuencia de incremento de medida (FTIMERM); -se carga el valor corriente (VΔT1) de dicho retraso (ΔT1) en dicho circuito retardador programable corriente (TIMER1,35,36,37); -se activa una interrupción corriente (INTT1) asociada a dicho circuito retardador programable corriente (TIMER1,35,36,37) que se produce cada vez que se alcanza dicho valor corriente (VΔT1); -se suministra la frecuencia de conteo corriente (FPMW) de un contador programable corriente (TIMERPWM1) de un módulo de modulación de anchura de impulsos programable corriente (PWM1,39,40,41) igual a dicha frecuencia de incremento de medida (FTIMERM) dividida por el doble de dicho número de fases; -se asocia una línea de salida corriente (Spwm1) a dicho módulo de modulación de anchura de impulsos programable corriente (PWM1,39,40,41); -se carga un registro de periodo corriente (REGPERpwm1) y un registro de relación cíclica corriente (REGDUTYpwm1) de dicho módulo de modulación de anchura de impulsos programable corriente (PWM1,39,40,41) respectivamente con dicho valor interflanco (VΔTpn) y con la mitad de dicho valor interflanco (VΔTpn); -se configura dicho módulo de modulación de anchura de impulsos corriente (PWM1,39,40,41) de manera que dicha línea de salida corriente (Spwm1) padezca una transición inicial de un nivel alto a un nivel bajo, y una primera transición de un nivel bajo a un nivel alto cuando dicho contador programable corriente (TIMERPWM1) alcanza un valor intermedio corriente (VDUTYpmw1) contenido en el registro de relación cíclica corriente (REGDUTYpwm1), y finalmente una segunda transición de un nivel alto a un nivel bajo cuando dicho contador programable corriente (TIMERPWM1) alcanza un valor final corriente (VPERpwm1) contenido en dicho registro de periodo corriente (REGPERpwm1) en cada disparo de dicha interrupción corriente (INTT1); -se genera dicha señal binaria desfasada corriente (So1) mediante dicha línea de salida corriente (Spwm1).

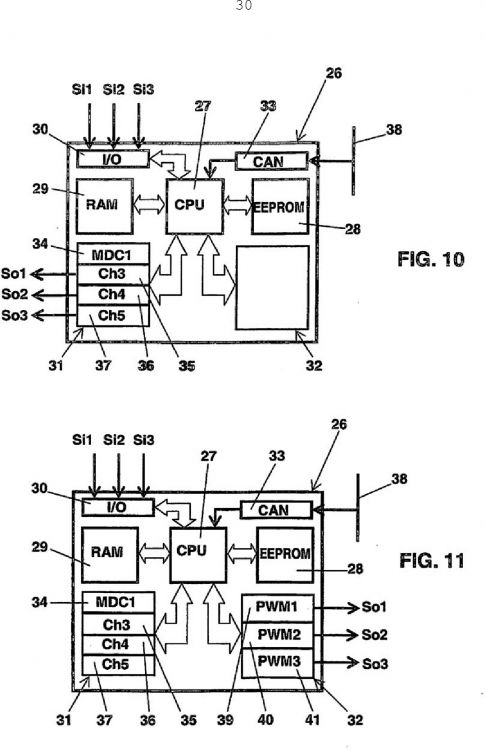

8. Dispositivo de generación de señales binarias desfasadas (So1,So2,So3) de un ángulo de desfase de control (φ) continuamente variable con respecto a al menos una señal binaria de sincronización de un conjunto de señales binarias de sincronización (Si1,Si2,Si3), del tipo de los que comprenden un microprocesador o un microcontrolador (26) que comprende:

- al menos una unidad central de tratamiento (27); -al menos una memoria volátil (29) y/o al menos una memoria no volátil (28); -al menos un circuito retardador programable (34,35,36,37); -al menos un puerto de entrada (30); caracterizado por el hecho de que dichas memorias (28,28) contienen un programa que lleva a cabo el procedimiento según cualquiera de las reivindicaciones 1 a 7 anteriores.

9. Dispositivo de generación de señales binarias desfasadas (So1,So2,So3) según la reivindicación 8, caracterizado por el hecho de que comprende además al menos un módulo de modulación de anchura de impulsos programable (39,40,41).

10. Dispositivo de generación de señales binarias desfasadas (So1,So2,So3) según cualquiera de las reivindicaciones 8 ó 9, caracterizado por el hecho de que comprende además una interfaz serie (33) que recibe una señal representativa de dicho ángulo de fase de control (φ), garantizando dicha interfaz (33) preferentemente un

5 enlace con una red de a bordo (38) de tipo CAN.

11. Utilización del procedimiento según cualquiera de las reivindicaciones 1 a 7 anteriores y/o del dispositivo según cualquiera de las reivindicaciones 8 a 10 en el lazo de control de una máquina eléctrica polifásica llevada a bordo de un vehículo, en

10 especial automóvil.

12. Secuencias de instrucciones ejecutables por el dispositivo según cualquiera de las reivindicaciones 8 a 10 que lleva a cabo el procedimiento según cualquiera de las reivindicaciones 1 a 7.

Patentes similares o relacionadas:

Circuito integrado foto-repetido con compensación de retardos de propagación de señal, especialmente de señales de reloj, del 22 de Julio de 2020, de Pyxalis: Circuito integrado que comprende N patrones adyacentes, todos idénticos, que corresponden a N circuitos parciales adyacentes idénticos (C1, C2, C3) de rango i = 1 a […]

Calibración de circuito de recuperación de datos de reloj multifásico, del 18 de Marzo de 2020, de QUALCOMM INCORPORATED: Un procedimiento de comunicaciones de datos, que comprende: configurar un primer circuito de recuperación de reloj para proporcionar una señal de reloj […]

Interpolador de borde digitalmente controlado (DCEI) para convertidores digital-tiempo (DTC), del 22 de Noviembre de 2018, de INTEL CORPORATION: Un convertidor digital-tiempo, DTC, , que comprende: un segmento de retardo/fase gruesa que genera una señal de retardo/fase gruesa, la señal […]

Circuito de retardo programable con resolución de tiempo de enteros y fraccional, del 4 de Octubre de 2017, de QUALCOMM INCORPORATED: Un aparato , que comprende: medios para retardar una señal de entrada por un primer retardo de un número entero de unidades […]

Establecimiento de llamada de telecomunicación de medios mixtos, del 18 de Marzo de 2016, de 3G Licensing S.A: Estación móvil apta para videotelefonía en respuesta a una interrupción de una llamada en curso de telecomunicaciones de medios mixtos, comprendiendo […]

Establecimiento de llamada de telecomunicación de medios mixtos, del 18 de Marzo de 2016, de 3G Licensing S.A: Estación móvil apta para videotelefonía en respuesta a una interrupción de una llamada en curso de telecomunicaciones de medios mixtos, comprendiendo […]

Dispositivo de generación de señales de sincronización con fluctuación de fase muy reducida, del 18 de Mayo de 2012, de COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES: Dispositivo de generación de señales de sincronización con fluctuación de fase muy reducida, particularmente para la sincronización de la activación de pulsos láser en un […]

Dispositivo de generación de señales de sincronización con fluctuación de fase muy reducida, del 18 de Mayo de 2012, de COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES: Dispositivo de generación de señales de sincronización con fluctuación de fase muy reducida, particularmente para la sincronización de la activación de pulsos láser en un […]

DISPOSITIVO DE FOTO-ESTIMULACION PARA DIAGNOSTICO Y TRATAMIENTO EN TERAPIAS ENERGETICAS, del 8 de Enero de 2010, de MERINO MACDONNELL,EDUARDO DANIEL: La presente invención se refiere, como el título lo indica, a un dispositivo emisor de luz, continua o pulsada, de longitudes de onda comprendidas […]

DISPOSITIVO DE FOTO-ESTIMULACION PARA DIAGNOSTICO Y TRATAMIENTO EN TERAPIAS ENERGETICAS, del 8 de Enero de 2010, de MERINO MACDONNELL,EDUARDO DANIEL: La presente invención se refiere, como el título lo indica, a un dispositivo emisor de luz, continua o pulsada, de longitudes de onda comprendidas […]

CIRCUITO DE SELECCION DE FASE., del 1 de Junio de 2005, de VITESSE SEMICONDUCTOR CORPORATION: Un circuito de selección de fase para seleccionar una fase a partir de una fuente de fases que genera las señales de fase, teniendo las señales de fase distintas fases, que […]