Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal.

Procedimiento (200) para la corrección de un error de offset de un convertidor de señal (140),

en donde elprocedimiento (200) presenta los siguientes pasos:

a) unión (210) de una entrada del convertidor de señal (140) a un canal de offset (OK), que está configuradopara proporcionar un valor de 5 tensión de referencia predefinido o un valor de corriente predefinido;

b) detección (220) y archivado de un valor de offset proporcionado a una salida del convertidor de señal (140),que el convertidor de señal (140) envía en respuesta a la aplicación del valor de tensión de referenciapredefinido o valor de corriente de referencia predefinido, en donde se realiza el archivado del valor deoffset en una memoria de valores de error de offset (160);

c) contactado (230) de la entrada del convertidor de señal (140) con una magnitud eléctrica a medir, que seaplica al menos a un canal de medición (MK1 - MK4);

d) detección (240) de un valor de medición proporcionado a la salida del convertidor de señal (140), que elconvertidor de señal (140) envía en respuesta a la aplicación de la magnitud eléctrica, y archivado del valorde medición en una memoria de valores de medición (170); y

caracterizado por un paso de

e) enlace (250) del valor de medición procedente de la memoria de valores de medición (170) con el valor deoffset procedente de la memoria de valores de error de offset (160) sobre la base de una estructura deenlace (180) en hardware, para obtener un valor de medición corregido y proporcionar este valor demedición corregido para una transmisión (190) a otra unidad de tratamiento de datos, en dondese entrega una señal de una unidad de control (130) a un interruptor (150), en donde el interruptor (150) estáconfigurado para unir la salida del convertidor de señal (140), en respuesta a la señal de la unidad de control (130),ya sea a la memoria de valores de error de offset (160) o a la memoria de valores de medición (170).

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E09166537.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20 70442 STUTTGART ALEMANIA.

Inventor/es: KARNER,RUEDIGER, OECHTERING,PETER.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M1/10 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 1/00 Conversión analógica/digital; Conversión digital/analógica (conversión de valores analógicos en, o a partir de una modulación diferencial H03M 3/00). › Calibración o ensayos.

- H03M1/12 H03M 1/00 […] › Convertidores analógico/digitales (H03M 1/02 - H03M 1/10 tienen prioridad).

PDF original: ES-2416479_T3.pdf

Fragmento de la descripción:

Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal

La presente invención se refiere a un procedimiento para la corrección de un error de offset de un convertidor de señal conforme a la reivindicación 1, así como un dispositivo de corrección para la corrección de un error de offset de un convertidor de señal conforme a la reivindicación 9.

En aplicaciones actuales se incluyen en el cálculo y con ello se demuestran errores de offset, en el caso de circuitos de convertidor analógico-digital (convertidores AD) , en el error total. En algunos sistemas, en los que se exige una mayor precisión, se lleva a cabo una medición de tensión de offset y se liquida el importe allí medido con ayuda del software con el valor de medición posterior.

Por el momento existe la posibilidad de activar una compensación de offset a través de un software. Este método tiene el inconveniente, sin embargo, de que el software tiene que activar implícitamente la medición de error de offset, archivar el resultado de medición y liquidarlo con cada valor medido. Esto exige una complejidad adicional en la comunicación así como en el cálculo de datos, lo que en sistemas con plazos críticos puede conducir a problemas con la duración del programa.

En el documento US 5, 610, 810 se propone un planteamiento para llevar a cabo a la vez una adaptación de la amplificación y de un offset de un aparato de tratamiento de datos para controlar el funcionamiento de una copiadora o similar, sin que la adaptación de los componentes aislados sea necesaria, con los que se compone el aparato (como por ejemplo un convertidor A/D) . Pueden compensarse modificaciones de la amplificación y/o del offset del aparato, que se producen con el tiempo. Aquí pueden llevarse a cabo una solicitud de datos y una edición de datos.

El documento WO 92/04775 A1 hace patente un dispositivo mejorado con auto-reposición a cero y un procedimiento para un sistema de detección de datos tomográfico apoyado por ordenador.

El documento US 6, 433713 B hace patente una calibración de un convertidor analógico-digital.

El documento Komblum J, “TB329. Technical Brief: Intersil Sigma-Delta Calibration Technique.”, mayo de 1995, muestra un modo de proceder para la calibración de un convertidor sigma-delta de Intersil.

La presente invención crea un procedimiento para la corrección de un error de offset de un convertidor de señal, en donde el procedimiento presenta los pasos definidos en la reivindicación 1.

Aparte de esto, la presente invención crea un dispositivo de corrección de un error de offset de un convertidor de señal, en donde el dispositivo de corrección comprende las particularidades definidas en la reivindicación 9:

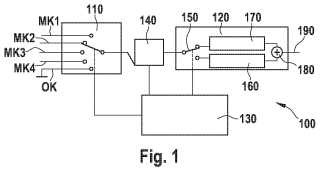

La presente invención se basa en el reconocimiento de que una corrección rápida de errores de offset de un convertidor de señal puede realizarse por medio de que, en una unidad de cálculo, un valor de medición entregado por el convertidor de señal para una magnitud eléctrica (que puede ser por ejemplo una tensión o una corriente) puede enlazarse con un valor de offset archivado en esta unidad de cálculo, en donde se utiliza una estructura de enlace en hardware. En especial en el caso de la utilización de convertidores analógico-digital como convertidores de señal es especialmente favorable una compensación de error de offset de este tipo. El valor de offset puede establecerse con ello previamente en un proceso de entrenamiento, por medio de que en primer lugar un canal de offset especial, que proporciona una corriente de referencia o una tensión de referencia, se conecta a la entrada del convertidor de señal y a continuación detecta un valor entregado por el convertidor de señal, desde la salida del convertidor de señal, y se archiva como valor de offset en una memoria de la unidad de cálculo.

La ventaja del planteamiento conforme a la invención consiste en que la corrección de error de offset se realiza antes de la edición del valor de medición corregido, por ejemplo sobre un bus de datos en una única estructura de hardware. Esta estructura de hardware puede ser por ejemplo un microcontrolador, un microprocesador, un procesador de señal digital, un circuito de conmutación integrado específico de la aplicación o un elemento similar del tratamiento de datos electrónico. De este modo puede evitarse la corrección de error de offset sobre la base de una consulta inducida por software del error de offset al convertidor de señal, la cual es excesivamente lenta en aplicaciones con plazos críticos a causa de la elaboración numéricamente compleja de órdenes de programa. Al mismo tiempo puede evitarse que, a la hora de producir un circuito correspondiente, se programe fijamente un error de offset prefijado de un convertidor de señal en la unidad de cálculo. Una programación fija de este tipo de un error de offset prefijado tendría el inconveniente de que por ejemplo modificaciones del error de offset, en función del envejecimiento o de la temperatura, no puedan tenerse en cuenta adecuadamente en un ciclo de vida del circuito de corrección correspondiente o del convertidor de señal. Con la presente invención es posible ventajosamente, por el contrario, detectar de nuevo el error de offset del convertidor de señal a intervalos regulares o irregulares y utilizar el valor de error de offset detectado de nuevo en lugar del valor de error de offset utilizado previamente.

Es ventajoso que en una forma de ejecución de la invención los pasos a) a e) se ejecuten repetidamente. Esto ofrece la ventaja de que sea posible una adaptación del valor de error de offset utilizado para la corrección de los valores de medición al error de offset actual del convertidor de señal, de tal modo que no sea necesario recurrir a un valor de error de offset programado a la hora de producir el convertidor de señal o el correspondiente dispositivo de corrección. Este valor de error de offset ajustado en fábrica ya no podría reproducir con la precisión suficiente el valor de error de offset actual a causa de procesos dependientes del envejecimiento o de la temperatura, de tal modo que ya no podría conseguirse un resultado de medición con precisión elevada al usar el convertidor de señal.

En otra forma de ejecución de la invención pueden ejecutarse los pasos a) a e) en función de un envejecimiento o de una temperatura del convertidor de señal o de un circuito para ejecutar el procedimiento. Aquí puede suponerse por ejemplo, mediante ladetección de un determinado envejecimiento o de la superación de una temperatura de un circuito o del convertidor de señal, que posiblemente ha tenido lugar un desplazamiento de offset, el cual hace necesaria una nueva medición del error de offset. De este modo para la corrección del error de offset del convertidor de señal se garantiza siempre la utilización de un valor de error de offset lo más actual posible.

Asimismo en el paso b) puede escribirse también el valor de offset en una memoria, en donde un valor archivado en esta memoria antes de la ejecución del paso b) se sobreescribe mediante la ejecución del paso b) . Esto ofrece la ventaja de que en cualquier caso puede utilizarse un valor de error de offset para la corrección, incluso si no se corresponde siempre con el error de offset actual del convertidor de señal. Con ello se parte de la excepción de que el valor de corrección de error de offset archivado en la memoria hace siempre posible una corrección de error de offset, que envía un resultado de medición mejor que cuando no se ha llevado a cabo ninguna corrección de error de offset.

Además de esto, en otra forma de ejecución de la presente invención, en el paso b) puede sobreescribirse un valor inicial archivado en la memoria al ejecutar por primera vez el procedimiento en una unidad de circuito. Por medio de esto se garantiza que al inicio del funcionamiento del convertidor de señal, incluso sin la detección del error de offset, se presente un valor de corrección de error de offset que pueda utilizarse para la corrección de error de offset. A causa del hecho de que después de la producción de los componentes del circuito estos con frecuencia tienen características de offset constantes a lo largo de un mayor periodo de tiempo, por motivos de simplificación y para garantizar una precisión elevada de los valores de medición obtenidos, por parte de fábrica se archiva ya en la memoria un primer valor de corrección de error de offset, sin que la adaptación a llevar a cabo posteriormente del mismo se haga imposible o se impida para la corrección de error de offset del valor de corrección de error de offset. Aparte de esto mediante la sobreescritura... [Seguir leyendo]

Reivindicaciones:

1. Procedimiento (200) para la corrección de un error de offset de un convertidor de señal (140) , en donde el procedimiento (200) presenta los siguientes pasos:

a) unión (210) de una entrada del convertidor de señal (140) a un canal de offset (OK) , que está configurado para proporcionar un valor de tensión de referencia predefinido o un valor de corriente predefinido;

b) detección (220) y archivado de un valor de offset proporcionado a una salida del convertidor de señal (140) , que el convertidor de señal (140) envía en respuesta a la aplicación del valor de tensión de referencia predefinido o valor de corriente de referencia predefinido, en donde se realiza el archivado del valor de offset en una memoria de valores de error de offset (160) ;

c) contactado (230) de la entrada del convertidor de señal (140) con una magnitud eléctrica a medir, que se aplica al menos a un canal de medición (MK1 – MK4) ;

d) detección (240) de un valor de medición proporcionado a la salida del convertidor de señal (140) , que el convertidor de señal (140) envía en respuesta a la aplicación de la magnitud eléctrica, y archivado del valor de medición en una memoria de valores de medición (170) ; y

caracterizado por un paso de e) enlace (250) del valor de medición procedente de la memoria de valores de medición (170) con el valor de offset procedente de la memoria de valores de error de offset (160) sobre la base de una estructura de enlace (180) en hardware, para obtener un valor de medición corregido y proporcionar este valor de medición corregido para una transmisión (190) a otra unidad de tratamiento de datos, en donde se entrega una señal de una unidad de control (130) a un interruptor (150) , en donde el interruptor (150) está configurado para unir la salida del convertidor de señal (140) , en respuesta a la señal de la unidad de control (130) , ya sea a la memoria de valores de error de offset (160) o a la memoria de valores de medición (170) .

2. Procedimiento (200) conforme a la reivindicación 1, caracterizado porque los pasos a) (210) a e) (250) se ejecutan repetidamente.

3. Procedimiento (200) conforme a la reivindicación 1 ó 2, caracterizado porque los pasos a) (210) a e) (250) se ejecutan en función de un envejecimiento o de la temperatura del convertidor de señal (140) o de un dispositivo de corrección (100) para ejecutar el procedimiento (200) .

4. Procedimiento (200) conforme a una de las reivindicaciones 1 a 3, caracterizado porque en una ejecución del paso b) (220) se escribe el valor de offset en la memoria de valores de error de offset (160) , en donde un valor archivado en esta memoria de valores de error de offset (160) antes de la ejecución del paso b) se sobreescribe mediante la ejecución del paso b) .

5. Procedimiento (200) conforme a la reivindicación 4, caracterizado porque en la ejecución del paso b) (220) , durante la ejecución por primera vez del procedimiento (200) en un dispositivo de corrección (100) , se sobreescribe un valor inicial archivado en la memoria de valores de error de offset (160) durante la producción del dispositivo de corrección (100) .

6. Procedimiento (200) conforme a una de las reivindicaciones 1 a 5, caracterizado porque los pasos a) (210) y c)

(230) se ejecutan mediante la utilización de una unidad de control (130) , que activa un multiplexor (110) para unir la entrada del convertidor de señal (140) al canal de offset (OK) y para contactar la entrada del convertidor de señal

(140) con la magnitud eléctrica a medir.

7. Procedimiento (200) conforme a una de las reivindicaciones 1 a 6, caracterizado porque en los pasos a) (210) y c)

(230) se alimenta una señal analógica a la entrada del convertidor de señal (140) y en los pasos b) (220) y d) (240) se mide una señal digital a la salida del convertidor de señal (140) .

8. Procedimiento (200) conforme a una de las reivindicaciones 1 a 7, caracterizado porque en el paso a (210) se une la entrada del convertidor de señal (140) a una conexión de masa, que se utiliza como canal de offset (OK) .

9. Dispositivo de corrección (100) para la corrección de un error de offset de un convertidor de señal (140) , en donde el dispositivo de corrección (100) comprende las siguientes particularidades:

- un multiplexor (110) para unir una entrada de un convertidor de señal (140) al menos a un canal de medición (MK1-MK4) o a un canal de offset (OK) , en donde el canal de offset (OK) está configurado para proporcionar una tensión de referencia predefinida o una corriente de referencia predefinida;

- una unidad de cálculo (120) , que está configurada para archivar un valor proporcionado por una salida del

convertidor de señal (140) como valor de offset en una memoria de valores de error de offset (160) o archivar un valor proporcionado por una salida del convertidor de señal (140) como valor de medición en una memoria de valores de medición (170) y enlazar el valor de medición archivado en la memoria de valores de medición (170) con el valor de offset archivado en la memoria de valores de error de offset (160) , sobre la base de una estructura de enlace (180) en hardware, y proporcionar el valor obtenido como valor

de medición corregido a una unidad de transmisión (190) ; y

- una unidad de control (130) , que está configurada para conmutar el multiplexor (110) y la unidad de cálculo (120) a un primer o a un segundo modo de funcionamiento,

caracterizado porque la unidad de cálculo (120) presenta un interruptor (150) , que está configurado para unir la salida del convertidor de señal (140) , en respuesta a la señal de la unidad de control (130) , ya sea a la memoria de 15 valores de error de offset (160) o a la memoria de valores de medición (170) , y en donde en el primer modo de funcionamiento la entrada del convertidor de señal (140) está unida al canal de offset (OK) y el valor proporcionado por la salida del convertidor de señal (140) se interpreta en la unidad de cálculo (120) como valor de error de offset y, en el segundo modo operativo, la entrada del convertidor de señal (140) está unida a un canal de medición (MK1

– MK4) y el valor proporcionado por la salida del convertidor de señal (140) se interpreta en la unidad de cálculo 20 (120) como valor de medición.

Patentes similares o relacionadas:

Compensación de deriva, del 20 de Noviembre de 2019, de Teledyne Signal Processing Devices Sweden AB: Un método asociado a un diseño de circuito eléctrico predefinido, en donde cada circuito eléctrico fabricado de acuerdo con el diseño de circuito […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

PROCEDIMIENTO ADAPTATIVO DE CALIBRACIÓN DÍGITAL CONCURRENTE DEL OFFSET EN COMPARADORES EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS), del 18 de Diciembre de 2012, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): El objeto de la presente invención es un procedimiento adaptativo para la calibración del offset de comparadores en convertidores analógico-digitales […]

PROCEDIMIENTO ADAPTATIVO PARA LA ESTIMACIÓN DE LA INL EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS), del 3 de Diciembre de 2012, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): Procedimiento adaptativo para la estimación de la INL en convertidores analógico-digitales (ADCs). Permite caracterizar y testar los convertidores analógico-digitales mediante […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

CIRCUITO MULTIPLICADOR DE UN UNICO BIT CON FUNCION DE AJUSTE DE FASE, del 8 de Abril de 2011, de OSAKI ELECTRIC CO., LTD: Circuito multiplicador de un único bit con función de ajuste de fase.Aumenta la resolución del ajuste de fase. Incluye un elemento aritmético […]

EMPAREJAMIENTO DINAMICO DE ELEMENTOS PARA CONVERTIDORES A/D., del 16 de Marzo de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON: Un método para un emparejamiento dinámico de elementos para un subconvertidor D/A de una etapa de convertidor A/D, caracterizado porque en ese dicho método se incluye el paso […]

SISTEMA DE GENERADOR CON PROCESAMIENTO INTELIGENTE DE SEÑAL DE POSICIÓN, del 30 de Noviembre de 2011, de VESTAS WIND SYSTEMS A/S: Sistema de generador de potencia eléctrica que incluye - un generador de potencia (GEN) que incluye un rotor impulsado por un árbol, - un procesador […]