Procedimiento y aparato para codificar y decodificar datos.

Procedimiento de operación de un transmisor, en el que el procedimiento comprende:

recibir un bloque de transporte concatenado de longitud X; determinar dos tamaños de bloque FEC, contiguos, disponibles Kl-1 y Kl a partir de un grupo de tamaños de bloque FEC, no contiguos, en el que los tamaños de bloque FEC, no contiguos, disponibles se encuentran entre Kmin y Kmax, y en el que Kmin

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2007/078676.

Solicitante: Motorola Mobility, Inc.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 600 North US Highway 45 Libertyville, IL 60048 ESTADOS UNIDOS DE AMERICA.

Inventor/es: CLASSON,BRIAN K, BLANKENSHIP,Yufei W, NIMBALKER,Ajit, BLANKENSHIP,T. Keith.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M13/29 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › combinando dos o más códigos o estructuras de códigos, p. ej. códigos de productos, códigos de producto generalizados, códigos concatenados, códigos internos y externos.

PDF original: ES-2386911_T3.pdf

Fragmento de la descripción:

Procedimiento y aparato para codificar y decodificar datos

Campo de la invencion

La presente invención se refiere, en general, a la codificación y decodificación de datos y, en particular, a un procedimiento y a un aparato para turbo codificar y turbo decodificar datos.

Antecedentes de la invencion

A veces, las transmisiones de datos digitales a traves de enlaces por cable o inalambricos pueden resultar corrompidas, por ejemplo, por ruido en el enlace o canal, por interferencia desde otras transmisiones o por otros factores ambientales. Para combatir los errores introducidos por el canal, muchos sistemas de comunicación emplean tecnicas de corrección de errores para ayudar en la comunicación.

Una tecnica utilizada para la corrección de errores es la turbo codificación de un bloque de información a transmitir. Utilizando dicha tecnica, un codificador en el interior del transmisor de un sistema de comunicación codificara un bloque u de entrada de K bits de longitud en un bloque x de palabra de código de N bits. A continuación, el bloque x de palabra de código es transmitido a traves del canal, posiblemente despues de un procesamiento adicional, tal como intercalamiento de canales, tal como se define en las especificaciones IEEE 802.16e. En el receptor, el turbo decodificador toma el vector y de senal recibido, de longitud N, como entrada, y genera una estimación u del vector u.

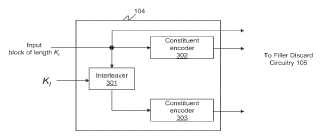

Tfpicamente, el turbo codificador esta compuesto de dos codificadores convolucionales constituyentes. El primer codificador constituyente toma el bloque u de entrada como entrada en su orden original, y el segundo codificador constituyente toma el bloque u de entrada en su orden intercalado despues de pasar u a traves de un turbo intercalador n. La salida x del turbo codificador esta compuesta de los bits sistematicos (iguales al bloque u de entrada) , los bits de paridad del primer codificador constituyente y los bits de paridad del segundo codificador constituyente.

Correspondientemente, el turbo decodificador en el interior del receptor del sistema de comunicación esta compuesto de dos decodificadores convolucionales constituyentes, uno para cada código constituyente. Los decodificadores constituyentes estan separados por el intercalador n y el des-intercalador n -1 correspondiente. Los mensajes en el formato de relación de probabilidad logarftmica (Log-Likelihood Ratios, LLRs) son pasados, iterativamente, entre los decodificadores constituyentes. La decisión u se toma despues de varias iteraciones.

El turbo intercalador n es el componente clave en el diseno del turbo código. Es responsable de la codificación del bloque u de entrada de una manera pseudo-aleatoria, proporcionando, de esta manera, las palabras de código x con una buena distribución de pesos y, por lo tanto, una buena capacidad de corrección de errores. Ademas del rendimiento de decodificación, el turbo intercalador n tiene un impacto considerable sobre la implementación del turbo decodificador en el interior del receptor. Normalmente, el rendimiento de los turbo códigos mejora con una longitud de creciente del intercalador. Sin embargo, se obtiene un retorno decreciente al incrementar el tamano de intercalador. En la practica, el maximo tamano de bloque de la corrección de errores hacia adelante (Forward, Error Correction, FEC) (es decir, el tamano del intercalador) de un turbo código esta limitado a un cierto valor debido a razones de complejidad y retraso. Por lo tanto, si el tamano del bloque de entrada (bloque de transporte concatenado o CTB) es mayor que el maximo tamano de bloque FEC soportado por el turbo código, el CTB es segmentado (por ejemplo, usando una regla de segmentación de bloques de código) en varios segmentos pequenos, cada uno de los cuales es procesamiento, por separado, por el turbo codificador en el transmisor y, correspondientemente, por el turbo decodificador en el receptor.

En algunos sistemas, el turbo código puede estar disenado para soportar solo un pequeno numero de tamanos de bloque FEC por varias razones (por ejemplo, decodificación a alta velocidad, almacenamiento reducido, etc.) . Por lo tanto, existe una necesidad de un procedimiento y un aparato de turbo codificación y turbo decodificación que adapte el CTB a los tamanos de bloque FEC disponibles.

MOTOROLA, FRANCE TELECOM, GET ANO ORANGE: "EUTRA FEC Enhancement', TOOC R1-061050 OF 3GPP TSG RAN WG 1 MEETING #44BIS, 27 de Marzo de 2006 (2006-03-27) , -31 de Marzo de 2006 (2006-03-31) paginas 114, XP002475873 Atenas, Grecia, se refiere a la turbo codificación para sistemas de comunicación 3GPP COMA.

Breve descripcion de los dibujos

La Fig. 1 es un diagrama de bloques de un transmisor.

La Fig. 2 es un diagrama de bloques de un receptor.

La Fig. 3 es un diagrama de bloques del turbo codificador de la Fig. 1.

La Fig. 4 es un diagrama de bloques de un formador de bloques de transporte en el lado del transmisor.

La Fig. 5 es un diagrama de bloques de un ensamblador de bloques de transporte en el lado del receptor.

La Fig. 6 es un diagrama de flujo que muestra el funcionamiento del transmisor de la Fig. 1.

La Fig. 7 es un diagrama de flujo que muestra el funcionamiento del receptor de la Fig. 2.

Descripcion detallada de los dibujos

Con el propósito de abordar la necesidad indicada anteriormente, en la presente memoria se proporciona un procedimiento y un aparato para la turbo codificación y la turbo decodificación.

En una realización, se recibe un bloque de transporte concatenado (CTB) de longitud X y se determinan dos tamanos de bloque FEC, Ki-1 y Ki a partir de un grupo de tamanos de bloque FEC, no contiguos, en la que los tamanos de bloque FEC, no contiguos, estan comprendidos entre Kmin y Kmax, y en la que Kmin <= Ki-1 < Kmax, Kmin <= Ki <= Kmax y en la que Ki-1 y Ki estan basados, adicionalmente, en X. El bloque de transporte concatenado de longitud X es segmentado en C segmentos, cada uno de un tamano sustancialmente igual a Ki-1 o Ki. Una palabra de código FEC para cada uno de los C segmentos es determinada usando los tamanos de bloque FEC Ki o Ki-1, y las C palabras de código FEC son transmitidas a traves del canal.

El beneficio del procedimiento anterior es que reduce la inclusión de bits de relleno requeridos para codificar el CTB, mientras se usa el menor numero de segmentos permitidos por los tamanos de bloque FEC, no contiguos, disponibles. En particular, el procedimiento usa dos tamanos de bloque FEC diferentes (pero contiguos) para minimizar el numero de bits de relleno mientras usa el mfnimo numero de segmentos permitido por los tamanos de bloque FEC, no contiguos, disponibles. Ademas, los tamanos de bloque FEC para los tamanos de segmento y el numero de segmentos pueden ser determinados usando circuiterfa lógica simple.

Previamente a la descripción de la codificación y la decodificación de datos, se establecen las definiciones siguientes para establecer los antecedentes necesarios:

• En aras de la simplicidad de la notación, un bloque de transporte concatenado se refiere al resultado de la concatenación de uno o mas bloques de transporte, despues de anadir una cabecera, tal como bits de CRC, a cada bloque de transporte.

• X denota el tamano de un bloque de transporte concatenado (por ejemplo, la longitud, en bits, del bloque de transporte concatenado) .

• Y denota el numero total de bits de relleno anadidos a un bloque de transporte concatenado.

• C denota el numero de segmentos en el que un bloque de transporte concatenado es segmentado.

• CBSSi denota el tamano del i-esimo segmento de un bloque de transporte concatenado (i = 1, . C) , donde C es el tamano del segmento. CBSS indica el tamano del segmento del bloque de código.

• Ki-1 y Ki indican los tamanos de bloque FEC (por ejemplo, los tamanos para los cuales se ha definido un intercalador interno del turbo código) que pueden ser usados para una codificación FECde los segmentos de un bloque de transporte concatenado.

• Kiabia indica un conjunto de tamanos de bloque FEC, no contiguos, disponibles (tamanos para los cuales se define un intercalador interno del turbo código) .

•... [Seguir leyendo]

Reivindicaciones:

1. Procedimiento de operación de un transmisor, en el que el procedimiento comprende: recibir un bloque de transporte concatenado de longitud X; determinar dos tamanos de bloque FEC, contiguos, disponibles Ki-1 y Ki a partir de un grupo de tamanos de

bloque FEC, no contiguos, en el que los tamanos de bloque FEC, no contiguos, disponibles se encuentran entre Kmin y Kmax, y en el que Kmin <= Ki-1 < Kmax, Kmin <= Ki <= Kmax, y en el que Ki-1 y Ki estan basados, ademas, en X; segmentar el bloque de transporte concatenado de longitud X en C segmentos de tamanos X CBSSi : Ki, para i = 1, ..XCi

X CBSSi : Ki-1, para i = Ci +1, .. C; si Ci-1 >=1; determinar una palabra de código FEC para codificar cada uno de los C segmentos usando tamanos de bloque FEC Ki o Ki-1; y

transmitir las C palabras de código FEC a traves del canal. en el que C = ⎡ X /XKmax ⎤ = Ci + Ci-1, donde Y = CXKi -X, Ci-1 = ⎣YX/X0i ⎦, Ci = C -⎣YX/X0i ⎦, y Ci-1 y Ci son el numero de segmentos que son codificados usando los tamanos de bloque FEC Ki-1 y Ki,

respectivamente, donde Ki es el menor tamano, de entre los tamanos de bloque FEC disponibles, que es mayor

o igual que ⎡ X /XC ⎤, y 0i indica la diferencia entre los tamanos de bloque FEC Ki-1 y Ki contiguos.

2. Un aparato que comprende: circuiterfa de recepción que recibe un bloque de transporte concatenado de longitud X; circuiterfa lógica para determinar dos tamanos de bloque FEC, contiguos, disponibles Ki-1 y Ki, a partir de un

grupo de tamanos de bloque FEC, no contiguos, en el que los tamanos de bloque FEC, no contiguos, disponibles se encuentran entre Kmin y Kmax, y en el que Kmin <= Ki-1 < Kmax, Kmin <= Ki <= Kmax, y en el que Ki-1 y Ki estan basados, ademas, en X;

circuiterfa (102) de segmentación de bloques de código que segmenta el bloque de transporte concatenado de longitud X en C segmentos de tamanos X CBSSi : Ki, para i = 1, ..XCi

X CBSSi : Ki-1, para i = Ci +1, .. C; si Ci-1 >=1; circuiterfa (104) de codificación para la determinación de una palabra de código FEC para cada uno de los C segmentos usando el tamano de bloque FEC Ki o Ki-1; y

circuiterfa (108) de transmisión que transmite las C palabras de código FEC a traves de un canal; en el que C = ⎡ X /XKmax ⎤ = Ci + Ci-1, donde Y = CXKi -X, Ci-1 = ⎣YX/X0i ⎦, Ci = C -⎣YX/X0i ⎦, y Ci-1 y Ci son el numero de segmentos que son codificados usando los tamanos de bloque FEC Ki-1 y Ki,

respectivamente, donde Ki es el menor tamano, de entre los tamanos de bloque FEC disponibles, que es mayor

o igual que ⎡ X /XC ⎤, y 0i indica la diferencia entre los tamanos de bloque FEC Ki-1 y Ki contiguos.

Patentes similares o relacionadas:

Método y dispositivo de codificación, del 15 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación, que comprende: realizar (S101), mediante un extremo de transmisión basado en un polinomio de verificación de redundancia cíclica, […]

Método y aparato para la transmisión inalámbrica de datos sujeta a bloqueos de señal periódicos, del 23 de Octubre de 2019, de Hughes Network Systems, LLC: Un método para la transmisión inalámbrica de una primera corriente de datos, estando la transmisión sujeta a bloqueos periódicos, el método que comprende: segmentar una […]

Procedimiento y sistema para generar códigos de canal, en particular, para un encabezamiento de trama, del 11 de Septiembre de 2019, de POLITECNICO DI TORINO: Un procedimiento para generar un código de canal, en particular, para un encabezamiento de trama, para codificar una señal en la que el valor objetivo […]

Intercalador de bits para un sistema de BICM con códigos de QC-LDPC, del 3 de Julio de 2019, de PANASONIC CORPORATION: Un procedimiento de intercalación de bits para intercalar bits de una palabra de código generada en base a un esquema de codificación de comprobación de paridad de baja densidad […]

Aparato de transmisión de CDMA y método de transmisión de CDMA, del 19 de Junio de 2019, de INVT SPE LLC: Un aparato de transmisión de CDMA que comprende: una sección de control que reconoce tipos de datos incluidos en una pluralidad de elementos de datos y emite: […]

Procedimiento, sistema y dispositivo para detección de errores en redes de comunicación inalámbrica OFDM sin decodificación de corrección de errores hacia delante completa, del 26 de Abril de 2019, de TELEFONICA, S.A.: Un procedimiento para detectar errores en un paquete de información recibido por un receptor OFDM en un sistema de multiplexación por división de frecuencias ortogonales, […]

Intercalador de bits para un sistema de BICM con códigos QC LDPC, del 6 de Marzo de 2019, de PANASONIC CORPORATION: Un procedimiento de entrelazado de bits para entrelazar bits de una palabra de código generada basándose en un esquema de codificación de verificación de paridad de baja densidad […]

Entrelazador de bits para un sistema BICM con códigos QC LDPC, del 28 de Febrero de 2019, de PANASONIC CORPORATION: Un método de entrelazado de bits para entrelazar bits de una palabra de código generada en base a un esquema de codificación con comprobación de paridad de baja densidad […]