PROCEDIMIENTO ADAPTATIVO PARA LA ESTIMACIÓN DE LA INL EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS).

Procedimiento adaptativo para la estimación de la INL en convertidores analógico-digitales (ADCs).

Permite caracterizar y testar los convertidores analógico-digitales mediante la estimación de la No-Linealidad-Integral (Integral-Non-Linearity, INL, en inglés), permitiendo evaluar el efecto de la temperatura y los cambios de polaridad en los convertidores, sin que para ello se interrumpa el camino natural de la conversión analógico-digital de la señal de entrada para inyectar el estímulo o referencia de test específico. Dicho procedimiento es válido para el test y caracterización de cualquier topología de conversión analógico-digital en aplicaciones BIST (de sus siglas en inglés, Built-In Self-Test) concurrentes como no concurrentes.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200930172.

Solicitante: CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC).

Nacionalidad solicitante: España.

Inventor/es: GINÉS ARTEAGA,Antonio José, PERALÍAS MACÍAS,Eduardo José, RUEDA RUEDA,Adoración.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M1/10 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 1/00 Conversión analógica/digital; Conversión digital/analógica (conversión de valores analógicos en, o a partir de una modulación diferencial H03M 3/00). › Calibración o ensayos.

PDF original: ES-2372773_A1.pdf

Fragmento de la descripción:

Procedimiento adaptativo para la estimación de la INL en convertidores analógico-digitales (ADCs) .

Objeto de la invención

El objeto de la presente invención es un procedimiento digital de bajo coste para la estimación de la No-Linealidad-Integral (Integral-Non-Linearity, INL, según sus siglas en inglés) en Convertidores Analógico-Digitales (Analog to Digital Converters, ADC, según sus siglas en inglés) . Dicho procedimiento es válido para el test y caracterización de cualquier topología de conversión analógico-digital.

En el caso particular de un ADC de tipo flash, la invención describe un procedimiento específico para la estimación del offset en sus comparadores analógicos. Este procedimiento específico se aplica directamente a ADCs multi-etapas (conocidos en la bibliografía como ADCs de tipo Pipeline) permitiendo caracterizar la no-linealidad del sub-ADC de cada etapa en dicha estructura, sin modificación alguna en la sección analógica del mismo.

Antecedentes de la invención

El aumento de la complejidad de los sistemas actuales de señal mixta integrado conjuntamente en un único chip (Systems-on-Chip, SoCs, de sus siglas en inglés) introduce unos requerimientos adicionales en la administración y control del consumo de potencia y temperatura. La necesidad de reducir el tiempo de testado y coste de instrumentación requiere soluciones simples que permitan una co-integración de hardware de testado con el propio dispositivo bajo test (DUT, Device Under Test según sus siglas en inglés) . Los requerimientos de estas soluciones de test, denominadas en la bibliografía como BIST (de sus siglas en inglés, Built-In Self-Test) , son especialmente críticos para los convertidores de datos, y más específicamente para ADCs, debido a su naturaleza de señal mixta (véanse las publicaciones D. Lee,

K. Yoo, K. Kim, G. Han, S. Kang, “Code-width testing-based compact ADC BIST circuit”, IEEE Trans. on Circuits and Systems II, vol. 51, no. 11, pp. 603-606, Nov. 2004, así como, H. Xing, H. Jiang, D. Chen and R. Geiger, “A fully digital-compatible BIST strategy for ADC linearity testing”, IEEE International Test Conference, pp. 1-10, Oct. 2007) . Estas soluciones BIST deben detectar la operación correcta o errónea del ADC en un ambiente cambiante, ya que tanto la temperatura como las condiciones de polarización dependen drásticamente de la actividad del sistema completo.

Tradicionalmente, la caracterización estática de estos convertidores se realiza mediante métodos basados en histogramas usando una referencia analógica con mayor resolución que el ADC bajo test (ADCUT, de sus siglas en inglés ADC Under Test) , como se detalla en las publicaciones, IEEE Standards, “IEEE standard for terminology and test methods for analog-to-digital converters”, IEEE Std 1241-2000, 2001, así como, S. M. Max, “Testing high speed high accuracy analog to digital converters embedded in systems on a chip”, IEEE International Test Conference, Paper 29.3, 1999, pp. 763-771. Junto a los inconvenientes de la generación de esta referencia de test dentro del mismo chip (generación on-chip) , y el alto coste y complejidad de la lógica requerida para la evaluación de los histogramas, estos métodos requieren interrumpir el camino natural de la señal analógica de entrada para inyectar el estímulo de test. Por tanto, la evaluación del efecto de la temperatura y cambios en la polarización no se pueden testar sin interrumpir la operación del ADC.

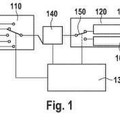

Como su propio nombre indica, un convertidor analógico-digital es un sistema que traslada el valor analógico de una cierta señal x a una representación digital. El código de salida resultante c se codifica, como se muestra en la Fig. 1, mediante una palabra digital de r-bits, c ∈ [0, M], donde r es la resolución del convertidor y el parámetro M define el código máximo dado usualmente por 2r−1.

Cada uno de los M+1 códigos identifica una zona particular dentro del rango de entrada (Full-Scale Range, FSR, según sus siglas en inglés) del ADC (FSR = 2R) . De hecho, el intervalo de la entrada analógica (x) correspondiente al j-ésimo nivel digital, dónde j es un número entero que barre todos los códigos posibles desde 1 hasta M-1, viene dado por,

donde tj define el valor analógico correspondiente a la transición de código para el cual la salida cambia del código j al código j+1.

En un ADC ideal, la diferencia entre dos transiciones consecutivas, también denominada umbrales, es una constante, q = tj+1-tj, llamada cuanto del convertidor o bit menos significativo (Least Significant Bit, LSB, de sus siglas en inglés) que define la mínima resolución discriminada en el proceso del cuantización de la entrada analógica (x) . El valor del cuanto ideal q puede evaluarse en función del la resolución r y la referencia R del convertidor como q = 2R/2r. En la práctica, los efectos de segundo orden en el sistema, como el desapareamiento aleatorio entre componentes, los errores de ganancia y offset, así como, las variaciones dependientes de cambios en la temperatura y polarización, introducen una desviación respecto al comportamiento nominal que puede degradar las prestaciones del ADC. El impacto de estos errores en el comportamiento estático se caracteriza clásicamente mediante la INL (véase el estándar de la IEEE, “IEEE standard for terminology and test methods for analog-to-digital converters”, IEEE Std 1241-2000, 2001) . Como se muestra en la Fig. 2, este parámetro se define como la desviación de cada transición tj respecto a su valor ideal tj (ideal) normalizado usualmente por el LSB del convertidor,

Hay que destacar, que en el caso particular de un ADC de tipo flash la medida de la INL se encuentra directamente relacionada con el offset efectivo (offj) en los comparadores analógicos del ADC, en la forma,

ya que para esta topología existe un comparador específico (Compj) por cada transición tj del ADC. Por tanto, conocida la INL se tiene determinado unívocamente el offset en los comparadores analógicos.

Independientemente de la topología de convertidor considerada, se hace evidente atendiendo a la definición previa que la evaluación de la característica estática del ADC requiere una estimación, ya sea directa o indirecta, de las transiciones representativas tj. Tradicionalmente, este proceso, denominado prelación, se ha realizado de forma estadística considerando una señal de baja frecuencia cuyas propiedades son conocidas a priori (generalmente, una referencia sinusoidal, rampa o triangular, como se muestra en el estándar de la IEEE, “IEEE standard for terminology and test methods for analog-to-digital converters”, IEEE Std 1241-2000, 2001) . Este proceso calcula la probabilidad de la salida evaluando histogramas acumulativos para los códigos excitados. Comparando la probabilidad medida con la esperada para la referencia considerada, se puede identificar el conjunto de transiciones reales, y por tanto la INL.

Debido a su simplicidad y robustez frente a las fuentes de ruido aleatorio, el método de histogramas se ha convertido en uno de los estándares más difundidos para la caracterización estática de ADCs. Sin embargo, esta situación puede ser radicalmente distinta en aplicaciones donde el hardware de testado debe ser co-integrado con el convertidor bajo test (ADCUT) . En estas aplicaciones BIST, las técnicas basadas en histograma presenta dos requerimiento prácticos que es necesario destacar: a) la dificultad de generación en el mismo chip de la referencia analógica con la precisión requerida, b) los requerimiento elevados de la lógica digital para evaluar histogramas acumulativos, ya que se necesita un acumulador digital por cada código de salida.

Adicionalmente, los métodos tradicionales basados en histograma requieren romper el camino natural de la señal analógica de entrada para poder inyectar el estimulo o referencia de test, y por tanto, estos métodos no son válidos para una medida concurrente de la INL. En este documento se entiende por “medida concurrente” una medida que no afecta a la operación normal del circuito bajo test, es decir, no requiere la interrupción de la conversión analógicadigital de la señal de entrada para introducir un estímulo de test específico.

Descripción de la invención

Un primer aspecto de la presente invención describe un procedimiento para la estimación de la INL en convertidores analógico-digitales... [Seguir leyendo]

Reivindicaciones:

1. Procedimiento adaptativo para la estimación de INL de un convertidor analógico-digital (ADCUT) , caracterizado porque comprende la operación inicial de asignar el valor de las transiciones digitales ideales (Ti (ideal) ) a unas estimaciones de las transiciones digitales reales (Ti) , y que además comprende realizar las siguientes operaciones:

obtener un código digital de salida (c) del ADCUT que es una representación digital (c) de una entrada analógica

(x) del ADCUT;

de forma sincronizada, obtener una estimación digital (X) de la entrada analógica (x) más precisa que la representación digital (c) de la operación anterior;

comparar la estimación digital (X) con las estimaciones actuales de las transiciones digitales reales (Tj, Tj+1) donde el índice j viene definido por la representación digital (c) obtenida y:

(ideal)

obtener una estimación de la INL como: INLj = Tj-Tj.

2. Procedimiento de acuerdo con la reivindicación 1, donde el aumento de Tj+1 y la disminución de Tj se llevan a cabo según pasos constantes.

3. Procedimiento de acuerdo con cualquiera de las reivindicaciones 1-2, que comprende realizar un cambio de variable según la ecuación, INLj = Tj-Tj (ideal) u otro similar, de modo que las operaciones se realizan directamente sobre la nueva variable obtenida.

4. Procedimiento de acuerdo con cualquiera de las reivindicaciones 1-3, donde la estimación digital (X) se obtiene a partir de un segundo convertidor analógico-digital ADCtest conectado en paralelo al ADCUT.

5. Procedimiento de acuerdo con la reivindicación 4, donde el ADCtest de la estimación digital (X) se encuentra controlado por un generador de números pseudoaleatorios (RNG) .

6. Procedimiento de acuerdo con cualquiera de las reivindicaciones 1-3, que comprende generar una señal digital en modo no-concurrente que sirve directamente como estimación digital (X) , y transformar dicha señal digital (X) en analógica (x) , empleando un convertidor digital-analógico DAC (DACtest) , para alimentarla al ADCUT.

7. Procedimiento de acuerdo con cualquiera de las reivindicaciones 1-3, donde el ADCUT es un sub-ADC de una de las etapas (STGi) de un ADC de tipo Pipeline, donde:

la representación digital (c) de la entrada analógica (x) de la etapa (STGi) viene dada por el sub-código digital del sub-ADC; y

la estimación digital (X) correspondiente a la entrada analógica (x) del i-ésimo sub-ADC bajo test (ADCUT en la etapa STGi) se obtiene mediante una operación aritmética lógica (con o sin truncación) del sub-código de salida de dicha etapa (c) y de los sub-códigos de salida de las etapas siguientes.

8. Dispositivo para la estimación de INL en un convertidor analógico-digital (ADC) a partir de una representación digital (c) de una entrada analógica (x) obtenida mediante el ADC cuya INL se desea estimar y de una estimación digital (X) de la entrada analógica (x) de mayor precisión que dicha representación digital (c) , caracterizado porque comprende:

a) un banco de registros (RB) , que almacena el valor actual de un conjunto de estimaciones de la INL del ADCUT e inicializa dichos valores a cero;

b) un bloque de comparación digital (CB) , que compara la estimación digital (X) con las estimaciones de las transiciones digitales evaluadas mediante un sumador digital en función de estimación actual de la INL y los valores

(ideal)

conocidos de las transiciones ideales, es decir, (INLj+ Tj, INLj+1+ Tj+1 (ideal) ) , donde el índice j viene definido por el código digital (c) , y genera un señal de habilitación (EN) y control (Sgn) ;

c) un bloque sumador/restador habilitado por la señal EN y controlado por (Sgn) , que aumenta la estimación de

(ideal)

(INLj+1) cuando X > INLj+1+ Tj+1 (ideal) , y disminuye la estimación de (INLj) cuando X < INLj+ Tj.

9. Dispositivo de acuerdo con la reivindicación 8, donde los elementos a, b y c están adaptados para funcionar directamente con Tj según un cambio de variable dado por la ecuación INLj = Tj-Tj (ideal) , y que además comprende los siguientes elementos:

(ideal) ;y

d) un restador que evalúa la INLj = Tj-Tj

e) un banco de registros, que almacena el el resultado del conjunto de estimaciones de la INL (INLj) del ADC.

Patentes similares o relacionadas:

Compensación de deriva, del 20 de Noviembre de 2019, de Teledyne Signal Processing Devices Sweden AB: Un método asociado a un diseño de circuito eléctrico predefinido, en donde cada circuito eléctrico fabricado de acuerdo con el diseño de circuito […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal, del 1 de Agosto de 2013, de ROBERT BOSCH GMBH: Procedimiento para la corrección de un error de offset de un convertidor de señal , en donde elprocedimiento presenta los siguientes […]

Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal, del 1 de Agosto de 2013, de ROBERT BOSCH GMBH: Procedimiento para la corrección de un error de offset de un convertidor de señal , en donde elprocedimiento presenta los siguientes […]

PROCEDIMIENTO ADAPTATIVO DE CALIBRACIÓN DÍGITAL CONCURRENTE DEL OFFSET EN COMPARADORES EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS), del 18 de Diciembre de 2012, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): El objeto de la presente invención es un procedimiento adaptativo para la calibración del offset de comparadores en convertidores analógico-digitales […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

CIRCUITO MULTIPLICADOR DE UN UNICO BIT CON FUNCION DE AJUSTE DE FASE, del 8 de Abril de 2011, de OSAKI ELECTRIC CO., LTD: Circuito multiplicador de un único bit con función de ajuste de fase.Aumenta la resolución del ajuste de fase. Incluye un elemento aritmético […]

EMPAREJAMIENTO DINAMICO DE ELEMENTOS PARA CONVERTIDORES A/D., del 16 de Marzo de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON: Un método para un emparejamiento dinámico de elementos para un subconvertidor D/A de una etapa de convertidor A/D, caracterizado porque en ese dicho método se incluye el paso […]

SISTEMA DE GENERADOR CON PROCESAMIENTO INTELIGENTE DE SEÑAL DE POSICIÓN, del 30 de Noviembre de 2011, de VESTAS WIND SYSTEMS A/S: Sistema de generador de potencia eléctrica que incluye - un generador de potencia (GEN) que incluye un rotor impulsado por un árbol, - un procesador […]