ORDENADOR AUTOCORRECTOR.

Sistema informático autocorrector (100) que comprende: tres o más procesadores (102a,

b, c, ...) que funcionan sincronizados; un controlador (104) adaptado para recibir señales desde los procesadores (102a, b, c...) y que está adaptado además para determinar un valor de la mayoría de las señales recibidas y detectar errores dentro de las señales recibidas; y un módulo de depuración (105) adaptado para resincronizar de forma recurrente los procesadores (102a, b, c, ...) en un punto clave predeterminado, independientemente de la detección de un error reconfigurando los elementos de estado de los procesadores (102a, b, c, ...) a un estado anterior, realizándose la sincronización de acuerdo con el valor de la mayoría

Tipo: Resumen de patente/invención. Número de Solicitud: W04005520US.

Solicitante: MAXWELL TECHNOLOGIES, INC..

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 9244 BALBOA AVENUE,SAN DIEGO, CA 92123.

Inventor/es: HILLMAN,ROBERT,ALLEN, CONRAD,MARK,STEVEN.

Fecha de Publicación: .

Fecha Concesión Europea: 23 de Septiembre de 2009.

Clasificación Internacional de Patentes:

- G06F11/16D

- G06F11/16T6

- G06F11/16T8

- G06F11/18E

- G06F11/18N2

Clasificación PCT:

- G06F1/18 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 1/00 Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76). › Instalación o distribución de energía.

- G06F11/16 G06F […] › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Detección o corrección de errores en un dato por redundancia en el hardware.

Clasificación antigua:

- G06F1/00 G06F […] › Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76).

Fragmento de la descripción:

Ordenador autocorrector.

Esta solicitud está relacionada con la solicitud de patente provisional n.º 60/451,041 (Atty Docket n.º 026471-0201, Express Mail n.º EV003428368), presentada el 28 de febrero de 2003, de la cual se reivindica la prioridad.

Campo de la invención

La presente invención se refiere en general a sistemas informáticos. Más particularmente, la invención se refiere a un sistema informático integrado tolerante a fallos o autocorrector.

Antecedentes

Ciertos entornos requieren que los sistema informáticos en uso sean extremadamente fiables. Al mismo tiempo, algunos de estos entornos pueden ser extremadamente severos, exponiendo los componentes del ordenador a elementos potencialmente catastróficos.

Uno de tales entornos es el entorno espacial. Los sistemas informáticos que pueden ser implantados en el espacio, por ejemplo en la órbita de la Tierra, no están disponibles para un mantenimiento normal y, por tanto, debe estar garantizado que funcionan durante la vida de la nave espacial. Por tanto, un sistema informático montado en una nave espacial debe ser altamente fiable y robusto en cuanto a su tolerancia a fallos, tanto internos como externos.

Además, los objetos en el entorno espacial están sometidos a diversos tipos de radiación que puede ser extremadamente dañina para ciertos componentes de ordenador. Por ejemplo, un elemento de radiación aislado puede causar una perturbación a la que se denomina perturbación de suceso aislado (SEU, "Single Event Upset") en un procesador o una memoria de un sistema informático. Sería deseable que un ordenador en el entorno espacial sea tolerante a tales perturbaciones de suceso aislado.

Desarrollar componentes de ordenador que sean tolerantes individualmente a tales perturbaciones puede ser extremadamente caro e ineficaz. En primer lugar, debido a los largos ciclos de desarrollo, tales componentes carecen generalmente del rendimiento de los componentes del estado de la técnica. Por ejemplo, un procesador diseñado para ser tolerante a la radiación puede tener dos años de antigüedad en el momento que el desarrollo está completo. En aquellos dos años, el estado de la técnica en los procesadores puede haber mejorado el rendimiento de los procesadores en más del doble. Además, hacer que tales componentes sean más robustos frente a fallos puede suponer que sea menor su efectividad en cuanto a coste.

La patente norteamericana n.º 5,903,717 describe un sistema informático para detectar y corregir errores procedentes de SEUs. El sistema incluye una pluralidad de procesadores (CPUs) cuyas salidas son votadas en cada ciclo de reloj. Cualquier señal de salida de CPU que no coincida con la mayoría de las señales de CPU tiene como resultado que se produce una señal de error. El sistema reacciona a las señales de error generando una interrupción en la gestión del sistema. Como reacción a la interrupción en la gestión del sistema como resultado del error detectado, el software inicia una resincronización de la pluralidad de CPUs cuando el error es causado por una perturbación de suceso aislado. La patente norteamericana US-A-5 452 441 describe un sistema y un método para restaurar un sistema de procesadores redundantes módulo N (NMR) en operación cuando uno o más procesadores están en estado fuera de servicio. El sistema NMR comprende N procesadores en el que cada uno tiene un sistema de memoria individual. Una red de interconexión está configurada para recibir datos de todos los N procesadores, y N votantes están conectados entre la red de interconexión y cada uno de los N procesadores para recibir datos de la red de interconexión y votar en los datos destinados para los N procesadores. Las escrituras de datos desde los procesadores activos son reenrutadas a la red de interconexión. Los registradores en la red de interconexión correspondientes a cada procesador reciben los datos de sus procesadores correspondientes y después envían los datos a todos los votantes. Los datos son votados y enviados a todos los N procesadores. Por tanto, las memorias de los procesadores fuera de servicio son restauradas con los procesadores activos mientras que los procesadores activos continúan operando. El reinicio del procesador fuera de servicio es empezado manualmente por un operario del sistema.

Lacopni M.J., Institute of Electrical and Electronics Engineers: "Optimal control of latent fault accumulation", International Symposium on Fault Tolerant Computing. (FTCS), Chicago, junio 20-23, 1989; International Symposium on Fault Tolerant Computing Systems (FTCS), Washington, IEEE Comp. Soc. Press, US, vol. symp.19, 21 de junio de 1989, pág. 382-388, son reseñas del control de la acumulación de errores en los dispositivos de memoria digital que practican con lugares de error potenciales y corrigen errores antes de que se produzca la acumulación. Son analizadas varias políticas de depuración, incluyendo la depuración invariante con tiempo y la que varía con el tiempo.

Sumario de la invención

La invención está definida por las reivindicaciones.

La invención descrita en la presente memoria se refiere a sistemas informáticos que son robustos en su tolerancia a los efectos de sucesos aislados a los que pueden tener que enfrentarse, por ejemplo en el entorno espacial o una nave espacial a altitud elevada. La invención se refiere a un sistema informático que está provisto de varios conjuntos de protecciones frente a fallos que pueden ser causados por la radiación espacial, por ejemplo. Tales protecciones incluyen una o más de las siguientes: múltiples procesadores, múltiples módulos de memoria, lógica de detección y corrección de errores y blindaje mecánico de los componentes. La invención mejora la fiabilidad de un sistema aportando depuración de los componentes con una planificación regular, en lugar de espesar a que sea detectado un error. Por tanto, a los errores que pueden quedar sin detectar durante un periodo prolongado de tiempo no se les permite propagarse y, por tanto, dañar el sistema.

En un aspecto, la invención proporciona un sistema informático tolerante a fallos con tres o más procesadores. Está previsto un controlador para recibir señales desde los procesadores y, usando lógica de votación, determina un valor de señal de la mayoría. El controlador puede detectar un error cuando una señal desde uno de los procesadores difiere de la señal de la mayoría. El sistema está también dotado de un módulo de depuración para resincronizar los procesadores después de que se ha alcanzado un punto clave predeterminado. El punto clave puede ser un intervalo de tiempo predeterminado o cualquier otro suceso que pueda ser definido por el usuario. El valor de señal de la mayoría puede ser usado para la resincronización de los procesadores.

En una realización preferida, el controlador suspende la operación del procesador que produzca una señal que difiera de la señal de la mayoría. Por tanto, el sistema continua la operación con los procesadores restantes. El controlador puede cambiar el punto clave predeterminado, como por ejemplo un intervalo de tiempo, en base a la frecuencia de errores registrados. Por ejemplo, si se registran errores con mayor frecuencia de la esperada, el intervalo de tiempo entre depuraciones puede ser acortado.

El módulo de depuración puede resincronizar los procesadores volcando los elementos de estado de procesador seleccionados para cada procesador dentro de una memoria principal. Esto almacena los datos en la memoria del procesador de manera que puede ser usada para resincronizar los procesadores. El módulo de depuración puede proporcionar a cada procesador datos de restauración. Los datos de restauración corresponden a los datos de la mayoría para elementos de estado seleccionados de los estados del procesador. En otras palabras, los datos en cada elemento de estado, como por ejemplo los registradores, de los estados de procesador para todos los procesadores son usados para determinar un valor de la mayoría. Un valor de la mayoría es determinado para cada elemento de estado seleccionado. Los valores de la mayoría para todos los elementos de estado se corresponden entonces con los datos de restauración usados para resincronizar los procesadores.

El controlador puede incluir matrices de puertas programables en campo (FPGAs) para la lógica de votación. Las FPGAs son dispositivos lógicos que pueden ser programados. Las FPGAs típicas incluyen una gran matriz de puertas. Las FPGAs en el controlador pueden ser individualmente tolerantes a fallos y, por tanto, pueden tolerar fallos tales...

Reivindicaciones:

1. Sistema informático autocorrector (100) que comprende: tres o más procesadores (102a, b, c, ...) que funcionan sincronizados; un controlador (104) adaptado para recibir señales desde los procesadores (102a, b, c...) y que está adaptado además para determinar un valor de la mayoría de las señales recibidas y detectar errores dentro de las señales recibidas; y un módulo de depuración (105) adaptado para resincronizar de forma recurrente los procesadores (102a, b, c, ...) en un punto clave predeterminado, independientemente de la detección de un error reconfigurando los elementos de estado de los procesadores (102a, b, c, ...) a un estado anterior, realizándose la sincronización de acuerdo con el valor de la mayoría.

2. Sistema informático (100) según la reivindicación 1, en el que el punto clave predeterminado es un intervalo de tiempo.

3. Sistema informático (100) según la reivindicación 1, en el que el punto clave predeterminado es un número de ciclos de reloj.

4. Sistema informático (100) según la reivindicación 1, en el que el punto clave determinado está adaptado para ser alcanzado durante un tiempo muerto del sistema operativo.

5. Sistema informático (100) según la reivindicación 1, en el que el controlador (104) está adaptado para registrar un error cuando una señal desde uno o más procesadores (102a, b, c, ...) no coincide con el valor de la mayoría.

6. Sistema informático (100) según la reivindicación 5, en el que el controlador (104) está adaptado para suspender la operación de uno o más procesadores (102a, b, c, ...) que producen una señal que no coincide con el valor de la mayoría.

7. Sistema informático (100) según la reivindicación 5, en el que el controlador (104) está adaptado para cambiar el punto clave predeterminado.

8. Sistema informático (100) según la reivindicación 7, en el que el controlador (104) está adaptado para cambiar el punto clave predeterminado en base a la frecuencia de los errores registrados.

9. Sistema informático (100) según la reivindicación 7, en el que el controlador (104) está adaptado para cambiar el punto clave predeterminado en base los requisitos del sistema.

10. Sistema informático (100) según la reivindicación 1, en el que el módulo de depuración (105) está adaptado para resincronizar los procesadores (102a, b, c...) mediante:

- a) Volcado de los elementos de estado (103a, b, c..) de procesador seleccionados para cada procesador (102a, b, c...) dentro de una memoria principal, y

- b) Provisión a cada procesador (102a, b, c...) de datos de restauración, correspondiendo dichos datos de restauración a un valor de la mayoría de cada uno de dichos elementos de estado (103a, b, c...) de procesador seleccionados.

11. Sistema informático (100) según la reivindicación 10, en el que dichos elementos de estado (103a, b, c, ...) incluyen registradores.

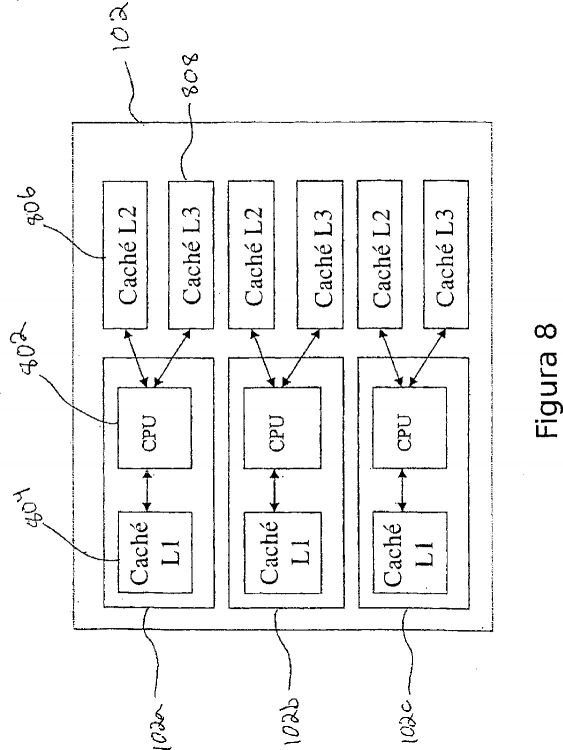

12. Sistema informático (100) según la reivindicación 10, en el que dichos elementos de estado (103a, b, c, ...) incluyen memoria caché (804, 896, 808).

13. Sistema informático (100) según la reivindicación 12, en el que al menos una porción de dicha memoria caché (804, 806, 808) está configurada como de escritura inmediata.

14. Sistema informático (100) según la reivindicación 1, en el que el controlador (104) incluye matrices de puertas programables en campo (FPGAs).

15. Sistema informático (100) según la reivindicación 14, en el que las FPGAs son tolerantes a fallos individualmente.

16. Sistema informático (100) según la reivindicación 1, en el que el controlador (104) incluye circuitos integrados para aplicaciones específicas (ASICs).

17. Sistema informático (100) según la reivindicación 1, en el que cada procesador (102a, b, c, ...) está dotado de un blindaje (506, 508) que mitiga la radiación.

18. Sistema informático (100) según la reivindicación 1, que comprende además: un blindaje (506, 508) para reducir la radiación adaptado para blindar sustancialmente todos los componentes del sistema informático (100).

19. Sistema informático (100) según la reivindicación 1, que comprende además: un módulo de memoria (106) adaptado para almacenar datos, estando dicho módulo de memoria (106) en comunicación con dichos procesadores (102a, b, c, ...).

20. Sistema informático (100) según la reivindicación 19, en el que el módulo de memoria (106) comprende además: tres o cuatro elementos de memoria idénticos (106a, b, c, ...); y un módulo de depuración de memoria adaptado para detectar un error en uno o más de dichos elementos de memoria (106a, b, c, ...) cuando una entrada en una dirección seleccionada de uno o más de dichos elementos de memoria (106a, b, c, ...) difiere de una entrada en dicha dirección seleccionada de una mayoría de dichos elementos de memoria (106a, b, c, ...).

21. Sistema informático (100) según la reivindicación 20, en el que dicho módulo de depuración de memoria está adaptado además para reconfigurar dicho uno o más elementos de memoria en los que se ha detectado un error para contener una entrada en la dirección seleccionada idéntica a dicha entrada en la dirección seleccionada de dicha mayoría de dichos elementos de memoria.

22. Sistema informático (100) según la reivindicación 20, en el que el módulo de depuración de memoria está adaptado para comprobar los errores en cada lectura o escritura en dicha dirección seleccionada.

23. Sistema informático (100) según la reivindicación 20, en el que el módulo de depuración de memoria está adaptado para comprobar los errores a intervalos regulares y reconfigurar una entrada en una dirección de uno o más de dichos elementos de memoria cuando dicha entrada difiere de una entrada en dicha dirección de una mayoría de dichos elementos de memoria.

24. Sistema informático (100) según la reivindicación 19, en el que el módulo de memoria incluye lógica de detección y corrección de errores.

25. Sistema informático (100) según la reivindicación 24, en el que la lógica de detección y corrección de errores incluye corrección de errores de Reed-Solomon.

26. Sistema informático (100) según la reivindicación 1, que es además tolerante a fallos y comprende además: tres o más elementos de memoria idénticos (106a, b, c, ...); y un módulo de depuración de memoria adaptado para detectar un error en uno o más de dichos elementos de memoria (106a, b, c, ..) cuando una entrada en una dirección seleccionada de dicho uno o más elementos de memoria (106a, b, c, ...) difiere de una entrada en dicha dirección seleccionada de una mayoría de dichos elementos de memoria (106a, b, c, ...), en el que dicho módulo de depuración de memoria está adaptado para comprobar errores a intervalos regulares predeterminados.

27. Sistema informático (100) según la reivindicación 26, en el que el módulo de depuración de memoria está adaptado además para reconfigurar dichos uno o más elementos de memoria (106a, b, c, ...) en que es detectado un error para contener una entrada en la dirección seleccionada idéntica a dicha entrada en la dirección seleccionada de dicha mayoría de dichos elementos de memoria (106a, b, c, ...).

28. Sistema informático (100) según la reivindicación 26, en el que el módulo de depuración de memoria está adaptado para comprobar errores en cada lectura o escritura en dicha dirección seleccionada.

29. Sistema informático (100) según la reivindicación 26, en el que el módulo de depuración de memoria comprende: una matriz de puertas AND (402), teniendo cada puerta (402a-c) en dicha matriz (402) como primera entrada una señal de uno de dichos elementos de memoria (106a, b, c, ...), y como segunda entrada una señal desde uno diferente de dichos elementos de memoria (106a, b, c, ...), produciendo cada puerta (402a-c) en dicha matriz (402) una primera salida; y una puerta OR (404) que tiene como entradas la primera salida de cada puerta (402a-c) en dicha matriz de puertas AND (402), teniendo dicha puerta OR (404) una segunda salida; en el que dicho módulo de depuración de memoria está adaptado para detectar un error en base a dicha segunda salida.

30. Método para la autocorrección a través de un ordenador, que comprende la realización de forma recurrente de las siguientes operaciones independientemente de la detección de un error:

- a) Volcado de los elementos de estado de procesador seleccionados desde tres o más procesadores de dicho ordenador que están funcionando sincronizados cuando se llega a un punto clave predeterminado;

- b) Almacenamiento de datos de restauración en una memoria del sistema, siendo dichos datos de restauración indicativos de un valor de la mayoría de cada uno de dichos elementos de estado de procesador seleccionados; y

- c) restaurar dichos elementos de estado de procesador seleccionados a un estado anterior usando dichos datos de restauración.

31. Método según la reivindicación 30, en el que los tres o más procesadores son reiniciados antes de la etapa c).

32. Método según la reivindicación 30, en el que el punto clave predeterminado es un intervalo de tiempo.

33. Método según la reivindicación 30, en el que el punto clave predeterminado es un número de ciclos de reloj.

Patentes similares o relacionadas:

Soporte de unidades de salvaguarda de datos informáticos, del 18 de Marzo de 2020, de FREEBOX (100.0%): Soporte de unidades de salvaguarda de datos informáticos (68A, 68B, 70), configurado para recibir al menos dos tamaños distintos de unidades […]

Conjunto de pantalla y teclado escamoteable para mesas, del 11 de Marzo de 2020, de ALBIRAL DISPLAY SOLUTIONS, S.L.: Conjunto de pantalla y teclado escamoteable para mesas, que comprende: - una estructura de soporte provista de un cerco que define […]

Carcasa estanca, del 26 de Febrero de 2020, de Catalyst Lifestyle Limited: Carcasa protectora para un dispositivo electrónico que comprende: una carcasa principal; una tapa ; estando la carcasa principal y la […]

Lámina de alta densidad con extracción en caliente de componentes para sistema informático, del 11 de Septiembre de 2019, de Bull SAS: Sistema informático que incluye una carcasa de sistema informático provista de un conector, al menos una lámina de componentes para sistema […]

Sistema de conexión de unidades de salvaguarda de datos informáticos, del 4 de Septiembre de 2019, de FREEBOX (100.0%): Sistema de conexión de unidades de salvaguarda (68A, 68B, 70) de datos informáticos a una placa base informática que comprende: - un soporte […]

Arquitectura de estación de base modulable para red de sensores inalámbrica, del 24 de Julio de 2019, de Kerlink: Módem de radio digital para la modulación y la demodulación de una señal digital en función de una tecnología de acceso de radio previamente seleccionada, […]

Bastidor de soporte de tarjeta de expansión de ordenador, del 3 de Abril de 2019, de GIGA-BYTE TECHNOLOGY CO., LTD.: Un bastidor de soporte adaptado para fijar al menos una tarjeta de expansión sobre una placa madre , en el que la placa madre incluye un primer […]

Carcasa piramidal, para ordenador, con gran capacidad de disipación de calor, del 12 de Diciembre de 2018, de PETRUZZI, Vasco: Una carcasa piramidal para recibir un ordenador que incorpora un tablero madre equipado con una CPU, comprendiendo dicha carcasa piramidal […]