Multiplicadores coma flotante y conversores asociados.

Dispositivos para realizar una multiplicación de al menos dos números coma flotante pre-procesados y generar un tercer número coma flotante pre-procesado son propuestos.

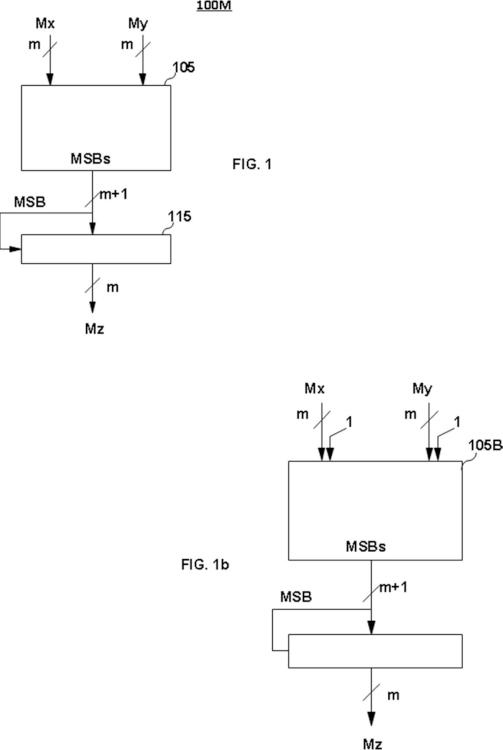

Un formato en coma fija pre-procesado es un formato en coma fija en el que el LSD de todos los números representados exactamente en dicho formato es igual a B/2 (es decir, 1 para base binaria), y el resto son redondeados a uno de estos números. Un formato en coma flotante pre-procesado es un formato en coma flotante en el que la mantisa es un número en coma fija pre-procesado. Para números teniendo una mantisa pre-procesada de m+2 dígitos, el dispositivo comprende un camino de datos del exponente y un camino de datos de la mantisa. El camino de datos de la mantisa comprende una primera entrada para recibir como mucho los m+1 Dígitos Más Significativos (MSDs) de la mantisa pre-procesada del primer número y una segunda entrada para recibir como mucho los m+1 MSDs de la mantisa pre-procesada del segundo número. El camino de datos de la mantisa está configurado para generar como mucho los m+1 MSDs de la mantisa pre-procesada del tercer número.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201430453.

Solicitante: UNIVERSIDAD DE MALAGA.

Nacionalidad solicitante: España.

Inventor/es: HORMIGO AGUILAR,Francisco Javier, VILLALBA MORENO,Julio.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F7/38 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Métodos o disposiciones para efectuar cálculos utilizando exclusivamente una representación numérica codificada, p. ej. utilizando una representación binaria, ternaria, decimal.

PDF original: ES-2546895_A1.pdf

Fragmento de la descripción:

Multiplicadores coma flotante v conversores asociados

La presente invención se refiere al procesamiento de datos y más concretamente a dispositivos para multiplicar números en coma flotante y los conversores asociados a los mismos.

ESTADO DE LA TÉCNICA

En los sistemas de procesado de información, la representación de los números se realiza mediante cadenas binarias. Los bits se pueden organizar en dígitos dependiendo del radix o base.

Los números pueden representarse en varios formatos. Los formatos más utilizados son el formato en coma flotante (FP) y el formato de coma fija (FF). En formato de coma fija, el cual incluye los números enteros, el número de dígitos fraccionarios y dígitos enteros es fijo. En esta representación, los números negativos se representan típicamente en formato de complemento, respecto de la base. Por ejemplo para números binarios se utiliza un formato de complemento a dos.

En coma flotante, el número se compone de la mantisa (Ma), la base (B) y el exponente (Ex). Por lo tanto, el valor (Va) representado sería Va = B * Ma A Ex. Entonces, solamente los números Ma y Ex necesitan almacenarse. El formato estándar IEEE-754 es el más extendido. El estándar define cinco formatos básicos que llevan el nombre de su base numérica y el número de bits usados en su codificación de intercambio. La precisión típica de los formatos binarios básicos es un bit más que la anchura de su mantisa (o mantisa). El bit de precisión extra proviene de un bit a uno implícito (oculto) en la parte más significativa. El número en coma flotante típico estará normalizado tal que el bit más significativo será un uno. Si conocemos que el

bit más significativo es uno, entonces no se necesita codificarlo en el formato de intercambio.

Los sistemas para realizar operaciones entre estos números pueden usar una pluralidad de unidades funcionales. Estas unidades pueden realizar transformaciones numéricas como operaciones aritméticas, conversiones de formato, evaluación de funciones, etc. El formato utilizado para representar los números con los que estos circuitos operan define completamente el diseño de estos circuitos y, por tanto, sus parámetros fundamentales de eficiencia tales como precisión, rango, velocidad, área y consumo. En consecuencia, el formato utilizado en estos sistemas influye enormemente en su eficiencia.

Dos circuitos básicos que se requieren en la mayoría de tales unidades funcionales son los circuitos de redondeo y los circuitos para complemento a dos.

Los circuitos de redondeo se utilizan cuando es necesario reducir el número de dígitos significativos, tanto en números en formato de coma fija como en la mantisa de números en formato de coma flotante. El circuito que realiza la función de complemento a dos se utiliza para cambiar el signo del número. Cualquier mejora en la eficiencia de estos dos circuitos afecta directamente a la eficiencia de la mayoría de las unidades funcionales que los incluyan.

Para realizar el complemento a la base de un número, primero se realiza el complemento a la base menos uno, una operación que se realiza sobre todos los dígitos en paralelo. Posteriormente se le suma al número una unidad-en- el-último lugar (ULP). En el caso binario, para que un circuito que lleva a cabo el complemento a dos de un número de N bits serían necesarios N inversores y un sumador de N bits. En el caso de una operación de resta (X-Y = X+(-Y)), que en realidad consiste en una suma con el complemento a dos del sustraendo, el bit de entrada de acarreo del sumador se suele utilizar para

añadir el ULP. Sin embargo, esto no significa que cada vez que se requiere llevar a cabo el complemento a dos el motivo es una resta. Tales casos son la operación de valor absoluto o la suma/resta de números en representación signo-magnitud, una representación típicamente usada en coma flotante.

Con respecto a los circuitos de redondeo, se utilizan varias formas de redondeo. Una que demuestra importantes propiedades y es la más utilizada es el "redondeo al par más cercano". En este modo, el valor que se utiliza como valor final es el valor que está más cerca del valor real y, en caso de empate, el valor par. Usando este tipo de redondeo, se obtiene un error inferior a +-0.5ULP y no presenta ningún sesgo en los errores.

Dado un número de D1 dígitos, para realizar una operación de redondeo a D2 dígitos, asumiendo D1 > D2, D1-D2 dígitos deben desecharse. Para que el redondeo sea al número más cercano, es importante examinar el valor del dígito más significativo de los que necesitan ser desechados (MD) y el dígito menos significativo de los que quedan (LD):

Si MD < (B/2) entonces simplemente dichos dígitos son descartados.

Si MD > (B/2) entonces dichos dígitos se descartan y se añade el valor uno al dígito menos significativo que permanece.

Si MD = (B/2) entonces se debe verificar si alguno de los dígitos a descartarse no es cero (sticky bit). Si es así, entonces el redondeo se realiza según el segundo caso. Si todos son cero, entonces si el dígito LD es par entonces el redondeo se realiza según el primer caso y si es impar según el segundo caso.

Por lo tanto, el circuito básico para implementar este tipo de redondeo requiere un sumador para sumar uno si es necesario y un circuito para calcular el sticky bit.

Los circuitos de complemento a la base y redondeo son necesarios en las unidades funcionales tales como sumadores, multiplicadores, divisores,

unidades FMAD, operadores de valor absoluto, conversores de formato o conversores de precisión etc. El coste adicional, por ejemplo en el área o retardo, que plantean dichos circuitos en las mencionadas unidades funcionales es generalmente substancial, sobre todo porque están típicamente en la vía crítica.

En el estado de la técnica anterior se han hecho varios intentos para reducir los efectos de estos cálculos, es decir el complemento a dos, el cálculo del sticky bit y redondeo. En ciertos documentos del estado de la técnica se ha propuesto pre-calcular el sticky bit o quitar estas operaciones de la vía crítica o reducir el número total de operaciones de redondeo necesarias o combinar redondeo y complemento a dos.

Sería deseable tener circuitos y métodos que reduzcan el coste en área, retardo y consumo de los circuitos de redondeo al más cercano y/o de complemento a la base.

La presente invención se refiere a varios métodos y dispositivos para evitar o al menos reducir parcialmente este problema.

RESUMEN

La presente descripción se refiere a configuraciones y circuitos para operaciones en coma flotante que implementan técnicas para codificar números con objeto de realizar funciones de redondeo al más cercano y complemento a la base sin la necesidad de realizar una suma. Por tanto, los sistemas que usen el tipo de codificación propuesto y que requieran estas operaciones podrían simultáneamente reducir área, retardo y consumo de potencia.

Con este fin, la presente descripción se centra en el diseño de sistemas digitales de procesamiento de información más eficientes (más rápidos, menor coste, menor consumo de energía) mediante el uso de una nueva familia de formatos o una modificación de los formatos de codificación numérica, aplicable a la mayoría de los formatos actuales, lo que implica cambios en los circuitos que procesan dichos formatos. Estos formatos simplifican drásticamente los circuitos para el redondeo al más cercano y complemento a la base, sin afectar negativamente al resto del circuito.

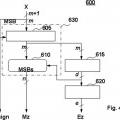

En un primer aspecto, se propone un dispositivo para realizar una multiplicación de al menos dos números en coma flotante pre-procesados y generar un tercer número en coma flotante pre-procesado. Cada número tiene una mantisa de m+2 dígitos. El dispositivo comprende un camino de datos del exponente y un camino de datos de la mantisa. El camino de datos de la mantisa comprende una primera entrada para recibir como mucho los m+1 Dígitos Más Significativos (MSDs) de la primera mantisa pre-procesada y una segunda entrada para recibir como mucho los m+1 MSDs de la segunda mantisa pre-procesada. El camino de datos de la mantisa está configurado para generar como mucho los m+1 MSDs de la mantisa del tercer número pre-procesado. El Dígito Menos Significativo (LSD) de todas las mantisas pre-procesadas es igual a B/2, siendo B la base del sistema de representación numérica utilizado. En el caso de que el sistema numérico sea binario, entonces B=2 y el LSD es igual a uno.

Una ventaja del dispositivo es la capacidad de realizar las operaciones mencionadas sin usar explícitamente el LSD de la mantisa de los números en coma flotante. Para... [Seguir leyendo]

Reivindicaciones:

1. Dispositivo para realizar una operación de multiplicación de al menos dos 5 números coma flotante pre-procesados y generar un tercer número coma flotante pre-procesado, en el que cada número tiene una mantisa de M+2 dígitos, el dispositivo comprende:

un camino de datos del exponente y

un camino de datos de la mantisa, que comprende

una primera entrada para recibir como mucho los M+1 Dígitos

Más Significativos (MSDs) de la mantisa pre-procesada del primer número,

una segunda entrada para recibir como mucho los M+1 MSDs de la mantisa pre-procesada del segundo número,

en el que el camino de datos de la mantisa está configurado 15 para generar como mucho los M+1 MSDs de la mantisa del tercer número pre-procesado, donde el Dígitos Menos Significativo (LSD) de todas las mantisas pre-procesadas es igual a B/2, siendo B la base del sistema de representación numérica.

2. Dispositivo según reivindicación 1, en el que el camino de datos del exponente está configurado para

calcular el exponente de salida;

calcular el signo de salida; y

2 5 detectar y resolver excepciones y valores especiales.

3. Dispositivo según reivindicación 1 ó 2, en el que dichas mantisas preprocesadas están normalizadas y dichas primera y segunda entradas están configuradas para recibir los m MSDs fraccionarios de la primera y segunda mantisa pre-procesada, respectivamente.

4. Dispositivo según cualquiera de las reivindicaciones 1 a 3, en el que comprende además una tercera entrada para recibir el LSD de dicha primera y segunda mantisa pre-procesada.

5. Dispositivo según cualquiera de las reivindicaciones 1 a 3, en el que

además comprende una tercera entrada con el valor B/2.

6. Dispositivo según cualquiera de las reivindicaciones 1 a 5, donde B=2 y los dígitos son bits.

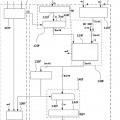

7. Dispositivo según reivindicación 6, en el que el camino de datos de la mantisa comprende

un módulo de multiplicación en coma fija preparado para recibir, en una primera y una segunda entrada, como mucho los M+1 MSBs de la 2 0 mantisa del primer y segundo número pre-procesado, respectivamente, y

generar los M+2 MSBs del valor que corresponde a la operación de multiplicación entre dichas mantisas pre-procesadas.

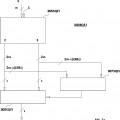

8. Dispositivo según reivindicación 7, en el que el módulo de multiplicación 2 5 en coma fija comprende

un multiplicador redundante configurado para recibir, en una primera y una segunda entrada, como mucho los M+1 MSBs de la mantisa del primer y

segundo número pre-procesado, respectivamente, y generar, en un formato

de representación redundante, los 2M+3 MSDs del valor correspondiente a la operación de multiplicación entre dichas mantisas pre-procesadas;

un módulo de conversión, conectado a la salida de dicho módulo de multiplicación, configurado para recibir los M+2 MSDs de la salida de dicho 5 multiplicador redundante y un bit de acarreo, y generar una salida de M+2 bits correspondiente a la conversión del valor redundante recibido a formato de representación no redundante;

un módulo de red de acarreo configurado para recibir los M+1 LSDs de la salida de dicho multiplicador redundante y generar dicho bit de acarreo 10 correspondiente al acarreo de salida de la conversión de los M+1 LSDs de la salida de dicho multiplicador redundante a representación no redundante.

9. Dispositivo según reivindicación 8, en el que el multiplicador redundante comprende

un generador de productos parciales configurado para recibir, en una

primera y una segunda entrada, como mucho los M+1 MSBs de la mantisa del primer y segundo número pre-procesado, respectivamente, y generar sus productos parciales en una salida

un árbol de compresores, con una primera entrada conectada a la 2 0 salida del generador de productos parciales y una segunda entrada configurada para recibir como mucho los M+1 MSBs de la mantisa del primer y segundo número pre-procesado pre-procesa, dicho árbol de compresores configurado para generar, en una representación redundante, los 2M+3 MSDs de un valor correspondiente a la operación de multiplicación entre dichas 25 mantisas pre-procesadas en una salida.

10. Dispositivo según cualquiera de las reivindicaciones 7 a 9 en el que el módulo de multiplicación en punto fijo comprende además una tercera entrada con el valor uno.

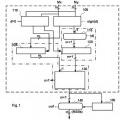

11. Dispositivo según cualquiera de las reivindicaciones 7 a 10 en el que 5 comprende además un módulo de normalización con una entrada conectada

a la salida del módulo de multiplicación en coma fija, donde el módulo de normalización está configurado para generar como mucho los M+1 MSBs de la tercera mantisa pre-procesada seleccionando los M+1 LSBs de su entrada si el MSB es igual a cero o los M+1 MSBs si dicho bit es igual a uno.

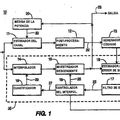

12. Dispositivo según cualquiera de las reivindicaciones anteriores, en el que comprende además un conversor de números coma fija pre-procesados a números coma flotante pre-procesados para convertir un número coma fija de N+2 bits a un número coma flotante con una mantisa de M+2 bits.

13. Dispositivo según reivindicación 12 en el que dicho conversor de números coma fija pre-procesados a números coma flotante pre-procesados comprende:

un calculador de cantidad de desplazamiento,

2 0 un módulo para calcular el exponente, con una primera entrada para

recibir la primera cantidad de desplazamiento del calculador de cantidad de desplazamiento, y una salida para generar el exponente del número coma flotante pre-procesado; y

un módulo de normalización con

2 5 una primera entrada para recibir los N MSBs de los N+1 LSBs

del número coma fija pre-procesado y una segunda para recibir la primera cantidad de desplazamiento; dicho módulo de normalización configurado para desplazar a la izquierda dichos N MSBs de acuerdo con dicha cantidad

de desplazamiento, completando el MSB de las posiciones vacantes con cero

y el resto con unos, o el MSB con uno y el resto con ceros, para generar como mucho los M+1 MSBs de la mantisa,

mientras que el signo del número coma flotante pre-procesado corresponde al MSB del número coma fija pre-procesado.

14. Dispositivo según reivindicación 13 en el que el módulo de normalización está configurado además para, completar dichas posiciones vacantes, aleatoriamente, basándose en un bit seleccionado, o en una combinación de bits seleccionados.

15. Dispositivo según reivindicación 13 ó 14, en el que dicho módulo de normalización está configurado además para generar selectivamente el complemento a uno del resultado de dicho desplazamiento.

16. Dispositivo según cualquiera de las reivindicaciones anteriores, en el que comprende además un conversor de números coma fija no procesados a números coma flotante pre-procesados, para convertir un número coma fija no procesado de R bits a un número coma flotante pre-procesado con una mantisa de M+2 bits. El conversor comprende:

un calculador de cantidad de desplazamiento

un módulo de normalización configurado para recibir los R bits del número en coma fija no procesado y generar como mucho los M+1 MSBs de la mantisa del número pre-procesado en coma flotante,

un calculador de exponentes con una primera entrada para recibir la segunda cantidad de desplazamiento proveniente del calculador de cantidad de desplazamiento y una salida para generar el exponente del número pre- procesado en coma flotante,

en el que el signo del número pre-procesado en coma flotante se corresponde con el MSB del número en coma fija no procesado.

17. Dispositivo según la reivindicación 16, en el que el módulo de 5 normalización comprende una primera entrada para recibir los R bits del número no procesado en coma fija y una segunda entrada para recibir la segunda cantidad de desplazamiento, donde el módulo de normalización está configurado para generar un valor que corresponde a como mucho los M+1 MSB de la mantisa pre-procesada mediante el desplazamiento a la izquierda 10 de los R-2 MSBs de los R-1 LSBs de la primera entrada seguida hacia la derecha por un bit a cero y rellenando las posiciones vacantes con el valor del LSB de la primera entrada.

18. Dispositivo según la reivindicación 17, en el que el módulo de 15 normalización está configurado además para generar selectivamente el complemento a uno de dicho valor generado si la entrada es negativa.

19. Dispositivo según cualquiera de las reivindicaciones 14,15,17,0 18, en el que el módulo de normalización comprende un desplazador variable 2 0 configurado para recibir un bit para completar las posiciones vacantes.

20. Dispositivo según la reivindicación 19, en el que dicho desplazador variable comprende un número de sucesivos multiplexores que es igual al primer entero mayor o igual que el logaritmo en base 2 de la máxima cantidad 25 de desplazamiento [log2(máxima cantidad de desplazamiento)], con cada multiplexor configurado para efectuar una operación de desplazamiento a la izquierda de 2A¡ posiciones, ¡e[0, número de multiplexores-1], y cada multiplexor configurado para completar las posiciones vacantes usando el valor de dicho bit recibido.

21. Dispositivo según la reivindicación 16, en el que el módulo de normalización comprende una primera entrada para recibir los R bits del número en coma fija no procesado y una segunda entrada para recibir la 5 segunda cantidad de desplazamiento, donde el módulo de normalización está configurado para generar un valor que se corresponde con como mucho los M+1 MSBs de la mantisa pre-procesada mediante el desplazamiento a la izquierda de los R-1 LSBs de la primera entrada.

22. Dispositivo según la reivindicación 21, en el que el módulo de

normalización está configurado además para generar selectivamente el complemento a uno del resultado de la mencionada operación de desplazamiento.

23. Dispositivo según a cualquiera de las reivindicaciones 13 a 22, en el que

el calculador de exponentes está configurado para decrementar, de acuerdo a la segunda cantidad de desplazamiento, un valor base para obtener el exponente.

2 0 24. Dispositivo según la reivindicación 23, en el que el calculador de

exponentes además está configurado para detectar desbordamientos o valores cero y provocar que el conversor genere la salida correspondiente.

25. Dispositivo según cualquiera de las reivindicaciones anteriores, en el que 25 comprende además un conversor de números coma flotante pre-procesados a números coma fija no procesados para convertir el tercer número en coma flotante pre-procesado a un número en coma fija no procesado.

26. Dispositivo según la reivindicación 25, en el que cuando el número en coma fija no procesado tiene H+1 bits, el conversor comprende un conversor de números coma flotante pre-procesados a números coma fija preprocesados con una salida de H+2 bits conectada a un módulo de redondeo.

27. Dispositivo según reivindicación 26, en el que el módulo de redondeo comprende un sumador; dicho sumador está configurado para recibir, en una entrada, los H+1 MSBs de la salida del mencionado conversor de números coma flotante pre-procesados a números coma fija pre-procesados e i o incrementar dicha entrada si el LSB de dicha salida es igual a 1.

28. Dispositivo según cualquiera de las reivindicaciones anteriores, que comprende además un conversor de números coma flotante pre-procesados a números coma flotante pre-procesados para convertir un número inicial 15 coma flotante con una mantisa de J+2 bits a un subsecuente número coma flotante, donde dicho subsecuente número coma flotante tiene, al menos, un tamaño de mantisa diferente.

29. Dispositivo según la reivindicación 28, en el que cuando el subsecuente 2 0 número en coma flotante pre-procesado tiene una mantisa con J+2-P bits, P<J+1, entonces el conversor comprende:

una unidad de redondeo para eliminar los P+1 LSBs de los J+2 bits de la mantisa inicial pre-procesada, para generar como mucho J+1-P MSBs de la mantisa del subsecuente número en coma flotante pre-procesado,

donde el LSB de la mantisa del subsecuente número coma flotante

pre-procesado es igual a 1,

y un calculador de exponentes para generar el exponente del subsecuente número en coma flotante pre-procesado.

30. Dispositivo según la reivindicación 28, en el que cuando el subsecuente número en coma flotante pre-procesado tiene una mantisa con J+2+Q bits, entonces el conversor comprende:

un módulo de rellenado, configurado para recibir como mucho los J+1

MSBs de la mantisa del número en coma flotante pre-procesado inicial y generar como mucho los J+Q+1 MSBs de la mantisa del subsecuente número en coma flotante pre-procesado fijando el MSB de los Q LSBs a uno o a cero y los restante Q-1 bits de dichos Q LSBs al complemento del mencionado 10 MSB, mientras los como mucho J+1 MSBs de la mantisa del subsecuente número en coma flotante pre-procesado son los mismos que los como mucho J+1 MSBs de la mantisa del número en coma flotante pre-procesado inicial, y

un calculador de exponentes para generar el exponente del 15 subsecuente número en coma flotante pre-procesado.

31. Dispositivo según la reivindicación 30, en el que el módulo de rellenado está configurado para fijar aleatoriamente dicho MSB basándose en el valor de un bit seleccionado, o de una combinación de bits seleccionados.

32. Dispositivo según cualquiera de las reivindicaciones anteriores, en el que comprende además un conversor de números coma flotante pre-procesados a números coma fija pre-procesados para convertir un número en coma flotante con una mantisa de F+2 bits en un número en coma fija.

33. Dispositivo según la reivindicación 32, en el que el número en coma fija pre-procesado tiene L bits, con L<F+4, el conversor comprende:

un calculador de la cantidad de desplazamiento que recibe el exponente del número en coma flotante pre-procesado en una entrada y que genera una cantidad de desplazamiento en una salida,

un módulo de desplazamiento con una primera entrada para recibir los 5 L-1 MSBs de la mantisa del número en coma flotante pre-procesado y una

segunda entrada acoplada a la salida del calculador de cantidad de desplazamiento y una tercera entrada para recibir el signo del mencionado número en coma flotante, para generar los L-1 MSBs del número en coma fija pre-procesado en una salida.

34. Dispositivo según la reivindicación 33, en el que el módulo de desplazamiento comprende un desplazador aritmético a la derecha acoplado a un inversor de bit condicional.

35. Dispositivo según reivindicación 32, en el que cuando el número en coma

fija pre-procesado comprende F+C+3 bits, C>0, el conversor comprende:

un calculador de cantidad de desplazamiento que recibe el exponente del número en coma flotante pre-procesado en una entrada y que genera una cantidad de desplazamiento en una salida,

2 0 un módulo de desplazamiento aritmético a la derecha con una primera

entrada conectada a la salida del calculador de desplazamiento, configurado para generar los F+C+2 MSBs del número en coma fija pre-procesado mediante el desplazamiento aritmético a la derecha de un valor intermedio de F+C+2 bits formado, de izquierda a derecha, por el bit de signo, los F+1

2 5 MSBs de la mantisa del número en coma flotante pre-procesado, y el MSB

de los C LSBs puesto a cero y el resto a uno, o el MSB de los C LSBs puesto a uno y el resto a cero.

36. Dispositivo según la reivindicación 35, en el que el módulo de desplazamiento aritmético a la derecha está configurado para poner aleatoriamente dicho MSB de los C LSBs del mencionado valor intermedio de F+C+2 bits en base al valor de un bit seleccionado, o de una combinación de 5 bits seleccionados.

37. Dispositivo según las reivindicaciones 35 o 36, en el que el módulo de desplazamiento aritmético a la derecha está configurado para generar selectivamente el complemento a uno del resultado de la mencionada 10 operación de desplazamiento.

38. Dispositivo según cualquiera de las reivindicaciones anteriores, comprende además un conversor de números en coma flotante no procesados a números en coma flotante pre-procesados para convertir un 15 número en coma flotante no procesado con una mantisa de E+2 bits en un número en coma flotante pre-procesado.

39. Dispositivo según la reivindicación 38, en el que cuando el número en coma flotante pre-procesado tiene una mantisa de E+2-D bits, D<E+1 2 o entonces el conversor comprende:

una unidad de redondeo configurada para eliminar los D+1 LSBs de la mantisa del número en coma flotante no procesado, para generar como mucho los E+1-D MSBs de la mantisa del número coma flotante pre- procesado, donde el LSB de la mantisa del número en coma flotante pre- 25 procesado es igual a uno, y

un calculador de exponentes para generar el exponente del número en coma flotante pre-procesado.

40. Dispositivo según la reivindicación 39, en el que la unidad de redondeo está configurada además para, selectivamente, poner a cero el segundo LSB de la mantisa del número en coma flotante pre-procesado si todos los D+1 LSBs de la mantisa del número en coma flotante no procesado son iguales a 5 cero.

41. Dispositivo según la reivindicación 38, en el que cuando el número en coma flotante pre-procesado tiene una mantisa de E+2+G bits entonces el conversor comprende:

un módulo de rellenado, configurado para recibir como mucho los E+2

bits de la mantisa del número en coma flotante no procesado y generar como mucho los E+G+1 MSBs de la mantisa del número en coma flotante pre- procesado fijando como mucho los E+2 MSBs del número en coma flotante pre-procesado al mismo valor que como mucho los E+2 bits de la mantisa del

número en coma flotante no procesado y los restantes bits a cero, donde el LSB de la mantisa del número en coma flotante pre-procesado es igual a uno, y

un calculador de exponentes configurado para generar el exponente del número en coma flotante pre-procesado.

42. Dispositivo según la reivindicación 41, en el que el módulo de rellenado está configurado además para generar selectivamente el valor correspondiente a restar uno del segundo LSB de la mencionada mantisa generada, cuando un bit seleccionado, o una combinación de bit 2 5 seleccionados, de la mantisa no procesada de entrada es igual a uno.

43. Dispositivo según cualquiera de las reivindicaciones anteriores, comprende además un conversor de números coma flotante pre-procesados

a números coma flotante no procesados para la conversión de un número en

coma flotante pre-procesado con una mantisa de U+2 bits en un número en coma flotante no procesado.

44. Dispositivo según la reivindicación 43, en el que cuando el número en 5 coma flotante no procesado tiene una mantisa de U+2-V bits, V<U, entonces el conversor comprende:

un módulo de redondeo, configurado para recibir como mucho los U+3-V MSBs de la mantisa del número en coma flotante pre-procesado y generar como mucho los U+2-V bits de la mantisa del número en coma 10 flotante no procesado,

un calculador de exponentes configurado para generar el exponente del número en coma flotante no procesado.

45. Dispositivo según la reivindicación 44, en el que el módulo de redondeo 15 comprende un sumador; dicho sumador está configurado para recibir, en una entrada, como mucho los U+2-V MSBs de la mantisa del número en coma flotante pre-procesado e incrementar dicho valor de entrada si el (U+3-V)- ésimo MSB de dicha mantisa es igual a 1, y generar una instrucción para el calculador de exponentes, si se produjera un desbordamiento.

46. Dispositivo según las reivindicaciones 44 ó 45, en el que el calculador de exponentes está configurado, además, para incrementar el exponente de salida cuando se genera la mencionada instrucción del módulo de redondeo.

2 5 47. Dispositivo según la reivindicación 43, en el que cuando el número en

coma flotante no procesado tiene una mantisa de U+2+W bits entonces el conversor comprende:

un módulo de rellenado, configurado para recibir como mucho los U+1 MSBs de la mantisa del número en coma flotante pre-procesado y generar como mucho los U+W+2 bits de la mantisa del número en coma flotante no procesado poniendo el MSB de los W+1 LSBs a uno y los restantes bits a 5 cero, y

un calculador de exponentes configurado para generar el exponente del número en coma flotante pre-procesado.

Patentes similares o relacionadas:

Procedimiento de decodificación de imágenes, del 16 de Diciembre de 2015, de HITACHI, LTD.: Procedimiento de decodificación de imágenes de una secuencia de imágenes, que comprende las etapas siguientes:

almacenar una imagen previamente codificada […]

Procedimiento de decodificación de imágenes, del 16 de Diciembre de 2015, de HITACHI, LTD.: Procedimiento de decodificación de imágenes de una secuencia de imágenes, que comprende las etapas siguientes:

almacenar una imagen previamente codificada […]

UNIDADES ARITMÉTICAS Y CONVERSORES ASOCIADOS, del 1 de Octubre de 2015, de UNIVERSIDAD DE MALAGA: Dispositivos para sumar números en coma flotante, dispositivos para multiplicar números en coma flotante, dispositivos para realizar operaciones de multiplicación-suma […]

Unidades aritméticas en coma fija y conversores asociados, del 29 de Septiembre de 2015, de UNIVERSIDAD DE MALAGA: Dispositivos para realizar una operación deseada de al menos un primer número en coma fija pre-procesado con N+1 dígitos, para generar al menos un segundo número […]

Unidades aritméticas en coma fija y conversores asociados, del 29 de Septiembre de 2015, de UNIVERSIDAD DE MALAGA: Dispositivos para realizar una operación deseada de al menos un primer número en coma fija pre-procesado con N+1 dígitos, para generar al menos un segundo número […]

Sumadores coma flotante y conversores, del 29 de Septiembre de 2015, de UNIVERSIDAD DE MALAGA: Dispositivos para realizar una operación deseada de suma o resta de al menos dos números coma flotante pre-procesados y generar un tercer número […]

Sumadores coma flotante y conversores, del 29 de Septiembre de 2015, de UNIVERSIDAD DE MALAGA: Dispositivos para realizar una operación deseada de suma o resta de al menos dos números coma flotante pre-procesados y generar un tercer número […]

Dispositivos coma flotante y conversores, del 29 de Septiembre de 2015, de UNIVERSIDAD DE MALAGA: Dispositivos para convertir números a y desde un formato pre-procesado son propuestos. Un formato en coma fija pre-procesado es un formato en […]

Dispositivos coma flotante y conversores, del 29 de Septiembre de 2015, de UNIVERSIDAD DE MALAGA: Dispositivos para convertir números a y desde un formato pre-procesado son propuestos. Un formato en coma fija pre-procesado es un formato en […]

Dispositivos para operaciones de multiplicación-suma fusionadas en coma flotante y conversores asociados, del 29 de Septiembre de 2015, de UNIVERSIDAD DE MALAGA: Dispositivos para realizar una operación de multiplicación-suma fusionada en coma flotante entre tres números coma flotante pre-procesados para generar un cuarto número coma […]

Dispositivos para operaciones de multiplicación-suma fusionadas en coma flotante y conversores asociados, del 29 de Septiembre de 2015, de UNIVERSIDAD DE MALAGA: Dispositivos para realizar una operación de multiplicación-suma fusionada en coma flotante entre tres números coma flotante pre-procesados para generar un cuarto número coma […]

Método y aparato para mejorar la discriminación de ruido usando un factor de atenuación, del 16 de Julio de 2014, de DOLBY LABORATORIES LICENSING CORPORATION: Un método para mejorar la discriminación de ruido en un sistema que tiene una pluralidad de sensores (A, B) que generan cada uno una señal de entrada de sensor representada […]

Método y aparato para mejorar la discriminación de ruido usando un factor de atenuación, del 16 de Julio de 2014, de DOLBY LABORATORIES LICENSING CORPORATION: Un método para mejorar la discriminación de ruido en un sistema que tiene una pluralidad de sensores (A, B) que generan cada uno una señal de entrada de sensor representada […]

METODO DE INTERPOLADOR OPTIMO Y APARATO PARA EL AJUSTE DE TEMPORIZACION DIGITAL, del 16 de Abril de 2008, de INTERDIGITAL TECHNOLOGY CORPORATION: Un sincronizador de temporización digital de un receptor para la sincronización de temporización de un transmisor en un sistema de comunicaciones […]

METODO DE INTERPOLADOR OPTIMO Y APARATO PARA EL AJUSTE DE TEMPORIZACION DIGITAL, del 16 de Abril de 2008, de INTERDIGITAL TECHNOLOGY CORPORATION: Un sincronizador de temporización digital de un receptor para la sincronización de temporización de un transmisor en un sistema de comunicaciones […]