MÉTODO PARA LA DETERMINACIÓN DE UN RETRASO DE SEÑAL ASIMÉTRICO DE UN CAMINO DE SEÑAL DENTRO DE UN CIRCUITO INTEGRADO.

Método para la determinación de un retraso de señal asimétrico de un camino de señal (2) dentro de un circuito integrado (1) con las siguientes etapas:

(a) Desacoplamiento (S1) de una señal emitida por el camino de señal (2) mediante un multiplexor integrado (7) para la medición de un retraso de señal asimétrico de un camino de medición, que es formado por el camino de señal integrado (2) y por el multiplexor integrado (7); (b) Medición (2) de un retraso de señal asimétrico del multiplexor integrado (7); y (c) Cálculo (S3) de una diferencia entre el retraso de señal asimétrico del camino de medición y el retraso de señal asimétrico del multiplexor integrado (7) para la determinación del retraso de señal asimétrico del camino de señal (2)

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2008/052482.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20 70442 STUTTGART ALEMANIA.

Inventor/es: ROHATSCHEK,ANDREAS-JUERGEN.

Fecha de Publicación: .

Fecha Solicitud PCT: 29 de Febrero de 2008.

Fecha Concesión Europea: 22 de Septiembre de 2010.

Clasificación Internacional de Patentes:

- G01R31/30D

- G01R31/317T

Clasificación PCT:

- G01R31/30 FISICA. › G01 METROLOGIA; ENSAYOS. › G01R MEDIDA DE VARIABLES ELECTRICAS; MEDIDA DE VARIABLES MAGNETICAS (indicación de la sintonización de circuitos resonantes H03J 3/12). › G01R 31/00 Dispositivos para ensayo de propiedades eléctricas; Dispositivos para la localización de fallos eléctricos; Disposiciones para el ensayo eléctrico caracterizadas por lo que se está ensayando, no previstos en otro lugar (ensayo o medida de dispositivos semiconductores o de estado sólido, durante la fabricación H01L 21/66; ensayo de los sistemas de transmisión por líneas H04B 3/46). › Ensayos marginales, p. ej. haciendo variar la tensión de alimentación (ensayo de computadores durante las operaciones de espera "standby" o los tiempos muertos G06F 11/22).

- G01R31/317 G01R 31/00 […] › Ensayo de circuitos digitales.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia.

Fragmento de la descripción:

La presente invención hace referencia a un método para la determinación del retraso de señal asimétrico de un camino de señal dentro de un circuito integrado y, en particular, un método para la determinación del retraso de señal asimétrico de un camino de señal dentro de un módulo de control de comunicación en un bus

10 FlexRay. En un sistema de buses FlexRay se produce la transmisión de datos a través de una multiplicidad de componentes que presentan respectivamente un retraso asimétrico de flancos de señales. En el caso de los componentes, se trata por ejemplo de estrellas activas, transceptores, tampones de entrada y salida.

15 El retraso de señal asimétrico de un componente es la diferencia entre el retraso de recorrido de un flanco de señal ascendente y el retraso de recorrido de un flanco de señal descendente a través del componente. Con ello, las causas de los retrasos asimétricos se subdividen en porciones sistemáticas y no sistemáticas. Las causas sistemáticas para un retraso asimétrico de un componente se predeterminan de forma fija para el componente, dentro de los límites de tolerancia especificados, en un punto de la operación predeterminado, por ejemplo, de una temperatura o una tensión de alimentación determinada. Un retraso de señal asimétrico máximo admisible se establece, en una transmisión de datos, mediante el protocolo de transmisión de datos correspondiente. Un protocolo de transmisión de datos predetermina, por ejemplo, que se detecte n veces una duración nominal de un bit y, en el caso de una indicación de muestreo del contador predeterminada del valor detectado, se adopte para otro procesamiento de datos. El procesamiento de datos se compone, por ejemplo, de la decodificación de un tren de datos en serie. En el protocolo de transmisión de datos del bus FlexRay se detecta, por ejemplo, ocho veces la duración nominal del bit y el valor lógico detectado en una indicación de muestreo del contador es adoptado por cinco. En el protocolo de transmisión de datos

- 2FlexRay, se permite un máximo de 37,5 n seg. de retraso asimétrico en el canal de transmisión para una decodificación sin defectos. Si se excede el retraso asimétrico máximo admisible, se puede detectar un valor incorrecto de bit. El valor incorrecto de bit se reconoce, por ejemplo, mediante un 5 control de redundancia cíclica (CRC) y los datos recibidos se rechazan o se transmiten nuevamente con esfuerzo adicional en el soporte lógico. En el diseño de un sistema de bus, se deben tener en cuenta todos los componentes causantes de una asimetría en la cadena de acción, partiendo de un componente de envío hasta un elemento de recepción. Con este fin, se toma y se 10 suma convencionalmente cada cuota de asimetría de las hojas de datos y de las valoraciones. Sin embargo, en el caso de circuitos integrados no se pueden determinar los retrasos asimétricos provocados por un camino de señal integrado, puesto que no se puede tomar ninguna señal de medición en un punto de medición. Un empaquetador 15 y desempaquetador de datos de señal de prueba adicional para tomar una señal de medición de esta clase, representa un esfuerzo técnico adicional no justificable. Por otra parte, los empaquetadores y desempaquetadores de datos de señal provistos en la carcasa del circuito integrado ya se encuentran reservados en la mayoría de los casos. La patente US 2005/028050 (Olivier Ganry, 03/02/2005) describe un método 20 para la determinación del retraso de señal de un flanco de señal ascendente o descendente de un camino de señal en un circuito integrado. Por lo tanto, es objeto de la presente invención crear un método para la determinación de retrasos de señal asimétricos de un camino de señal dentro de un circuito integrado, con el que se pueda determinar el retraso de señal asimétrico sin 25 proveer de un empaquetador y desempaquetador de datos de señal adicional. Dicho objeto se resuelve, conforme a la presente invención, mediante un método con las características indicadas en la reivindicación 1. La presente invención crea un método para la determinación de un retraso de señal asimétrico y/o de una inestabilidad de un camino de señal dentro de un circuito 30 integrado, con las siguientes etapas:

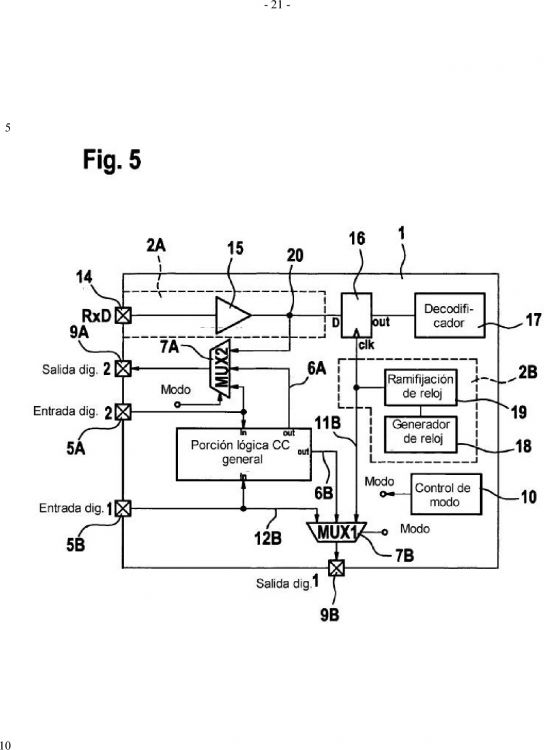

- 3-Desacoplamiento de una señal emitida por el camino de señal mediante un multiplexor integrado para la medición de un retraso de señal asimétrico de un camino de medición, que es formado por el camino de señal integrado y por el multiplexor integrado; 5 -Medición del retraso de señal asimétrico del multiplexor integrado; y -Cálculo de una diferencia entre el retraso de señal asimétrico del camino de medición y el retraso de señal asimétrico del multiplexor integrado para la determinación del retraso de señal asimétrico del camino de señal. En una forma de ejecución del método conforme a la presente invención, un 10 aparato de medición externo para la medición del retraso de señal asimétrico, en primer lugar, aplica un flanco de señal ascendente y, a continuación, un flanco de señal descendente, con que el aparato de comprobación externo registra el tiempo de recorrido para el flanco de señal ascendente y el tiempo de recorrido para el flanco de señal descendente, con que se calcula el retraso de señal asimétrico como diferencia 15 del tiempo de recorrido para el flanco de señal ascendente y del tiempo de recorrido para el flanco de señal descendente. En una forma de ejecución del método conforme a la presente invención, el multiplexor se conmuta entre un primer modo de operación de medición para la medición del retraso de señal del camino de medición y un segundo modo de 20 operación de medición para la medición del retraso de señal del multiplexor. En una forma de ejecución del método conforme a la presente invención, el multiplexor interconecta, en un modo de operación normal, una señal de salida emitida por un circuito lógico integrado. En una forma de ejecución del método conforme a la presente invención, el 25 camino de señal integrado se forma mediante un camino de señal de datos, que en el modo de operación normal emite una señal a un multivibrador biestable integrado de disparo por flanco. En una forma de ejecución del método conforme a la presente invención, el camino de señal integrado se forma mediante un camino de señal de reloj, que en el 30 modo de operación normal emite una señal de reloj a una entrada de señal de reloj de un multivibrador biestable integrado de disparo por flanco.

- 4En una forma de ejecución del método conforme a la presente invención, una unidad de control del modo de operación conmuta el multiplexor entre el primer modo de operación de medición, el segundo modo de operación de medición y el modo de operación normal. 5 En una forma de ejecución del método conforme a la presente invención, el multivibrador biestable de disparo por flanco se conforma de un multivibrador biestable D, que emite una señal de salida lógica a un decodificador integrado del circuito integrado. La presente invención crea, además, un circuito integrado que presenta, al 10 menos, un camino de señal integrado con retraso de señal asimétrico medible, con que en un primer modo de operación de medición se puede desacoplar una señal de salida del camino de señal integrado mediante un multiplexor integrado controlable para la medición de un retraso de señal asimétrico de un camino de medición que abarca el camino de señal integrado y el multiplexor integrado, con que en un 15 segundo modo de operación de medición se puede desacoplar una señal de medición mediante el multiplexor integrado controlable para la medición del retraso de señal asimétrico del multiplexor integrado. En una forma de ejecución preferida del circuito integrado, el camino de señal presenta, al menos, un circuito de memoria intermedia para una señal de datos de 20 recepción. En una forma de ejecución preferida del circuito integrado, el camino de señal se encuentra conectado, del lado de la salida, a una entrada de datos de un multivibrador biestable de disparo por flanco, cuya salida se encuentra conectada a un decodificador integrado del circuito integrado. 25 En una forma de ejecución preferida del circuito integrado, el camino de señal se conforma mediante un camino integrado de señal de reloj. En una forma de ejecución preferida del circuito integrado, el camino de señal de reloj presenta un generador de reloj integrado para la producción de una señal de reloj. 30 En una forma de ejecución preferida del circuito integrado, el generador de señales de reloj es un circuito PLL.

- 5En una forma de ejecución preferida del circuito integrado, el multiplexor...

Reivindicaciones:

1. Método para la determinación de un retraso de señal asimétrico de un camino de señal (2) dentro de un circuito integrado (1) con las siguientes etapas:

(a) Desacoplamiento (S1) de una señal emitida por el camino de señal (2) mediante un multiplexor integrado (7) para la medición de un retraso de señal asimétrico de un camino de medición, que es formado por el camino de señal integrado (2) y por el multiplexor integrado (7);

(b) Medición (2) de un retraso de señal asimétrico del multiplexor integrado (7); y

(c) Cálculo (S3) de una diferencia entre el retraso de señal asimétrico del camino de medición y el retraso de señal asimétrico del multiplexor integrado (7) para la determinación del retraso de señal asimétrico del camino de señal (2).

2. Método de acuerdo con la reivindicación 1, con que un aparato de comprobación externo (13) para la medición del retraso de señal asimétrico, en primer lugar, aplica un flanco de señal ascendente y, a continuación, un flanco de señal descendente, con que el aparato de comprobación externo (13) registra el tiempo de recorrido para el flanco de señal ascendente y el tiempo de recorrido para el flanco de señal descendente, y calcula el retraso de señal asimétrico como diferencia entre el tiempo de recorrido para el flanco de señal ascendente y el tiempo de recorrido para el flanco de señal descendente.

3. Método de acuerdo con la reivindicación 1, con que el multiplexor integrado (7) se puede conmutar entre un primer modo de operación de medición (MBI) para medir el retraso de señal del camino de medición y un segundo modo de operación de medición (MBII) para medir el retraso de señal del multiplexor (7).

4. Método de acuerdo con la reivindicación 3, con que el multiplexor integrado (7), en un modo de operación normal (NB), interconecta una señal de salida lógica producida por un circuito lógico integrado (3).

5. Método de acuerdo con la reivindicación 4, con que el camino de señal (2) se forma mediante un camino de señal de datos (2A), que en el modo de operación normal (NB) emite una señal a un multivibrador biestable integrado (16) de disparo por flanco.

6. Método de acuerdo con la reivindicación 4, con que el camino de señal (2) se forma mediante un camino de señal de reloj (2B), que en el modo de operación

normal (NB) emite una señal de reloj a una entrada de reloj del multivibrador

biestable integrado (16) de disparo por flanco.

7. Método de acuerdo con la reivindicación 3 ó 4, con que una unidad de control del modo de operación (10) conmuta el multiplexor (7) entre el primer modo de operación de medición (MBI), el segundo modo de operación de medición (MBII) y el modo de operación normal (NB).

8. Método de acuerdo con la reivindicación 6, con que el multivibrador biestable (16) de disparo por flanco se conforma de un multivibrador biestable D, que emite una señal de salida lógica a un decodificador integrado (17) del circuito integrado (1).

9. Dispositivo que presenta, al menos, un camino de señal integrado 2 con retraso de señal asimétrico medible, con que en un primer modo de operación de medición (MBI) se puede desacoplar una señal de salida del camino de señal integrado (2) mediante un multiplexor integrado controlable (7) para la medición de un retraso de señal asimétrico de un camino de medición que abarca el camino de señal integrado (2) y el multiplexor integrado (7), con que en un segundo modo de operación de medición (MBII) se puede desacoplar una señal de medición mediante el multiplexor integrado controlable (7) para la medición del retraso de señal asimétrico del multiplexor integrado (7).

10. Dispositivo de acuerdo con la reivindicación 9, con que el camino de señal (2) presenta, al menos, un circuito de memoria intermedia (15) para una señal de datos de recepción.

11. Dispositivo de acuerdo con la reivindicación 10, con que el camino de señal (2) se encuentra conectado, del lado de la salida, a una entrada de datos de un multivibrador biestable de disparo por flanco (16), cuya salida se encuentra conectada a un decodificador integrado (17).

12. Dispositivo de acuerdo con la reivindicación 9, con que el camino de señal (2) se forma mediante un camino integrado de señal de reloj (2B).

13. Dispositivo de acuerdo con la reivindicación 12, con que el camino de señal de reloj presenta un generador de reloj integrado para la producción de una señal de reloj.

14. Dispositivo de acuerdo con la reivindicación 13, con que el generador de señales de reloj (18) es un circuito PLL.

15. Dispositivo de acuerdo con la reivindicación 9, con que el multiplexor integrado (7) presenta, al menos, tres entradas, una salida y una entrada de control.

5 16. Dispositivo de acuerdo con la reivindicación 15, con que el multiplexor

(7) interconecta con un empaquetador y desempaquetador de datos de señal de salida

(5) del dispositivo (1), en el primer modo de operación de medición (MBI), una salida del camino de señal integrado (2) conectada con una primera entrada del multiplexor (7), en el segundo modo de operación de medición (MBII), una señal de

10 medición aplicada a una segunda entrada del multiplexor (7), y en un modo de operación normal (NB), una señal de salida lógica de un circuito lógico integrado (3), aplicada a una tercera entrada del multiplexor (7).

17. Dispositivo de acuerdo con la reivindicación 15, con que la entrada de

control del multiplexor integrado (7) se encuentra conectada con una unidad de 15 control del modo de operación integrada (10).

18. Dispositivo de acuerdo con la reivindicación 9, con que el dispositivo (1) es un controlador de comunicación para un bus FlexRay.

“Siguen 7 páginas de dibujos”

Patentes similares o relacionadas:

Circuito integrado digital protegido contra errores transitorios, del 9 de Octubre de 2019, de THALES: Circuito integrado digital que comprende un conjunto lógico que comprende un bloque lógico funcional, una unidad lógica de detección […]

Procedimiento de prueba de circuitos de criptografía, circuito de criptografía asegurado adecuado para ser probado y procedimiento de cableado de tal circuito, del 27 de Marzo de 2019, de Institut Mines-Telecom: Procedimiento de prueba de un circuito de criptografía que integra un secreto y que consta de registros y de puertas (10, 211, 212, […]

Dispositivo de medición de posición y método para verificar una señal de ciclo de trabajo, del 13 de Febrero de 2019, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo de medición de posición que comprende una unidad de detección de posición , una unidad de procesamiento , una unidad de interfaz […]

Medición eficiente del ruido de la fuente de alimentación basada en la incertidumbre de temporización, del 16 de Enero de 2019, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un circuito integrado que comprende un dispositivo de medición de ruido de la fuente de alimentación, el circuito integrado que tiene un bloque funcional, comprendiendo […]

Método de protección para información de datos relativos a un dispositivo electrónico y su circuito de protección, del 25 de Abril de 2018, de Shenzhen Xinguodu Technology Co. Ltd: Un circuito para proteger información de datos de un equipo electrónico, que comprende un procesador y un dispositivo electrónico conectado con el procesador […]

Procedimiento para la prueba funcional de una unidad receptora PS15 de un aparato de mando de automóvil y unidad receptora PS15 correspondiente, del 26 de Octubre de 2016, de CONTINENTAL AUTOMOTIVE GMBH: Procedimiento para la verificación funcional de una unidad receptora PSI5 de un aparato de mando de automóvil, en donde la unidad receptora […]

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

Procedimiento, componente electrónico y sistema para diagnosticar enlaces de comunicación, del 6 de Enero de 2016, de PHOENIX CONTACT GMBH & CO. KG: Procedimiento para diagnosticar enlaces de comunicación en un sistema de comunicación , que incluye las etapas

a) aportación de una pluralidad de unidades […]

Procedimiento, componente electrónico y sistema para diagnosticar enlaces de comunicación, del 6 de Enero de 2016, de PHOENIX CONTACT GMBH & CO. KG: Procedimiento para diagnosticar enlaces de comunicación en un sistema de comunicación , que incluye las etapas

a) aportación de una pluralidad de unidades […]