Memoria que usa un bus de nodo único de datos, direcciones y control.

Un sistema digital, que comprende

una memoria (104) que usa un bus de nodo único,

de datos, direcciones y control, que comprende:

una matriz de memoria (104) adaptada para su acoplamiento a la alimentación eléctrica (VDD) y

a puesta a tierra (VSS) ;

en donde, la matriz de memoria (104) está encapsulada en un encapsulado de circuito integrado de baja cuenta de terminales (SO 2. 3, SO 2. 5) ; y

un bus de nodo único de datos, direcciones y control (106) acoplado a dicha matriz de memoria (104) , en el que la matriz de memoria (104) tiene un controlador de bus activo de conducción hacia arriba y conducción hacia abajo para controlar el bus de nodo único de datos, direcciones y control (106) y en el que la red de memoria sincroniza una señal de reloj interna de la memoria por medio de una señal recibida; y

un procesador digital (102) acoplado a la memoria (104) a través del bus de nodo único de datos, direcciones y control (106) en el que el procesador digital (102) genera una primera señal de confirmación (ACK) sobre dicho bus de nodo único de datos, direcciones y control después de la recepción de un byte de datos y genera una segunda señal de confirmación (NACK) a la recepción de un byte de datos si no se va a enviar ningún byte de datos adicional por la matriz de memoria (104) .

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2006/047489.

Solicitante: MICROCHIP TECHNOLOGY INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 2355 WEST CHANDLER BOULEVARD CHANDLER, AZ 85224-6199 ESTADOS UNIDOS DE AMERICA.

Inventor/es: SORRELLS,PETER H, WILKIE,DAVID L, PARRIS,CHRISTOPHER A, KVASNICKA,MARTIN S, BOWMAN,MARTIN R.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C5/06 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 5/00 Detalles de memorias cubiertos por el grupo G11C 11/00. › Disposiciones para interconectar eléctricamente elementos de almacenamiento, p. ej. por cableado.

PDF original: ES-2462368_T3.pdf

Fragmento de la descripción:

Memoria que usa un bus de nodo único de datos, direcciones y control

Campo técnico

La presente revelación se refiere, en general, a una memoria de semiconductores, por ejemplo una memoria de solo lectura programable y borrable eléctricamente (EEPROM) , una memoria FLASH, una memoria de acceso aleatorio estática (SRAM) , una memoria de acceso aleatorio dinámica (DRAM) y similares, y más particularmente, a una memoria de semiconductores que usa un bus de nodo único de datos, direcciones y control.

Antecedentes Los dispositivos digitales de circuitos integrados, por ejemplo los procesadores digitales, tales como, por ejemplo, pero sin limitarnos a estos, microprocesadores, microcontroladores, procesadores de señal digital (DSP) , redes lógicas programables (PLA) , circuitos integrados de aplicación específica (ASIC) y similares, se hacen cada vez más pequeños y con menos conexiones de señales de entrada -salida (E/S) (por ejemplo, terminales) tanto por consideraciones de coste como de espacio. Usualmente, un dispositivo de circuito integrado puede estar en un encapsulado de circuito integrado que tiene una pluralidad de terminales de conexión. Al menos dos de estos terminales se deben usar para alimentación eléctrica y puesta a tierra, por ejemplo, VDD y VSS, respectivamente. Estos dispositivos de circuitos integrados se pueden beneficiar de memoria adicional, por ejemplo memoria externa. La memoria puede ser, por ejemplo, pero sin limitarse a estas, una memoria programable una vez (OTP) , una memoria de solo lectura programable eléctricamente (EPROM) , una memoria de solo lectura programable y borrable eléctricamente (EEPROM) , una memoria FLASH, una memoria estática de acceso aleatorio (SRAM) , una memoria dinámica de acceso aleatorio (DRAM) y similares.

El documento US 5.270.972 desvela un sistema digital serie de tres terminales en el que está dispuesto una memoria en un encapsulado de baja cuenta de terminales y conectado a un bus de nodo único (303, fig. 3) controlado por un controlador de conducción hacia abajo (385) . El controlador de conducción hacia abajo genera una primera o una segunda señales de confirmación sobre un bus de nodo único (303) causadas por una señal de control (ACK) recibida desde un procesador digital (340) .

El documento EP 1 496 444 desvela un procedimiento de generación de una señal de activación de un núcleo de memoria normalizado. El documento US 6.034.898 desvela una memoria dinámica de acceso aleatorio para aumentar la corriente del controlador de salida de datos que comparte transistores de conducción hacia arriba y transistores de conducción hacia abajo. El documento US 2005/0268022 desvela una memoria de línea caché y un procedimiento que tiene un puerto de direcciones serie. El documento US 5.809.518 desvela un protocolo de transferencia de comandos / datos para una arquitectura de bus de un hilo.

Sumario Es un objeto de la presente invención proporcionar un sistema digital que tiene una memoria conectada a un bus de un nodo único que proporciona un protocolo de transmisión fiable. Este objeto se puede conseguir por el sistema digital como se define en la reivindicación independiente 1. Las mejoras adicionales se caracterizan en las reivindicaciones dependientes.

Por ejemplo, una matriz de memoria (en adelante en ese documento "memoria") puede estar acoplada a un dispositivo digital de circuito integrado con un número mínimo de conexiones, por ejemplo, se pueden requerir un bus de nodo único de datos, direcciones y control, más alimentación eléctrica y puesta a tierra, por ejemplo, VDD (o VCC) y VSS, respectivamente, para la operación de la memoria, de este modo se puede usar un encapsulado mínimo de circuito integrado de tres terminales, por ejemplo, SOT 23-3, SC70-3, etc. para el encapsulado de la memoria. La selección de direcciones de la memoria cuando se implementa una pluralidad de memorias puede usar terminales de selección de dirección adicionales sobre un encapsulado de circuito integrado de baja cuenta de terminales, por ejemplo, SOT 23-5, SOT 23-6, MSOP-8, SOIC-8 y similares, y/o programando una dirección de memoria para cada una de la pluralidad de memorias a través del bus de nodo único de datos, direcciones y control.

De acuerdo con una realización de ejemplo específica como se describe en la presente revelación, una memoria que usa un bus de nodo único de datos, direcciones y control, comprende una matriz de memoria adaptada para el acoplamiento a un bus de nodo único de datos, direcciones y control, alimentación eléctrica y puesta a tierra. La matriz de memoria tiene un controlador activo de conducción hacia arriba y conducción hacia abajo para controlar el bus de nodo único de datos, direcciones y control. La matriz de memoria puede estar encapsulada en un encapsulado de circuito integrado con una baja cuenta de terminales. La memoria puede ser también parte de un encapsulado de circuito integrado de múltiples dados que albergan tanto el dispositivo digital como la memoria.

De acuerdo con otra realización de ejemplo específica como se describe en la presente revelación, un sistema digital comprende un procesador digital y una matriz de memoria que se acopla al procesador digital a través de un bus de nodo único de datos, direcciones y control. La matriz de memoria tiene un controlador activo de bus con conducción hacia arriba y hacia abajo para controlar el bus de nodo único de datos, direcciones y control. El procesador digital

puede ser el maestro y la matriz de memoria puede ser un esclavo sobre el bus de nodo único de datos, direcciones y control.

Breve descripción de los dibujos Se puede adquirir un entendimiento más completo de la presente revelación refiriéndonos a la siguiente descripción tomada junto con los dibujos adjuntos, en los que:

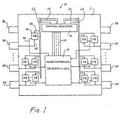

la Figura 1 ilustra un diagrama de bloques esquemático de un dispositivo digital de circuito integrado acoplado a una memoria con un bus de nodo único de datos, direcciones y control, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 2 ilustra diagramas físicos esquemáticos de encapsulados de circuitos integrados de baja cuenta de terminales de ejemplo, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 3 ilustra un diagrama esquemático de formas de onda de temporización de señal para un bus de nodo único de datos, direcciones y control ilustrado en la Figura 1, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 4 ilustra un diagrama de una asignación de bytes de dirección de un dispositivo de memoria en una memoria, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 5 ilustra una tabla de un conjunto de instrucciones para una memoria, de acuerdo con una realización de ejemplo específica de la presente revelación:

la Figura 6 ilustra un diagrama esquemático de formas de onda de temporización de señal para una secuencia de comando de lectura de una memoria, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 7 ilustra un diagrama esquemático de formas de onda de temporización de señal para una secuencia de comando de escritura de una memoria, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 8 ilustra un diagrama esquemático de formas de onda de temporización de señal para una secuencia de comando de activación de escritura de una memoria, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 9 ilustra un diagrama esquemático de formas de onda de temporización de señal para una secuencia de comando de desactivación de escritura de una memoria, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 10 ilustra un diagrama esquemático de formas de onda de temporización de señal para una secuencia de comando de lectura del registro de estado de una memoria, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 11 ilustra un diagrama esquemático de formas de onda de temporización de señal para una secuencia de comando de escritura del registro de estado de una memoria, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 12 ilustra un diagrama esquemático de formas de onda de temporización de señal para una secuencia de comando de borrar todo de una memoria, de acuerdo con una realización de ejemplo específica de la presente revelación;

la Figura 13 ilustra un diagrama esquemático de formas de onda de... [Seguir leyendo]

Reivindicaciones:

1. Un sistema digital, que comprende una memoria (104) que usa un bus de nodo único, de datos, direcciones y control, que comprende:

una matriz de memoria (104) adaptada para su acoplamiento a la alimentación eléctrica (VDD) y a puesta a tierra (VSS) ; en donde, la matriz de memoria (104) está encapsulada en un encapsulado de circuito integrado de baja cuenta de terminales (SO.

2. 3, SO.

2. 5) ; y un bus de nodo único de datos, direcciones y control (106) acoplado a dicha matriz de memoria (104) , en el que la matriz de memoria (104) tiene un controlador de bus activo de conducción hacia arriba y conducción hacia abajo para controlar el bus de nodo único de datos, direcciones y control (106) y en el que la red de memoria sincroniza una señal de reloj interna de la memoria por medio de una señal recibida; y

un procesador digital (102) acoplado a la memoria (104) a través del bus de nodo único de datos, direcciones y control (106) en el que el procesador digital (102) genera una primera señal de confirmación (ACK) sobre dicho bus de nodo único de datos, direcciones y control después de la recepción de un byte de datos y genera una segunda señal de confirmación (NACK) a la recepción de un byte de datos si no se va a enviar ningún byte de datos adicional por la matriz de memoria (104) .

2. El sistema digital de acuerdo con la reivindicación 1, en el que la señal recibida comprende una cabecera de comienzo codificada en binario multi-bit.

3. El sistema digital de acuerdo con la reivindicación 1 o 2, en el que la matriz de memoria (104) genera una señal de confirmación (ACK) después de la recepción de un byte por dicho controlador de bus de conducción hacia arriba y conducción hacia abajo.

4. El sistema digital de acuerdo con una de las reivindicaciones anteriores, que comprende además al menos un terminal de selección de la dirección de memoria (A0; A1) .

5. El sistema digital de acuerdo con una de las reivindicaciones anteriores, en el que la matriz de memoria (104) usa un protocolo de transferencia en serie de señales seleccionado del grupo que consiste en Manchester, modulación de ancho de pulso (PWM) , modulación sin retorno a cero (NRZ) , modulación de la posición de pulso (PPM) , codificación de desplazamiento de frecuencia (FSK) , codificación de desplazamiento de fase (PSK) , y codificación de desplazamiento de amplitud (ASK) .

6. El sistema digital de acuerdo con una de las reivindicaciones anteriores, en el que la matriz de memoria (104) tiene una instrucción READ que lee los datos de la matriz de memoria (104) comenzando en una dirección seleccionada y una instrucción WRITE que escribe los datos a la matriz de memoria (104) comenzando en la dirección seleccionada.

7. El sistema digital de acuerdo con una de las reivindicaciones anteriores, en el que la matriz de memoria (104) tiene una instrucción WREN que establece un seguro de activación de la escritura de modo que posibilita las operaciones de escritura y una instrucción WRDI que elimina el seguro de activación de la escritura de modo que imposibilita las operaciones de escritura.

8. El sistema digital de acuerdo con la reivindicación 1, en el que la matriz de memoria (104) tiene una instrucción RDSR que lee desde una pluralidad de registros de estado y una instrucción WRSR que escribe a uno o a la pluralidad de registros de estado.

9. El sistema digital de acuerdo con la reivindicación 1, en el que la matriz de memoria (104) tiene una instrucción ERAL que borra toda la matriz de memoria (104) y una instrucción WRAL que escribe toda la matriz de memoria (104) .

10. El sistema digital de acuerdo con una de las reivindicaciones anteriores, en el que la matriz de memoria (104) se selecciona del grupo que consiste en una memoria programable una vez (OTP) , una memoria de solo lectura programable eléctricamente (EPROM) , una memoria de solo lectura programable y borrable eléctricamente (EEPROM) , y una memoria FLASH.

11. El sistema digital de acuerdo con una de las reivindicaciones anteriores, en el que el encapsulado de circuito integrado (SO.

2. 3) tiene tres terminales (VSS, VDD, SCIO) .

12. El sistema digital de acuerdo con una de las reivindicaciones anteriores, que comprende además un encapsulado de circuito integrado (SO.

2. 3; SO.

2. 5) que encapsula el procesador digital (102) y la matriz de memoria (104) .

13. El sistema digital de acuerdo con la reivindicación 12, en el que el encapsulado del circuito integrado SO.

2. 3;

SO.

2. 5) es un encapsulado de dados dual.

14. El sistema digital de acuerdo con una de las reivindicaciones anteriore.

11. 13, en el que el procesador digital

(102) se selecciona del grupo que consiste en un microprocesador, un microcontrolador y procesador de señales digitales (DSP) , una matriz lógica programable (PLA) , y un circuito integrado de aplicación específica (ASIC) .

15. El sistema digital de acuerdo con una de las reivindicaciones anteriores 11-14, en el que el procesador digital

(102) es un maestro y la matriz de memoria (104) es un esclavo sobre el bus de nodo único de datos, direcciones y control (106) .

Patentes similares o relacionadas:

Dispositivo y procedimiento para el procesamiento de cuadros de datos en serie, del 11 de Octubre de 2018, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo para el procesamiento de cuadros de datos en serie, que comprende una unidad de convertidor en serie-paralelo , una unidad de evaluación […]

Circuito de terminación para terminación en troquel, del 6 de Noviembre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un circuito de terminación para proporcionar terminación en troquel para un terminal de undispositivo semiconductor , en […]

Almacenamiento de datos y estructuras apilables, del 18 de Septiembre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un sistema que comprende una pila incluyendo: un primer dispositivo de memoria ; un segundo dispositivo de memoria […]

Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N, del 21 de Agosto de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador,que comprende:

dotar a un chip […]

Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N, del 21 de Agosto de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador,que comprende:

dotar a un chip […]

Dispositivo en cascada de cadena de margarita, del 4 de Junio de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un dispositivo semiconductor (410a, ..., 410d) que comprende: memoria; circuitos de entrada de reloj configurados para recibir una señal de reloj (SCLK); circuitos de […]

Dispositivo de Cascada de Cadena Tipo Margarita, del 12 de Septiembre de 2012, de MOSAID TECHNOLOGIES INCORPORATED: Un sistema que tiene una pluralidad de dispositivos conectados en serie que incluyen por lo menosprimeros y segundos dispositivos, caracterizado porque: el […]

SISTEMA DE MEDICION EN RED CON SENSORES Y UN PUENTE., del 16 de Marzo de 2007, de VLAAMSE INSTELLING VOOR TECHNOLOGISCH ONDERZOEK (VITO): Sistema de medición configurado para la medición de los valores físicos en una red de sensores de tipo bus, comprendiendo dicha red de sensores de tipo bus por […]

CONJUNTO DE MODULO DE MEMORIA QUE UTILIZA CHIPS PARCIALMENTE DEFECTUOSOS, del 1 de Noviembre de 2007, de CELETRONIX INTERNATIONAL, LTD

CELETRONIX USA, INC.: Procedimiento para la implementación selectiva de un reforzador de reloj, comprendiendo dicho procedimiento: montar un reforzador de reloj en una placa […]

CONJUNTO DE MODULO DE MEMORIA QUE UTILIZA CHIPS PARCIALMENTE DEFECTUOSOS, del 1 de Noviembre de 2007, de CELETRONIX INTERNATIONAL, LTD

CELETRONIX USA, INC.: Procedimiento para la implementación selectiva de un reforzador de reloj, comprendiendo dicho procedimiento: montar un reforzador de reloj en una placa […]