DISPOSITIVO Y PROCEDIMIENTO PARA CONTROLAR INVERSORES CONECTADOS EN SERIE.

Dispositivo (30) para controlar dos o más inversores (17, 24, 25) conectados en serie, pudiendo recibir cada inversor como entrada una señal de CC y al menos una señal de control para generar una señal de CA como salida, comprendiendo dicho dispositivo (30):

- un primer generador (67) de señales que puede generar una pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3'), estando las señales portadoras de dicha pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3') en una única frecuencia (fc), en fase entre sí, o, en pares, en oposición de fase entre sí, y teniendo diferentes niveles de CC; - un segundo generador (68) de señales que puede generar una señal de referencia (Vref); - medios (31) de control que pueden comparar dicha señal de referencia (Vref) con cada señal portadora de dicha pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3') para generar como salida una pluralidad respectiva de señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3'), caracterizado porque comprende - medios (40) de conmutación que pueden dirigir cada señal de control de dicha pluralidad de señales de control (Vpwm1, Vpwm1' Vpwm2, Vpwm2', Vpwm3, Vpwm3') en secuencia como entrada a cada uno de dichos dos o más inversores (17, 24, 25) de tal manera que, en cualquier instante temporal, a la al menos una entrada de control de cada inversor se le alimenta una única señal de control de dicha pluralidad de señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3')

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E06425361.

Solicitante: ANSALDO SISTEMI INDUSTRIALI S.P.A.

Nacionalidad solicitante: Italia.

Dirección: VIALE SARCA 336 20126 MILANO MI ITALIA.

Inventor/es: Torri,GiordanoAnsaldo Sistemi Industriali S.p.A.

Fecha de Publicación: .

Fecha Solicitud PCT: 26 de Mayo de 2006.

Clasificación Internacional de Patentes:

- H02M7/49 ELECTRICIDAD. › H02 PRODUCCION, CONVERSION O DISTRIBUCION DE LA ENERGIA ELECTRICA. › H02M APARATOS PARA LA TRANSFORMACION DE CORRIENTE ALTERNA EN CORRIENTE ALTERNA, DE CORRIENTE ALTERNA EN CORRIENTE CONTINUA O DE CORRIENTE CONTINUA EN CORRIENTE CONTINUA Y UTILIZADOS CON LAS REDES DE DISTRIBUCION DE ENERGIA O SISTEMAS DE ALIMENTACION SIMILARES; TRANSFORMACION DE UNA POTENCIA DE ENTRADA EN CORRIENTE CONTINUA O ALTERNA EN UNA POTENCIA DE SALIDA DE CHOQUE; SU CONTROL O REGULACION (transformadores H01F; convertidores dinamoeléctricos H02K 47/00; control de los transformadores, reactancias o bobinas de choque, control o regulación de motores, generadores eléctricos o convertidores dinamoeléctricos H02P). › H02M 7/00 Transformación de una potencia de entrada en corriente alterna en una potencia de salida en corriente continua; Transformación de una potencia de entrada en corriente continua en una potencia de salida en corriente alterna. › Combinación de las formas de onda de la tensión de salida de una pluralidad de convertidores.

Clasificación PCT:

- H02M7/48 H02M 7/00 […] › utilizando tubos de descarga con electrodo de control o dispositivos semiconductores con electrodo de control.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

PDF original: ES-2357852_T3.pdf

Fragmento de la descripción:

La presente invención se refiere a un dispositivo para controlar inversores conectados en serie, según el preámbulo de la reivindicación 1.

En particular, la aplicación de la presente invención es en unidades de fuente de alimentación para el control de cargas de CA, tales como, por ejemplo, motores trifásicos.

Se conocen unidades de fuente de alimentación para cargas de CA en el estado de la técnica, y comprenden un transformador con devanados primario y secundario que pueden conectarse a una red de alimentación eléctrica, un rectificador que convierte la tensión de red de CA en una tensión de CC, y un inversor que convierte la tensión de CC rectificada en una tensión de CA a una frecuencia predefinida determinada por un sistema de ancho de modulación de impulsos o PMW, por ejemplo para alimentar esta tensión de CA a un motor de CA, por ejemplo un motor de inducción trifásico.

En la patente US 5,625,545 se describe una unidad de alimentación eléctrica para controlar motores de corriente alterna de tensión media. Según la técnica conocida descrita anteriormente, la unidad de alimentación comprende un transformador multifásico con una pluralidad de devanados secundarios que alimentan potencia a una correspondiente pluralidad de baterías conectadas en serie para cada fase del motor. Cada una de las baterías tiene una salida monofásica y puede controlarse mediante un dispositivo controlador de la modulación. Cada batería tiene un rectificador que rectifica la tensión de CA alimentada por un devanado secundario del transformador, para alimentar una tensión de CC rectificada, un condensador de aplanamiento para eliminar la ondulación presente en la tensión de CC rectificada, y un inversor de PWM que convierte la tensión de CC presente en los extremos del condensador en una tensión de CA. El dispositivo controlador de la modulación actúa sobre cada batería para controlar la salida, de manera que el instante de conmutación de una batería a la línea de fase de carga está separado en el tiempo del instante de conmutación de las demás baterías a la misma línea de fase de carga, por ejemplo para reducir las componentes armónicas en cada línea de fase de alimentación de carga. En particular, el control de la modulación se basa en un procedimiento subarmónico o de suboscilación, de manera que se compara una única señal de referencia con una pluralidad de señales portadoras, una para cada señal de potencia, oscilando a la misma frecuencia y desplazadas en fase de manera adecuada entre sí según el procedimiento definido como “interdigitado”. Normalmente, el desplazamiento de fase es igual a 360° dividido entre el número de baterías en serie en una línea de fase de carga. A partir de la comparación entre la señal de referencia y cada señal portadora, se generan señales de control para los inversores de las baterías, específicamente para controlar el encendido y apagado de los transistores IGBT que constituyen cada inversor.

Un procedimiento alternativo conocido para el control de la modulación de inversores en serie de una unidad de fuente de alimentación de CA implica el uso de una pluralidad de señales portadoras que oscilan a la misma frecuencia, que están en fase entre sí y que están desplazadas en nivel, es decir que tienen diferentes niveles de polarización de CC por ejemplo para ocupar bandas de amplitud adyacentes.

Según este procedimiento alternativo, las señales portadoras positivas puede estar en oposición de fase con las señales portadoras negativas, así como las señales portadoras pueden alternar dispuestas en fase – en oposición de fase (A new multilevel PWM method: a theoretical analysis. Carrara, Marchesoni et al. IEEE Transaction in Power Electronics, Vol. 7, n. 3 julio de 1992).

Se ilustra un dispositivo para el control de inversores en serie que utiliza el procedimiento de control según la técnica conocida descrita anteriormente con referencia a las figuras 1 a 13 en el caso de tres baterías conectadas en serie.

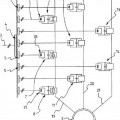

El dispositivo 100 de control está diseñado para controlar tres inversores 101, 102 y 103 conectados en serie para alimentar un motor trifásico. Para mayor simplicidad de la descripción, los inversores que se utilizan para alimentar las otras dos fases del motor trifásico se han omitido, al igual que la sección de rectificación de cada batería.

Cada inversor, por ejemplo el inversor 101 mostrado en la figura 2, consiste en una estructura de puente en H con dos ramas de transistor IGBT, en particular una rama izquierda en la que están dispuestos dos transistores 110a, 110b IGBT en serie entre sí, y una rama derecha en la que están dispuestos dos transistores 111a, 111b IGBT en serie entre sí. El inversor 101 comprende adicionalmente dos bancos de condensadores 112 y 113 de aplanamiento que están conectados en paralelo a los pares de transistores 110a, 110b, 111a, 111b IGBT.

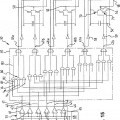

El dispositivo 100 de control comprende seis comparadores 104a, 104b, 105a, 105b, 106a, 106b, cada uno de los cuales compara una señal de referencia o señal 116 de modulación con una señal 107a, 107b, 108a, 108b, 109a, 109b portadora respectiva (figura 3) para generar seis señales 120a, 120b, 121a, 121b, 122a, 122b de control respectivas (figuras 4 a 9) para los tres inversores 101, 102, 103.

Las señales 107a, 107b, 108a, 108b, 109a, 109b portadoras se generan mediante un generador 114 de señales, mientras que la señal 116 de referencia se genera mediante un generador 117 de señales.

En las figuras adjuntas, las señales se indican con referencia a las líneas sobre las que se transmiten esas señales.

Las señales 107a, 107b, 108a, 108b, 109a, 109b portadoras oscilan a la misma frecuencia, están en fase entre sí, y sus niveles de CC están desplazados. Las señales 107a, 107b, 108a, 108b, 109a, 109b portadoras mostradas en la figura 3 se generan en pares que son simétricos con relación a la tensión cero de manera que los pares de señales 107a y 107b, 108a y 108b, 109a y 109b simétricas están en oposición de fase entre sí. Como alternativa, los pares de señales 107a y 107b, 108a y 108b, 109a y 109b puede estar en fase entre sí y desplazados en nivel de CC.

La comparación de los pares de señales 107a y 107b, 108a y 108b, 109a y 109b portadoras con la señal 116 de referencia genera los pares de señales 120a y 120b, 121a y 121b, 122a y 122b de control, que están diseñadas para controlar las ramas derecha e izquierda respectivas de cada inversor (figuras 4 a 9).

Debe señalarse que el dispositivo 100 de control hace posible controlar los inversores 101, 102, 103 de manera que el instante de conmutación de un inversor en una línea de fase está separado en el tiempo del instante de conmutación de los demás inversores en la misma línea de fase, por ejemplo para reducir las componentes armónicas en cada línea de fase de alimentación de carga, como es el caso utilizando el dispositivo de control y el procedimiento subarmónico descrito en la patente US 5,626,545.

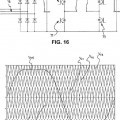

La figura 13 representa la forma de onda de la tensión 130 de alimentación producida por los inversores 101, 102, 103 que están conectados en serie en el caso de uso del dispositivo 100 de control, en la que las señales 120a, 120b, 121a, 121b, 122a, 122b de control se generan mediante la comparación de la señal 116 de referencia con las señales 107a, 107b, 108a, 108b, 109a, 109b portadoras.

Debe señalarse que la forma de onda de la tensión 130 producida por los inversores 101, 102, 103 en el caso de uso del dispositivo 100 de control corresponde sustancialmente a la que se produciría por los inversores 101, 102, 103 en el caso de uso del dispositivo de control y el procedimiento de modulación subarmónico descrito en la patente US 5,626,545, en que el se utilizan señales portadoras desplazadas en fase entre sí. Sin embargo, si se tiene en cuenta la tensión generada por los inversores 101, 102, 103 individuales, se observa una diferencia sustancial.

Las figuras 10, 11 y 12 representan las tensiones 127, 128, 129 de salida que se generan respectivamente por los inversores 103, 102, 101 utilizando el dispositivo 100 de control. Las tensiones 127, 128, 129 de salida se refieren al caso real en el que los transistores IGBT tienen una función de transferencia cuadrada, sin tener en cuenta los retardos de los transistores en conmutación.

La comparación de las formas de onda de las tensiones 127, 128, 129 de salida generadas por el dispositivo 100 y las generadas por el... [Seguir leyendo]

Reivindicaciones:

1. Dispositivo (30) para controlar dos o más inversores (17, 24, 25) conectados en serie, pudiendo recibir cada inversor como entrada una señal de CC y al menos una señal de control para generar una señal de CA como salida, comprendiendo dicho dispositivo (30):

- un primer generador (67) de señales que puede generar una pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3'), estando las señales portadoras de dicha pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3') en una única frecuencia (fc), en fase entre sí, o, en pares, en oposición de fase entre sí, y teniendo diferentes niveles de CC;

- un segundo generador (68) de señales que puede generar una señal de referencia (Vref);

- medios (31) de control que pueden comparar dicha señal de referencia (Vref) con cada señal portadora de dicha pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3') para generar como salida una pluralidad respectiva de señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3'), caracterizado porque comprende

- medios (40) de conmutación que pueden dirigir cada señal de control de dicha pluralidad de señales de control (Vpwm1, Vpwm1' Vpwm2, Vpwm2', Vpwm3, Vpwm3') en secuencia como entrada a cada uno de dichos dos o más inversores (17, 24, 25) de tal manera que, en cualquier instante temporal, a la al menos una entrada de control de cada inversor se le alimenta una única señal de control de dicha pluralidad de señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3').

2. Dispositivo (30) según la reivindicación 1, en el que dichos medios (40) de conmutación pueden dirigir, con un periodo Ts, dichas señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3') como entrada a dichos dos o más inversores (17, 24, 25), consistiendo dicho periodo Ts en un número de subperiodos ti igual al número de inversores conectados en serie, en el que:

- en cada subperiodo ti:

- a cada entrada de control se le alimenta una única señal de control y cada señal de control alimenta una única entrada de control; y

- cada señal de control alimenta un inversor que es diferente del inversor alimentado en el subperiodo anterior;

- en cada periodo Ts:

- cada señal de control alimenta cada inversor durante uno sólo de dichos subperiodos ti.

3. Dispositivo (30) según la reivindicación 2, en el que dichos subperiodos ti tienen la misma duración t.

4. Dispositivo (30) según la reivindicación 2 o la reivindicación 3, en el que dichos subperiodos ti tienen una duración t que es mayor que, o igual al periodo Tc de dichas señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3').

5. Dispositivo (30) según una cualquiera de las reivindicaciones 1 a 4, en el que dichos medios (31) de control comprenden una pluralidad de comparadores (61, 62, 63, 64, 65, 66), pudiendo comparar cada comparador de dicha pluralidad de comparadores (61, 62, 63, 64, 65, 66) dicha señal de referencia (Vref) con una señal portadora respectiva de dicha pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3') para generar como salida una señal de control respectiva, pudiendo dirigir dichos medios (31) de conmutación la señal de control generada por cada comparador en secuencia como entrada a cada uno de los inversores (17, 24, 25) de tal manera que, en cualquier instante temporal, a la al menos una entrada de control de cada inversor se le alimenta una única señal de control de dicha pluralidad de señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3').

6. Dispositivo (30) según una cualquiera de las reivindicaciones 1 a 5, en el que cada inversor comprende una primera entrada (47a) de control para recibir una primera señal de control, una segunda entrada (47b) de control para recibir una segunda señal de control, pudiendo controlarse los medios de conmutación primeros (72, 73) y segundos (70, 71) respectivamente mediante dichas señales de control primera y segunda, pudiendo comparar dichos medios (31) de control dicha señal de referencia (Vref) con una primera señal portadora (Vc1, Vc2, Vc3) y con una segunda señal portadora (Vc1', Vc2', Vc3') de dicha pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3') para generar respectivamente dichas señales de control primera y segunda, pudiendo dirigir dichos medios (40) de conmutación dicha primera señal de control en secuencia a la primera entrada (47a, 48a, 49a) de control de cada inversor, y dicha segunda señal de control en secuencia a la segunda entrada (47b, 48b, 49b) de control de cada inversor de tal manera que, en cualquier instante temporal, a la primera entrada de control de cada inversor se le alimenta una única primera señal de control de dicha pluralidad de señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3') y a la segunda entrada de control de cada inversor se le alimenta una única segunda señal de control de dicha pluralidad de señales de control (Vpwm1,

Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3').

7. Dispositivo (30) según la reivindicación 6, en el que cada inversor comprende una estructura de puente en H con una primera y una segunda rama, estando dispuestos dichos medios de conmutación primeros (72, 73) y segundos (70, 71) respectivamente en dicha primera y segunda rama, siendo simétricas dichas señales portadoras primera (Vc1, Vc2, Vc3) y segunda (Vc1', Vc2', Vc3') con respecto al nivel cero de la señal de referencia (Vref).

8. Dispositivo (30) según una cualquiera de las reivindicaciones 1 a 7, en el que dichos medios (40) de conmutación comprenden una pluralidad de puertas lógicas Y y un generador de señales de conmutación, teniendo cada puerta (80) lógica de dicha pluralidad de puertas lógicas una primera entrada (81) que está conectada a dichos medios (31) de control para recibir una señal de control (Vpmw1), una segunda entrada (82) que está conectada a dicho generador de señales de conmutación para recibir una señal de conmutación (VA) y una salida (83) que puede conectarse a un inversor, estando conectadas las salidas de dichas puertas (80) lógicas entre sí en grupos como entrada en una puerta lógica O de tal manera que cada señal de control (Vpwm1, Vpwm1', Vpwm2', Vpwm2', Vpwm3, Vpwm3') se dirige como entrada en secuencia a cada uno de los inversores dependiendo del valor lógico de las señales de conmutación (VA, VB, VC).

9. Dispositivo (30) según una cualquiera de las reivindicaciones 1 a 8, en el que cada señal de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3') se dirige como entrada en secuencia a cada uno de los inversores de tal manera que los niveles de potencia promedio de la señal de salida de CA generada por cada inversor, cuando se evalúa durante un intervalo de tiempo predefinido, se corresponden sustancialmente entre sí, de modo que la potencia alimentada por los inversores se distribuye uniformemente en los inversores.

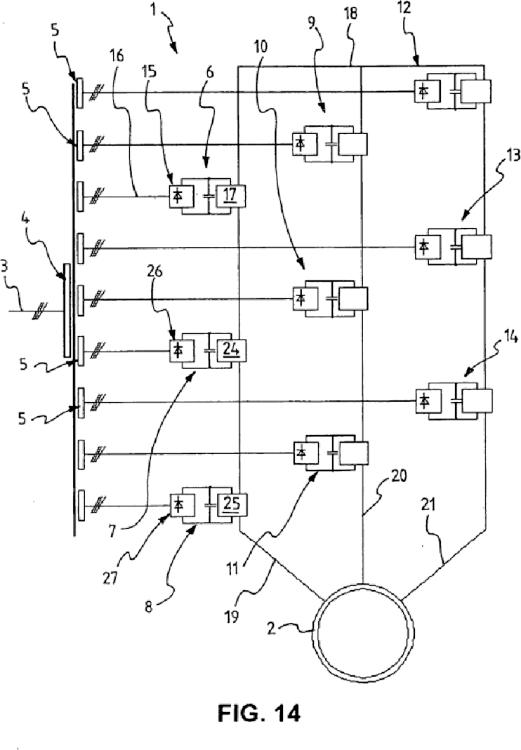

10. Unidad (1) de fuente de alimentación de CA para excitar una carga (2) de CA, que comprende:

- medios de transformador que pueden recibir una señal de CA a una primera frecuencia (f1) y comprenden un circuito (4) de devanado primario y dos o más circuitos (5) de devanado secundario;

- dos o más baterías (6, 7, 8) que están conectadas en serie, comprendiendo cada batería (6):

- un rectificador (15) que tiene una entrada de CA conectada a un circuito (5) de devanado secundario respectivo y una salida de CC;

- un inversor (17) que tienen una entrada de CC conectada a la salida de CC del rectificador para recibir una señal de CC, al menos una entrada de control para recibir una señal de control y una salida de CA para generar una señal de CA a una segunda frecuencia (f2);

estando los inversores (17, 24, 25) de dichas baterías (6, 7, 8) conectados en serie para alimentar dicha carga (2) de CA; y

- un dispositivo (30) para controlar dichos inversores (17, 24, 25) conectados en serie, según una cualquiera de las reivindicaciones 1 a 9.

11. Unidad (1) de fuente de alimentación de CA según la reivindicación 10, en la que dicha carga (2) de CA es una carga que tiene un número N de fases, comprendiendo dicha unidad (1) de alimentación N inversores para cada fase de dicha carga de CA.

12. Procedimiento para controlar dos o más inversores (17, 24, 25) conectados en serie, pudiendo recibir cada inversor como entrada una señal de CC y al menos una señal de control para generar como salida una señal de CA, comprendiendo dicho procedimiento las etapas de:

- comparar una señal de referencia (Vref) con cada señal portadora de una pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2' Vc3, Vc3') para generar como salida una pluralidad respectiva de señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3'), estando las señales portadoras de la pluralidad de señales portadoras (Vc1, Vc1', Vc2, Vc2', Vc3, Vc3') a la misma frecuencia (fc) y en fase entre sí, y teniendo diferentes niveles de CC;

- dirigir cada señal de control de dicha pluralidad de señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3') en secuencia como entrada a cada uno de dichos dos o más inversores (14, 24, 25) de tal manera que, en cualquier instante temporal, a la al menos una entrada de control de cada inversor se le alimenta una única señal de control de dicha pluralidad de señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3, Vpwm3').

13. Procedimiento según la reivindicación 12, en el que dicha etapa de direccionamiento comprende dirigir, con un periodo Ts, dichas señales de control (Vpwm1, Vpwm1', Vpwm2, Vpwm2', Vpwm3,Vpwm3') como entrada a dichos dos o más inversores (17, 24, 25), consistiendo dicho periodo Ts en un número de subperiodos t1 que es igual al número de inversores conectados en serie, en el que:

- en cada subperiodo ti:

- a cada entrada de control se le alimenta una única señal de control, y cada señal de control alimenta una única entrada de control; y

- cada señal de control alimenta un inversor que es diferente del inversor alimentado en el subperiodo anterior;

- en cada periodo Ts:

- cada señal de control alimenta cada inversor durante uno sólo de dichos subperiodos ti.

Patentes similares o relacionadas:

Unidad de acoplamiento y módulo de batería con ondulador pulsado integrado y módulos de celdas intercambiables durante el funcionamiento, del 10 de Junio de 2020, de SAMSUNG SDI CO., LTD.: Unidad de acoplamiento sin abastecimiento de energía propio para un módulo de batería, comprendiendo la unidad de acoplamiento una […]

Procedimiento de control para el uso de redundancia en el caso de una falla de un convertidor de corriente polifásico con acumuladores de energía distribuidos, del 22 de Abril de 2020, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para el control de un convertidor con al menos dos módulos de fase (T1, ..., T6) que presentan un primer y un segundo ramal de válvula […]

Procedimiento de control de redundancia de un convertidor polifásico con acumuladores de energía distribuidos, del 22 de Abril de 2020, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para controlar un convertidor con acumuladores de energia distribuidos con tres modulos de fase , que forman en cada caso […]

UN CONVERTIDOR DE POTENCIA PARCIAL SIN TRANSFORMADOR (PPC) PARA LA ETAPA DC-DC DE ESTACIONES DE CARGA RÁPIDA DE VEHÍCULOS ELÉCTRICOS (EV), del 26 de Marzo de 2020, de UNIVERSIDAD TÉCNICA FEDERICO SANTA MARÍA: Se describe un nuevo convertidor de potencia parcial (PPC) para la etapa DC-DC de estaciones de carga rápida de vehículos eléctricos (EV). El […]

Inversor de múltiples niveles, del 26 de Febrero de 2020, de LSIS Co., Ltd: Un inversor de múltiples niveles, el inversor de múltiples niveles comprende: un transformador de cambio de fase configurado para emitir un voltaje de […]

Inversor con celda de potencia de doble estructura, del 26 de Febrero de 2020, de LSIS Co., Ltd: Un inversor con celda de potencia de doble estructura, el inversor comprende: una pluralidad de celdas de potencia, cada una con una pluralidad de regiones de la celda […]

Dispositivo generador-motor de velocidad variable y sistema generador-motor de velocidad variable, del 4 de Diciembre de 2019, de Hitachi Mitsubishi Hydro Corporation: Un sistema generador-motor de velocidad variable que comprende un convertidor de potencia conectado a una fuente de alimentación de CC , que […]

Inversor de múltiples niveles con módulos separados de celdas de alimentación, del 27 de Noviembre de 2019, de LSIS Co., Ltd: Un inversor de múltiples niveles configurado para emitir un voltaje trifásico a un motor , el inversor de múltiples niveles que […]

Inversor de múltiples niveles con módulos separados de celdas de alimentación, del 27 de Noviembre de 2019, de LSIS Co., Ltd: Un inversor de múltiples niveles configurado para emitir un voltaje trifásico a un motor , el inversor de múltiples niveles que […]