Corrección de errores digitales.

Un circuito corrector de errores, dispuesto para recibir una señal de reloj,

que comprende:

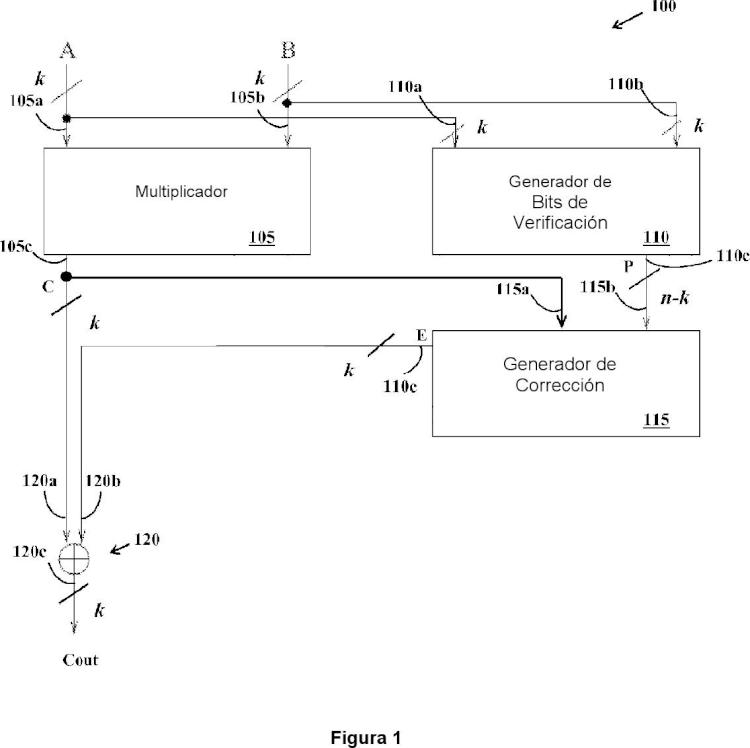

un componente (205) dispuesto para generar una primera salida a partir de una primera entrada y una segunda entrada;

un detector de errores (250) dispuesto para generar un indicador de errores (F) indicativo de si ha detectado o no un error en la primera salida, basándose en la primera salida, la primera entrada y la segunda entrada; un generador de corrección (215) para generar una salida de corrección después de un primer periodo de tiempo que comienza con un evento de temporización en la señal de reloj, basándose en la primera salida, la primera entrada y la segunda entrada; y

un generador de salida (260, 265) dispuesto para generar una salida del circuito corrector de errores después de un segundo periodo de tiempo que comienza con el evento de temporización en la señal de reloj, en el que si el indicador de errores (F) indica que se ha detectado un error en la primera salida entonces el segundo periodo de tiempo es mayor que el primer periodo de tiempo, o si el indicador de errores (F) indica que se ha detectado un error en la primera salida entonces el segundo periodo de tiempo no es mayor que el primer periodo de tiempo,

y en el que si el indicador de errores (F) indica que se ha detectado un error en la primera salida entonces la salida del circuito corrector de errores comprende una combinación de la primera salida y la salida de corrección por lo que el error detectado en la primera salida se corrige, o si el indicador de errores (F) indica que se ha detectado un error en la primera salida entonces la salida del circuito corrector de error corresponde directamente a la primera salida.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/GB2012/051953.

Solicitante: OXFORD BROOKES UNIVERSITY.

Nacionalidad solicitante: Reino Unido.

Dirección: Gipsy Lane Campus, Headington, Oxford Oxfordshire OX3 0BP REINO UNIDO.

Inventor/es: POOLAKKAPARAMBIL,MAHESH, JABIR,ABUSALEH, MATHEW,JIMSON, PRADHAN,DHIRAJ K.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F11/10 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › añadiendo cifras binarias o símbolos especiales a los datos expresados según un código, p. ej. control de paridad, exclusión de los 9 o de los 11.

PDF original: ES-2552305_T3.pdf

Patentes similares o relacionadas:

Método de segmentación de un bloque de transporte en múltiples bloques de código cuando se añade una CRC a cada bloque de código, del 2 de Octubre de 2019, de LG ELECTRONICS INC.: Un método para transmitir datos en un sistema de acceso inalámbrico, el método que comprende: obtener (S601) un número C de bloques de código en base […]

Dispositivo de memoria de semiconductor no volátil, del 28 de Agosto de 2019, de Winbond Electronics Corp: Un dispositivo de almacenamiento de semiconductor no volátil , que comprende: una matriz de memoria ; una pluralidad de circuitos de retención de […]

Seguimiento de cambios usando redundancia en tiempo lógico, del 4 de Junio de 2019, de Microsoft Technology Licensing, LLC: Un método para mantener el seguimiento de cambios entre porciones unitarias de un sistema de almacenaje, comprendiendo el método: […]

Métodos y sistemas para detectar y corregir errores en una memoria no volátil, del 30 de Enero de 2019, de Winbond Electronics Corp: Un sistema de memoria, que comprende: una matriz de memoria no volátil resistiva configurada para almacenar datos, bits de anticipación y bits de […]

Sistemas y métodos para asegurar datos en movimiento, del 9 de Mayo de 2018, de Security First Corp: Un método para leer y escribir un conjunto de datos, que comprende: dividir el conjunto de datos en una o más comparticiones de datos 5 usando un algoritmo […]

Método para procesar datos en Ethernet, circuito integrado de capa física y dispositivo de Ethernet, del 2 de Mayo de 2018, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesamiento de datos de Ethernet, aplicable al procesamiento de datos en un extremo de transmisión, que comprende: * la realización de una codificación […]

Dispositivo de inspección de traducción de dirección, dispositivo de procesamiento central y procedimiento de inspección de traducción de dirección, del 17 de Enero de 2018, de MITSUBISHI HEAVY INDUSTRIES, LTD.: Un dispositivo de comprobación de traducción de dirección que comprende: una unidad de gestión de memoria de traducción entre una dirección virtual y una dirección […]

Procedimiento, dispositivo y sistema de almacenamiento distribuido, del 11 de Octubre de 2017, de HUAWEI TECHNOLOGIES CO., LTD.: Un procedimiento de almacenamiento distribuido, que comprende: dividir un archivo de datos para generar K segmentos de datos, dividir cada segmento de […]