UN BUCLE DE ENGANCHE DE FASE QUE REGULA LA GANANCIA AUTOMATICAMENTE.

Un bucle de enganche de fase, PLL (99) que comprende: un oscilador (110) que proporciona una primera señal de frecuencia;

un oscilador de referencia (125) que proporciona una segunda señal de frecuencia; un detector de fase (100), comprendiendo el detector de fase: una primera entrada del detector de fase (N) acoplada para recibir la primera señal de frecuencia; y una segunda entrada del detector de fase (P) acoplada para recibir la segunda señal de frecuencia; un discriminador de frecuencia (130) configurado para recibir la primera señal de frecuencia y la segunda señal de frecuencia y para proporcionar una primera señal (A) que es proporcional a un error de frecuencia entre la primera señal de frecuencia y la segunda señal de frecuencia; un comparador de ventana (135) acoplado al discriminador de frecuencia (130), estando configurado el comparador de ventana (135) para recibir la primera señal, para comparar la primera señal (A) con los umbrales con relación al error de frecuencia, generar una segunda señal (B), en el que los umbrales definen una ventana de comparación predeterminada; estando acoplado el detector de fase (100) al comparador de ventana (135) para recibir la segunda señal (B), siendo funcional el detector de fase (100) a múltiples ganancias como una función de la segunda señal (B); y comprendiendo el discriminador de frecuencia (130): un circuito aditivo-substractor (430) configurado para recibir la primera señal de frecuencia y la segunda señal de frecuencia y para proporcionar una señal digital; un conversor digital a analógico (420) acoplado al circuito aditivo-substractor (430), estando configurado el conversor digital a analógico (420) para convertir la señal digital en una señal analógica; y un diferenciador (410) acoplado al conversor digital a analógico (420), estando configurado el diferenciador (410) para recibir la señal analógica y para proporcionar la primera señal (A) al comparador de ventana (135) que es representativa de la diferencia entre la primera señal de frecuencia y la segunda señal de frecuencia

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E08000503.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE SAN DIEGO, CA 92121 ESTADOS UNIDOS DE AMERICA.

Inventor/es: MARK V.HARRIS, SMITH,ALAN ANDREW.

Fecha de Publicación: .

Fecha Solicitud PCT: 13 de Diciembre de 2004.

Fecha Concesión Europea: 25 de Agosto de 2010.

Clasificación Internacional de Patentes:

- H03L7/107 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › utilizando una función de transferencia variable para el bucle, p. ej. un filtro pasabajos de anchura de banda variable.

- H03L7/113 H03L 7/00 […] › utilizando un discriminador de frecuencia.

- H03L7/18 H03L 7/00 […] › utilizando un divisor de frecuencia o un contador en el bucle (H03L 7/20, H03L 7/22 tienen prioridad).

Clasificación PCT:

- H03L7/00 H03L […] › Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania.

Fragmento de la descripción:

ANTECEDENTES

La invención se refiere a un bucle de enganche de fase. Más específicamente, la invención se refiere a un bucle de enganche de fase que regula la ganancia automáticamente.

Los teléfonos móviles y otros transceptores de comunicación generalmente comprenden circuitos diferentes de transmisión y recepción que comparten un único sintetizador de frecuencia. El sintetizador de frecuencia sirve como oscilador local para los circuitos tanto de transmisión como de recepción del transceptor. Estos sintetizadores de frecuencia típicamente comprenden un bucle de enganche de fase (PLL) que puede controlarse para que oscile a frecuencias específicas. Cuando el teléfono está recibiendo señales, el PLL estará controlado para que oscile a una frecuencia de recepción y cuando el teléfono está transmitiendo, el PLL estará controlado para oscilar a una frecuencia de transmisión.

Muchos teléfonos móviles modernos están diseñados para funcionar en plurales sistemas celulares diferentes propiedad de diferentes operadores y manipulados según diferentes normas de comunicaciones. Esto habitualmente significa que el receptor del teléfono debe ser capaz de recibir señales a frecuencias ampliamente diferentes y de conmutar rápidamente entre esas frecuencias. Lo mismo sucede con el transmisor.

Cuando el receptor (o transmisor) cambia de una frecuencia a otra, existe un periodo de tiempo en el que el oscilador local no está sincronizado en una frecuencia. No es posible la comunicación durante este periodo de tiempo y el teléfono móvil tiene que esperar a que el oscilador local se sincronice en una frecuencia antes de que puedan reanudarse las comunicaciones por el aire.

Si el oscilador local permanece sin sincronizar en una frecuencia demasiado tiempo, podría interrumpirse el funcionamiento del teléfono. Al final esto provocará la degradación de la percepción del usuario sobre la calidad del servicio. En el peor de los casos podría provocar el cese de la comunicación. Por lo tanto, es deseable minimizar el tiempo que el oscilador permanece sin sincronizar. Un modo de minimizar ese tiempo es disminuir el tiempo que le lleva al PLL cambiar entre diferentes frecuencias.

La ganancia global de un PLL es un factor que afecta a la velocidad a la que el PLL puede cambiar de una frecuencia de funcionamiento a otra. Un PLL con una elevada ganancia cambiará más rápidamente entre frecuencias que un PLL con una ganancia inferior. Un PLL con ganancia inferior es más estable una vez sincronizado en la frecuencia deseada. Sin embargo, cuando se usa un PLL de ganancia inferior para grandes cambios de frecuencia, puede suceder un estado conocido como salto de ciclo. El salto de ciclo sucede cuando el error de fase aumenta y excede los 360 grados. En el punto en el que el error de fase excede los 360 grados hay una transición brusca. Cuando un PLL encuentra esta transición brusca, generalmente alarga enormemente el tiempo que lleva a un PLL a volver a menos de 360 grados de error y sincronizarse en una nueva frecuencia. Un PLL de mayor ganancia generalmente tolerará cambios de frecuencia más grandes sin que suceda el salto de ciclo.

Para sacar provecho de los beneficios de una ganancia tanto alta como baja en un PLL, los sistemas actuales tienden a utilizar PLL con ganancia seleccionable. Los PLL disponibles en el mercado generalmente ofrecen una elección de valores de ganancia programables para el detector de fase. Ajustando la ganancia del detector de fase, puede ajustarse la ganancia global del PLL. Se selecciona una ganancia baja cuando el PLL está sincronizado en una frecuencia y se selecciona una alta ganancia durante los cambios de una frecuencia a otra.

Las tecnologías actuales que usan diferentes ganancias del detector de fase implican programar el detector de fase para cada cambio de ganancia. Por ejemplo, un PLL está programado a una primera frecuencia o inicial. Cuando se sincroniza en esta primera frecuencia, el detector de fase está a baja ganancia. Cuando se inicia un cambio en la frecuencia, el PLL está programado a una segunda frecuencia; y, el detector de fase está programado simultáneamente a alta ganancia. Según el PLL se acerca a la segunda frecuencia, el detector de fase entonces se re-programa a baja ganancia. Como alternativa, el detector de fase podría re-programarse para reducir la ganancia en base al tiempo a alta ganancia en lugar de la proximidad de la segunda frecuencia.

La re-programación repetida del PLL consume un tiempo valioso del procesador en las técnicas actuales.

Llama la atención el documento US 6 188 289 que describe un oscilador controlado por tensión de amplio intervalo que incluye una unidad de conversión de tensión-a-corriente que genera una corriente de control receptiva a tensión de control, y una unidad de generación de corriente desviada que genera una corriente desviada. La unidad de generación de corriente desviada es receptiva a la tensión de control y, en ciertos momentos, es receptiva a una tensión de referencia. Una unidad de adición añade la corriente de control a la corriente desviada, y genera una corriente de control de la oscilación. Una unidad de oscilación genera la señal de oscilación receptiva a la corriente de control de la oscilación.

Adicionalmente llama la atención el documento EP-A-0 732 830 que describe que el circuito para la extracción de la señal de reloj desde una corriente de datos de alta velocidad permite una rápida obtención de la identidad entre las frecuencias de la señal de reloj localmente generada y de la señal de datos, incluso cuando dichas frecuencias son muy diferentes. El circuito comprende un bucle de enganche de fase principal, que controla un oscilador controlado por tensión controlando continuamente su fase, y un bucle secundario, que permite que el bucle principal llegue a sincronizarse, causando que el oscilador controlado por tensión oscile a una frecuencia cercana a la frecuencia de funcionamiento.

Llama la atención el documento US 3 750 035 que describes circuitos discriminadores de frecuencia y detectores de fase, teniendo cada uno dos circuitos basculantes, un circuito basculante por cada una de las dos señales a comparar, y un medio para causar que un circuito basculante esté regulado la mayoría del tiempo en proporción al grado al que una señal difiere de la otra en frecuencia o fase, y un medio para integrar la diferencia entre formas de onda de salida de los circuitos basculantes para obtener una señal de salida Eo que puede usarse para ajustar la frecuencia y fase de una señal variable V con respecto a una señal de referencia R.

Adicionalmente llama la atención el documento US-B 6 356 158 que describe que un bucle de enganche de fase (PLL) que tiene un amplio intervalo de frecuencias de salida del oscilador y un amplio intervalo de valores del divisor de bucle es factible en forma integrada porque la capacitancia total de su filtro de bucle es pequeña. El PLL incluye un primer detector de fase, un segundo detector de fase, un oscilador programable de línea de retardo por derivación, un divisor de bucle dividir-por-M, y un filtro de bucle programable en chip. El filtro programable está programado para tener en cuenta uno de muchos filtros de bucle. En una primera etapa, se realimenta la salida del oscilador mediante el divisor de bucle hasta el primer detector de fase. La frecuencia del oscilador se reduce cambiando la selección de conexión dentro de la unidad de oscilador hasta que el primer detector de fase determine que la frecuencia de la realimentación de señal mediante el divisor de bucle (dividir-por-M) es más pequeña que la frecuencia de una señal de entrada. El control de conexión al que sucede este estado de sincronización de frecuencia, junto con el valor M, se usa después para determinar cual de los muchos filtros de bucle se usará en una etapa de enganche de bucle. El filtro de bucle programable se controla para tener en cuenta el filtro de bucle seleccionado y el filtro de bucle seleccionado se conmuta en un bucle de control que implica el segundo detector de fase. El bucle de control controla el oscilador para conseguir el enganche de fase variando una tensión de suministro suministrada al oscilador.

De acuerdo con la presente invención, se proporciona un bucle de enganche de fase, PLL, que regula la ganancia automáticamente, como se expone en la reivindicación 1. Las realizaciones preferidas de la invención se reivindican en las reivindicaciones dependientes.

El PLL comprende un discriminador de frecuencia para proporcionar una primera...

Reivindicaciones:

1. Un bucle de enganche de fase, PLL (99) que comprende: un oscilador (110) que proporciona una primera señal de frecuencia; un oscilador de referencia (125) que proporciona una segunda señal de frecuencia; un detector de fase (100), comprendiendo el detector de fase:

una primera entrada del detector de fase (N) acoplada para recibir la primera señal de frecuencia; y

una segunda entrada del detector de fase (P) acoplada para recibir la segunda señal de frecuencia; un discriminador de frecuencia (130) configurado para recibir la primera señal de

frecuencia y la segunda señal de frecuencia y para proporcionar una primera señal (A) que es proporcional a un error de frecuencia entre la primera señal de frecuencia y la segunda señal de frecuencia;

un comparador de ventana (135) acoplado al discriminador de frecuencia (130), estando configurado el comparador de ventana (135) para recibir la primera señal, para comparar la primera señal (A) con los umbrales con relación al error de frecuencia, generar una segunda señal (B), en el que los umbrales definen una ventana de comparación predeterminada;

estando acoplado el detector de fase (100) al comparador de ventana (135) para recibir la segunda señal (B), siendo funcional el detector de fase (100) a múltiples ganancias como una función de la segunda señal (B); y

comprendiendo el discriminador de frecuencia (130): un circuito aditivo-substractor (430) configurado para recibir la primera señal de frecuencia y la segunda señal de frecuencia y para proporcionar una señal digital;

un conversor digital a analógico (420) acoplado al circuito aditivo-substractor (430), estando configurado el conversor digital a analógico (420) para convertir la señal digital en una señal analógica; y

un diferenciador (410) acoplado al conversor digital a analógico (420), estando configurado el diferenciador (410) para recibir la señal analógica y para proporcionar la primera señal (A) al comparador de ventana (135) que es representativa de la diferencia entre la primera señal de frecuencia y la segunda señal de frecuencia.

2. El PLL (99) de la reivindicación 1, en el que el detector de fase (100) es funcional a dos ganancias.

3. El PLL (99) de la reivindicación 1, en el que los umbrales comprenden un primer valor umbral (a) que corresponde a un primer valor del error de frecuencia y un segundo valor umbral

(b) que corresponde a un segundo valor del error de frecuencia.

4. El PLL (99) de la reivindicación 1, en el que dichos umbrales comprenden un primer umbral que corresponde a una primera velocidad de cambio del error de frecuencia y un segundo umbral que corresponde a una segunda velocidad de cambio del error de frecuencia.

5. El PLL (99) de cualquiera de las reivindicaciones 3 a 4, en el que la ganancia del 10 detector de fase (100) se regula a un valor de ganancia mayor para valores de la primera señal

(A) que están fuera de la ventana de comparación predeterminada y la ganancia del detector de fase (100) se regula a un valor de ganancia inferior para valores de la primera señal (A) que están dentro de la ventana de comparación predeterminada.

15 6. Un teléfono que comprende el PLL (99) de cualquiera de las reivindicaciones 1 a 5.

7. El teléfono de la reivindicación 6, funcional de acuerdo con la norma GSM.

Patentes similares o relacionadas:

Circuito de transmisión, circuito de recepción, método y sistema de transmisión de datos, del 27 de Mayo de 2015, de Thine Electronics, Inc: Un método de transferencia de datos digitales para transferir de forma alterna y periódica una primera información y una segunda información respectivamente en un primer periodo […]

BUCLE DE ENGANCHE DE FASE QUE REGULA LA GANANCIA AUTOMÁTICAMENTE, del 26 de Abril de 2011, de QUALCOMM INCORPORATED: Un procedimiento para regular automáticamente la ganancia en un bucle de enganche en fase, PLL , en el cual el PLL comprende un detector de fase, comprendiendo […]

BUCLE DE ENGANCHE DE FASE QUE REGULA LA GANANCIA AUTOMÁTICAMENTE, del 26 de Abril de 2011, de QUALCOMM INCORPORATED: Un procedimiento para regular automáticamente la ganancia en un bucle de enganche en fase, PLL , en el cual el PLL comprende un detector de fase, comprendiendo […]

PROCEDIMIENTO Y DISPOSICION PARA ENCLAVAR UN OSCILADOR DE YIG., del 16 de Marzo de 2004, de DAIMLERCHRYSLER AEROSPACE AKTIENGESELLSCHAFT: EL OBJETIVO DE LA INVENCION ES SUMINISTRAR UN PROCESO DE SINCRONIZADO PARA UN OSCILADOR YIG, QUE TIENE EN CUENTA EL ENVEJECIMIENTO Y LA HISTERESIS DEL OSCILADOR […]

APARATO DE BUCLE DE ENGANCHE DE FASE., del 1 de Marzo de 2007, de MARCONI MOBILE SPA: Un aparato de bucle de enganche de fase, que comprende un primer bucle de enganche de fase que tiene un detector de fase de muestreo dispuesto para […]

Linealizador de forma de onda, del 12 de Junio de 2019, de MBDA UK LIMITED: Una fuente de barrido de frecuencia para un radar FMCW que comprende un sintetizador de frecuencia de bucle de bloqueo de fase, incluyendo el bucle bloqueado […]

SINTETIZADORES DE FRECUENCIA PARA SOPORTE DE ESTANDARES DE COMUNICACION DE VOZ Y DE CONEXION EN RED SIN HILOS., del 1 de Junio de 2007, de QUALCOMM INCORPORATED: A procedimiento de procesado de señales de radiofrecuencia que comprende: generación de una primera forma de onda en un dispositivo de comunicación sin hilos usando […]

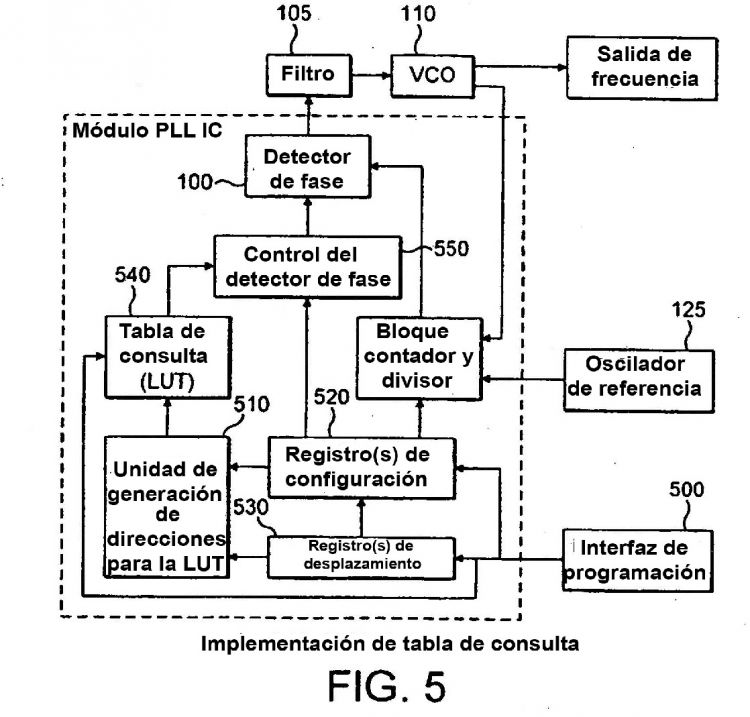

UN CICLO DE FASE CERRADA., del 1 de Abril de 2007, de QUALCOMM INCORPORATED: Un mecanismo que comprende: Un ciclo de fase cerrada ; Un primer conjunto de registros para contener los datos definiendo un modo de operación del ciclo […]

AJUSTE DIGITAL AFC MEDIANTE DOS RECIPROCOS., del 16 de Noviembre de 2006, de SIEMENS AKTIENGESELLSCHAFT: La presente invención se refiere a un circuito automático de frecuencia (C.A.F) con un oscilador , un sistema de síntesis digital (DDS) […]