APARATO Y METODO DE PROCESAMIENTO DE DATOS.

Un aparato de procesamiento de datos operativo para mapear símbolos de datos recibidos desde un número predeterminado de señales de subportadoras de un símbolo Multiplexado por División de Frecuencias Ortogonales,

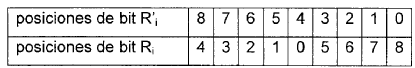

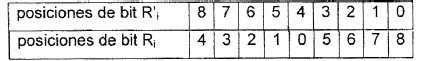

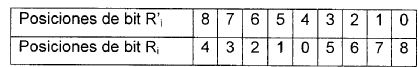

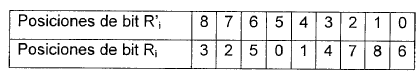

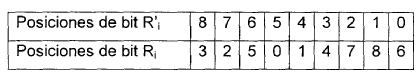

OFDM, en un flujo de símbolos de salida, comprendiendo el aparato de procesamiento un desintercalador (314) operativo para ingresar en una memoria (540) del intercalador el número predeterminado de símbolos de datos a partir de las señales de subportadora OFDM, y para leer desde la memoria (540) los símbolos de datos hacia el flujo de símbolos de datos para realizar el mapeo, siendo la lectura de salida en un orden diferente al ingreso, determinándose el orden a partir de un conjunto de direcciones, con la consecuencia de que los símbolos de datos son desintercalados a partir de las señales de subportadora OFDM, un generador (542) de direcciones operativo para generar el conjunto de direcciones, generándose una dirección para cada uno de los símbolos de datos recibidos, con el objeto de indicar la señal subportadora OFDM desde la que el símbolo de datos recibido ha de mapearse en el flujo de símbolos de salida, comprendiendo el generador (542) de direcciones un registro (200) de desplazamiento de retroalimentación lineal que incluye un número predeterminado de etapas del registro y que es operativo para generar una secuencia de bits pseudoaleatoria de acuerdo con un polinomio generador, un circuito (210) de permutación operativo para recibir el contenido de las etapas (200) del registro de desplazamiento y para permutar los bits presentes en las etapas del registro de acuerdo con un código de permutación con el objeto de formar una dirección de una de las subportadoras OFDM, y una unidad de control (224) operativa en combinación con un circuito (216) de verificación de direcciones, para regenerar una dirección cuando una dirección generada excede una dirección válida máxima predeterminada, caracterizado porque la dirección válida máxima predeterminada es menor que mil veinticuatro, el registro (200) de desplazamiento de retroalimentación lineal tiene nueve etapas de registro con un polinomio generador para el registro de desplazamiento de retroalimentación lineal, de R''i[8] = R''i-1[0] R''i-1[4], y el código de permutación forma, con un bit adicional, una dirección de diez bits R i[n] para el i-ésimo símbolo de datos a partir del bit presente en la n-ésima etapa de registro ''R-i[n], de acuerdo con la tabla: **(Ver fórmula)**

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E08253420.

Solicitante: SONY CORPORATION.

Nacionalidad solicitante: Japón.

Dirección: 1-7-1 KONAN, MINATO-KU,TOKYO.

Inventor/es: TAYLOR,MATTHEW PAUL ATHOL, ATUNGSIRI,SAMUEL ASANGBENG, WILSON,JOHN NICHOLAS.

Fecha de Publicación: .

Fecha Solicitud PCT: 22 de Octubre de 2008.

Fecha Concesión Europea: 16 de Septiembre de 2009.

Clasificación Internacional de Patentes:

- H03M13/27 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › usando técnicas de entrelazado.

- H04L27/26M

Clasificación PCT:

- H03M13/27 H03M 13/00 […] › usando técnicas de entrelazado.

- H04L1/00 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › Disposiciones para detectar o evitar errores en la información recibida.

- H04L27/26 H04L […] › H04L 27/00 Sistemas de portadora modulada. › Sistemas utilizando códigos de frecuencias múltiples (H04L 27/32 tiene prioridad).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Aparato y método de procesamiento de datos.

Campo de la invención

La presente invención se refiere a aparatos de procesamiento de datos operativos para mapear símbolos de datos recibidos desde un número predeterminado de señales de subportadora de un símbolo OFDM en un flujo de símbolos de salida. La presente invención se refiere también a generadores de direcciones para utilizar en la escritura de símbolos en, y lectura de símbolos desde, la memoria del intercalador.

Las realizaciones de la presente invención pueden proporcionar un receptor OFDM.

Antecedentes de la invención

El estándar Difusión de Video Digital - Terrestre (Digital Video Broadcasting-Terrestrial, DVB-T) utiliza Multiplexado por División de Frecuencias Ortogonales (OFDM, Orthogonal Frequency Division Multiplexing) para comunicar a receptores datos que representan imágenes de video y sonido, a través de una señal de difusión de comunicaciones por radio. Es sabido que hay dos modos para el estándar DVB-T que se conocen como el modo 2k y el modo 8k. El modo 2k proporciona 2048 subportadoras mientras que el modo 8k proporciona 8192 subportadoras. Análogamente, para el estándar Difusión de Video Digital - Portátil (DVB-H, Digital Video Broadcasting - Handheld) se ha previsto un modo 4k en el que el número de subportadoras es de 4096.

Para mejorar la integridad de los datos comunicados utilizando DVB-T o DVB-H se proporciona un intercalador de símbolos para intercalar símbolos de datos de entrada a medida que estos símbolos son mapeados en las señales de subportadora de un símbolo OFDM. Un intercalador de símbolos semejante comprende una memoria de intercalador en combinación con un generador de direcciones. El generador de direcciones genera una dirección para cada uno de los símbolos de entrada, indicando cada dirección una de las señales de subportadora del símbolo OFDM sobre la cual se ha de mapear el símbolo de datos. Para el modo 2k y el modo 8k se ha descrito una disposición en el estándar DVB-T para generar las direcciones para el mapeo. Análogamente, para el modo 4k del estándar DVB-H se ha previsto una disposición para generar direcciones para el mapeo y en la solicitud de patente europea EP-A-1 463 256 se describe un generador de direcciones para implementar este mapeo. El generador de direcciones comprende un registro de desplazamiento de retroalimentación lineal que sirve para generar una secuencia de bits pseudoaleatoria y un circuito de permutación. El circuito de permutación permuta el orden del contenido del registro de desplazamiento de retroalimentación lineal, para generar una dirección. La dirección proporciona una indicación de una localización de memoria de la memoria de intercalador, para escribir el símbolo de datos de entrada en la memoria de intercalador, o leer el símbolo datos de entrada desde esta, para el mapeo en una de las señales de subportadora del símbolo OFDM. Análogamente, se dispone un generador de direcciones en el receptor para generar direcciones de la memoria del intercalador, con el objeto de escribir los símbolos de datos recibidos en la memoria de intercalador, o leer los símbolos de datos desde esta para formar un flujo de datos de salida.

En un artículo publicado titulado "DVB-RCT: A standard for Interactive DVB-T", de G. Faria y F. Scalise, se describen dos sistemas para implementar un canal de retorno para DVB Terrestre.

En el documento US 6 353 900 se describe un intercalador que incluye un generador de direcciones para generar una dirección de una memoria del intercalador utilizando un generador de números pseudoaleatorios. Los datos se escriben en la memoria de intercalador en orden secuencial, y a continuación se leen utilizando direcciones especificadas por el generador de direcciones.

De acuerdo con otro desarrollo del estándar de difusión denominado Difusión de Video Digital - Terrestre y conocido como DVB-T2, se ha propuesto la posibilidad de proporcionar otros modos para comunicar datos.

Compendio de la invención

De acuerdo con un aspecto de la presente invención se proporciona un aparato de procesamiento de datos dispuesto para, en funcionamiento, mapear símbolos de datos recibidos desde una serie predeterminada de señales de subportadora de un símbolo Multiplexado por División de Frecuencias Ortogonales (OFDM) en un flujo de símbolos de salida. El aparato de procesamiento de datos comprende un desintercalador dispuesto para ingresar en una memoria de intercalador el número predeterminado de símbolos de datos procedentes de las señales de subportadora OFDM, y para leer desde la memoria los símbolos de datos hacia el flujo de símbolos de salida con el objeto de llevar a cabo el mapeo, siendo la lectura de salida en un orden diferente a la lectura de entrada, determinándose el orden a partir de un conjunto de direcciones, con la consecuencia de que los símbolos de datos son desintercalados desde las señales de subportadora OFDM. Se dispone un generador de direcciones para generar el conjunto de direcciones, generándose una dirección para cada uno de los símbolos de datos recibidos, con el objeto de indicar la señal subportadora OFDM desde la que ha de mapearse el símbolo de datos recibido, en el flujo de símbolos de salida.

El generador de direcciones comprende un registro de desplazamiento de retroalimentación lineal que incluye un número predeterminado de etapas de registro y es operativo para generar una secuencia de bits pseudoaleatoria de acuerdo con un polinomio generador, un circuito de permutación y una unidad de control. El circuito de permutación es operativo para recibir el contenido de las etapas de los registros de desplazamiento y para permutar los bits presentes en las etapas de los registros de acuerdo con un código de permutación, con el objeto de crear una dirección de una de las subportadoras OFDM.

La unidad de control es operativa en combinación con un circuito de verificación de direcciones para regenerar una dirección, cuando una dirección generada excede una dirección válida máxima predeterminada. El aparato de procesamiento de datos está caracterizado porque la dirección válida máxima predeterminada es menor que mil veinticuatro, el registro de desplazamiento de retroalimentación lineal tiene nueve etapas de registro con un polinomio generador para el registro de desplazamiento de retroalimentación lineal, de R'i[8] = R'i-1[0]? R'i-1[4], y el código de permutación forma, con un bit adicional, una dirección de diez bits Ri[n] para el i-ésimo símbolo de datos a partir del bit presente en la n-ésima etapa del registro R'i[n], de acuerdo con la tabla:

Aunque dentro del estándar DVB-T se conoce el proporcionar el modo 2k y el modo 8k, y el estándar DVB-H proporciona un modo 4k, se ha propuesto proporcionar un modo 1k para DVB-T2. Si bien el modo 8k proporciona una disposición para establecer una red de una sola frecuencia con suficientes períodos de protección para acomodar mayores retardos de propagación entre transmisores DVB, es sabido que el modo 2k proporciona una ventaja en aplicaciones móviles. Esto se debe a que el período de símbolos 2k es solo la cuarta parte del período de símbolos 8k, lo que permite que la estimación de canal se actualice con mayor frecuencia permitiendo que el receptor siga con mayor precisión la variación temporal del canal debida a efecto Doppler y otros. Por lo tanto el modo 2k es ventajoso para aplicaciones móviles. Sin embargo, se ha planteado la necesidad de un sistema de comunicaciones OFDM acorde con el estándar DVB-T2 para comunicar en entornos incluso más severos, lo que requiere que un receptor trabaje con mayores variaciones temporales en el canal de comunicaciones, tal como en aplicaciones móviles. Por lo tanto se ha propuesto un modo 1k, aunque con el modo 1k se necesitará una red de múltiples frecuencias que complica una disposición de transmisores para proporcionar un sistema de difusión. Sin embargo, para proporcionar el modo 1k debe proporcionarse un intercalador de símbolos para mapear los símbolos de datos de entrada a las señales de subportadora del símbolo OFDM.

Las realizaciones de la presente invención pueden proporcionar un aparato de procesamiento de datos operativo como un intercalador de símbolos para mapear símbolos de datos recibidos desde un símbolo OFDM, en un flujo de datos de salida, en el que el número de las subportadoras del símbolo OFDM que llevan los símbolos...

Reivindicaciones:

1. Un aparato de procesamiento de datos operativo para mapear símbolos de datos recibidos desde un número predeterminado de señales de subportadoras de un símbolo Multiplexado por División de Frecuencias Ortogonales, OFDM, en un flujo de símbolos de salida, comprendiendo el aparato de procesamiento

un desintercalador (314) operativo para ingresar en una memoria (540) del intercalador el número predeterminado de símbolos de datos a partir de las señales de subportadora OFDM, y para leer desde la memoria (540) los símbolos de datos hacia el flujo de símbolos de datos para realizar el mapeo, siendo la lectura de salida en un orden diferente al ingreso, determinándose el orden a partir de un conjunto de direcciones, con la consecuencia de que los símbolos de datos son desintercalados a partir de las señales de subportadora OFDM,

un generador (542) de direcciones operativo para generar el conjunto de direcciones, generándose una dirección para cada uno de los símbolos de datos recibidos, con el objeto de indicar la señal subportadora OFDM desde la que el símbolo de datos recibido ha de mapearse en el flujo de símbolos de salida, comprendiendo el generador (542) de direcciones

un registro (200) de desplazamiento de retroalimentación lineal que incluye un número predeterminado de etapas del registro y que es operativo para generar una secuencia de bits pseudoaleatoria de acuerdo con un polinomio generador,

un circuito (210) de permutación operativo para recibir el contenido de las etapas (200) del registro de desplazamiento y para permutar los bits presentes en las etapas del registro de acuerdo con un código de permutación con el objeto de formar una dirección de una de las subportadoras OFDM, y

una unidad de control (224) operativa en combinación con un circuito (216) de verificación de direcciones, para regenerar una dirección cuando una dirección generada excede una dirección válida máxima predeterminada, caracterizado porque

la dirección válida máxima predeterminada es menor que mil veinticuatro,

el registro (200) de desplazamiento de retroalimentación lineal tiene nueve etapas de registro con un polinomio generador para el registro de desplazamiento de retroalimentación lineal, de R'i[8] = R'i-1[0]? R'i-1[4], y el código de permutación forma, con un bit adicional, una dirección de diez bits Ri[n] para el i-ésimo símbolo de datos a partir del bit presente en la n-ésima etapa de registro R'i[n], de acuerdo con la tabla:

2. Un aparato de procesamiento de datos como el reivindicado en la reivindicación 1, en el que la dirección válida máxima predeterminada es un valor entre setecientos y mil veinticuatro.

3. Un aparato de procesamiento de datos como el reivindicado en la reivindicación 1 o 2, en el que el símbolo OFDM incluye subportadoras piloto, que están dispuestas para transportar símbolos conocidos, y la dirección válida máxima predeterminada depende de un número de los símbolos de subportadoras piloto presentes en el símbolo OFDM.

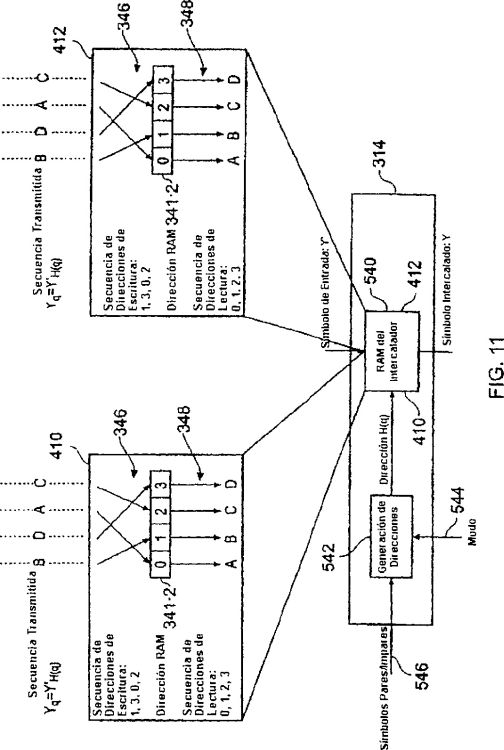

4. Un aparato de procesamiento de datos como el reivindicado en la reivindicación 1, 2 o 3, en el que la memoria (540) del desintercalador está dispuesta para efectuar el mapeo de los símbolos de datos recibidos desde las señales de subportadora sobre el flujo de datos de salida, para símbolos OFDM pares mediante la acción de ingresar los símbolos de datos de acuerdo con un orden secuencial y leer los símbolos de datos desde la memoria (540) en función de un conjunto de direcciones generadas por el generador (542) de direcciones, y para símbolos OFDM impares mediante la acción de ingresar los símbolos en la memoria (540) de acuerdo con el conjunto de direcciones generadas por el generador (542) de direcciones y leer los símbolos de datos desde la memoria (540) de acuerdo con un orden secuencial.

5. Un aparato de procesamiento de datos como el reivindicado en cualquiera de las reivindicaciones 1 a 4, en el que el circuito (210) de permutación es operativo para cambiar el código de permutación, que permuta el orden de los bits de las etapas de registro para formar las direcciones, desde un símbolo OFDM a otro.

6. Un aparato de procesamiento de datos como el reivindicado en la reivindicación 5, en el que el circuito de permutación (210) es operativo para funcionar cíclicamente a través de una secuencia de diferentes códigos de permutación para sucesivos símbolos OFDM.

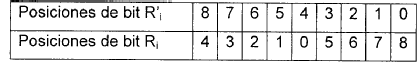

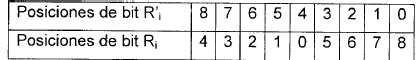

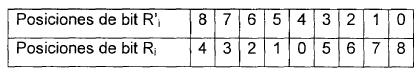

7. Un aparato de procesamiento de datos como el reivindicado en la reivindicación 6, en el que la secuencia de códigos de permutación comprende dos códigos de permutación, que son:

8. Un aparato de procesamiento de datos como el reivindicado en la reivindicación 6 o 7, en el que las subportadoras de los símbolos OFDM son la mitad o menos de la mitad de un número máximo de subportadoras en los símbolos OFDM de cualquiera de una pluralidad de modos operativos, y los símbolos de datos incluyen primeros conjuntos de símbolos de datos recibidos desde símbolos OFDM pares, y segundos conjuntos de símbolos de datos recibidos desde símbolos OFDM impares, y el aparato de procesamiento de datos es operativo para desintercalar los conjuntos primero y segundo de datos de símbolos en el flujo de datos de salida de acuerdo con un proceso de intercalación impar,

incluyendo el proceso de intercalación impar

escribir los primeros conjuntos de símbolos de datos recibidos desde las subportadoras de los símbolos OFDM pares en una primera parte (410) de la memoria (540) del intercalador, de acuerdo con un orden determinado por el conjunto de direcciones generadas con uno de los códigos de permutación de la secuencia,

leer los primeros conjuntos de símbolos de datos desde la primera parte (410) de la memoria (540) del intercalador hacia el flujo de datos de salida, de acuerdo con un orden secuencial de los primeros conjuntos de símbolos de datos de entrada,

escribir el segundo conjunto de símbolos de datos recibidos desde las subportadoras de los símbolos OFDM impares en una segunda parte (412) de la memoria (540) del intercalador, de acuerdo con un orden definido por el conjunto de direcciones generadas con otro de los códigos de permutación de la secuencia, y

leer los segundos conjuntos de símbolos de datos desde la segunda parte (412) de la memoria (540) del intercalador hacia el flujo de datos de salida de acuerdo con un orden secuencial de los segundos conjuntos de símbolos de datos de entrada.

9. Un receptor para recibir datos desde una señal modulada con Multiplexado por División de Frecuencias Ortogonales, OFDM, incluyendo el receptor un aparato de procesamiento de datos acorde con cualquiera de las reivindicaciones 1 a 8, siendo el aparato de procesamiento de datos operativo para mapear símbolos de datos recibidos desde un número predeterminado de señales de subportadora de un símbolo Multiplexado por División de Frecuencias Ortogonales, OFDM, en un flujo de símbolos de salida.

10. Un receptor como el reivindicado en la reivindicación 9, en el que el receptor es operativo para recibir datos que han sido modulados de acuerdo con un estándar de Difusión de Video Digital tal como el estándar de Difusión de Video Digital - Terrestre, el estándar de Difusión de Video Digital - Portátil, el estándar de Difusión de Video Digital - Terrestre 2 o el estándar de Difusión de Video Digital - Cable 2.

11. Un generador (542) de direcciones para ser utilizado en la recepción de símbolos de datos intercalados en subportadoras de un símbolo Multiplexado por División de Frecuencias Ortogonales, siendo el generador (542) de direcciones operativo para generar un conjunto de direcciones, siendo cada dirección generada para cada uno de los símbolos de datos con el objeto de indicar una de las señales de subportadora desde la que ha de mapearse el símbolo de datos recibido, desde una memoria de intercalador hacia un flujo de datos de salida, comprendiendo el generador (542) de direcciones

un registro (200) de desplazamiento de retroalimentación lineal que incluye un número predeterminado de etapas de registro y que es operativo para generar una secuencia de bits pseudoaleatoria de acuerdo con un polinomio generador,

un circuito (210) de permutación operativo para recibir el contenido de las etapas del registro de desplazamiento y para permutar los bits presentes en las etapas de registro de acuerdo con un código de permutación para formar una dirección, y

una unidad de control (224) operativa en combinación con un circuito (216) de verificación de direcciones, para regenerar una dirección cuando una dirección generada excede una dirección válida máxima predeterminada, caracterizado porque

la dirección válida máxima predeterminada es menor que mil veinticuatro,

el registro de desplazamiento de retroalimentación lineal tiene nueve etapas de registro con un polinomio generador para el registro de desplazamiento de retroalimentación lineal, de R'i[8] = R'i-1[0]? R'i-1[4], y el orden de permutación forma, con un bit adicional, una dirección de diez bits Ri[n] para el i-ésimo símbolo de datos a partir del bit presente en la n-ésima etapa de registro R'i[n], de acuerdo con un código definido por la tabla:

12. Un método para mapear símbolos recibidos desde un número predeterminado de señales de subportadora de un símbolo Multiplexado por División de Frecuencias Ortogonales, OFDM, en un flujo de símbolos de salida, comprendiendo el método

ingresar en una memoria (540) de intercalador el número predeterminado de símbolos de datos a partir de las señales de subportadora OFDM,

leer desde la memoria (540) del intercalador los símbolos de datos, hacia el flujo de símbolos de salida para efectuar el mapeo, siendo la lectura de salida en un orden diferente que el ingreso, determinándose el orden a partir de un conjunto de direcciones, con la consecuencia de que los símbolos de datos son desintercalados a partir de las señales de subportadora OFDM,

generar el conjunto de direcciones, generándose la dirección para cada uno de los símbolos de datos recibidos, con el objeto de indicar la señal subportadora OFDM desde la que ha de mapearse el símbolo de datos recibido, desde la memoria (540) del intercalador hacia el flujo de símbolos de salida, comprendiendo la generación del conjunto de direcciones

utilizar un registro (200) de desplazamiento de retroalimentación lineal que incluye un número predeterminado de etapas de registro, para generar una secuencia de bits pseudoaleatoria de acuerdo con un polinomio generador,

utilizar un circuito (210) de permutación para recibir el contenido de las etapas del registro de desplazamiento y para permutar los bits presentes en las etapas del registro de acuerdo con un código de permutación para formar una dirección, y

regenerar una dirección cuando una dirección generada excede una dirección válida máxima predeterminada, caracterizado porque

la dirección válida máxima predeterminada es menor que mil veinticuatro,

el registro (200) de desplazamiento de retroalimentación lineal tiene nueve etapas de registro con un polinomio generador para el registro de desplazamiento de retroalimentación lineal, de R'i[8] = R'i-1[0]? R'i-1[4], y el orden de permutación forma, con un bit adicional, una dirección de diez bits Ri[n] para el i-ésimo símbolo de datos a partir del bit presente en la n-ésima etapa de registro R'i[n], de acuerdo con la tabla:

13. Un método como el reivindicado en la reivindicación 12, en el que la dirección válida máxima predeterminada es un valor entre setecientos y mil veinticuatro.

14. Un método como el reivindicado en la reivindicación 12 o 13, en el que el símbolo OFDM incluye subportadoras piloto que están dispuestas para transportar símbolos conocidos, y la dirección válida máxima predeterminada depende de un número de los símbolos de subportadoras piloto presentes en el símbolo OFDM.

15. Un método como el reivindicado en la reivindicación 12, 13 o 14, en el que el ingreso en la memoria (540) del intercalador, del número predeterminado de símbolos de datos a partir de las señales de subportadora OFDM, y la lectura de salida desde la memoria (540) del intercalador, de los símbolos de datos hacia el flujo de símbolos de salida para efectuar el mapeo, incluye

para símbolos OFDM pares, ingresar los símbolos de datos de acuerdo con un orden secuencial, y

leer los símbolos de datos desde la memoria (540) del intercalador, de acuerdo con un conjunto de direcciones generadas por el generador (542) de direcciones, y

para símbolos OFDM impares, ingresar los símbolos de datos en la memoria (540) del intercalador de acuerdo con el conjunto de direcciones generadas por el generador (542) direcciones, y

leer los símbolos de datos desde la memoria de acuerdo con un orden secuencial.

16. Un método como el reivindicado en cualquiera de las reivindicaciones 12 a 15, en el que usar un circuito de permutación (210) para recibir el contenido de las etapas (200) del registro de desplazamiento y permutar los bits presentes en las etapas del registro de acuerdo con el código de permutación para formar una dirección, incluye cambiar el código de permutación, que permuta el orden de los bits de las etapas del registro para formar una dirección, desde un símbolo OFDM a otro.

17. Un método como el reivindicado en la reivindicación 16, en el que el cambio del código de permutación, que permuta el orden de los bits de las etapas del registro para formar las direcciones, desde un símbolo OFDM a otro, incluye realizar un ciclo a través de una secuencia de diferentes códigos de permutación para sucesivos símbolos OFDM.

18. Un método como el reivindicado en la reivindicación 17, en el que la secuencia de códigos de permutación comprende dos códigos de permutación, que son:

19. Un método como el reivindicado en la reivindicación 16, 17 o 18, en el que las subportadoras de los símbolos OFDM son la mitad o menos de la mitad de un número máximo de subportadoras en los símbolos OFDM de cualquiera de una pluralidad de modos operativos, comprendiendo el método

recibir primeros conjuntos de símbolos de datos desde símbolos OFDM pares y segundos conjuntos de símbolos de datos desde símbolos OFDM impares, y el ingreso en la memoria (540) del intercalador de los símbolos de datos recibidos desde las señales de subportadora OFDM y la lectura desde la memoria del intercalador de los símbolos de datos hacia el flujo de símbolos de salida para efectuar el mapeo, es de acuerdo con un proceso de intercalación impar, incluyendo el proceso de intercalación impar

escribir los primeros conjuntos de símbolos de datos recibidos desde las subportadoras de los símbolos OFDM pares en una primera parte (410) de la memoria (540) del intercalador de acuerdo con un orden determinado por el conjunto de direcciones generadas con uno de los códigos de permutación de la secuencia,

leer los primeros conjuntos de símbolos de datos desde la primera parte (410) de la memoria (540) del intercalador hacia el flujo de datos de salida de acuerdo con un orden secuencial de los primeros conjuntos de símbolos de datos de entrada,

escribir el segundo conjunto de símbolos de datos recibidos desde las subportadoras de los símbolos OFDM impares en una segunda parte (412) de la memoria (540) del intercalador de acuerdo con un orden definido por el conjunto de direcciones generadas con otro de los códigos de permutación de la secuencia, y

leer los segundos conjuntos de símbolos de datos desde la segunda parte (412) de la memoria (540) del intercalador hacia el flujo de datos de salida de acuerdo con un orden secuencial de los segundos conjuntos de símbolos de datos de entrada.

20. Un método de recepción de datos a partir de símbolos modulados con Multiplexado por División de Frecuencias Ortogonales, OFDM, incluyendo el método

mapear símbolos recibidos desde un número predeterminado de señales de subportadora de un símbolo Multiplexado por División de Frecuencias Ortogonales, OFDM, en un flujo de símbolos de salida de acuerdo con cualquiera de las reivindicaciones 12 a 19.

21. Un método de recepción como el reivindicado en la reivindicación 20, en el que la recepción de los símbolos de datos desde las señales de subportadora de los símbolos OFDM es acorde con un estándar de Difusión de Video Digital tal como el estándar de Difusión de Video Digital - Terrestre, el estándar de Difusión de Video Digital - Portátil, el estándar de Difusión de Video Digital - Terrestre 2 o el estándar de Difusión de Video Digital - Cable 2.

Patentes similares o relacionadas:

Método y aparato para la transmisión inalámbrica de datos sujetos a bloqueos de señal periódicos, del 6 de Mayo de 2020, de Hughes Network Systems, LLC: Un método, que comprende: segmentar (S311, S321, S331) un flujo de datos en paquetes de un tamaño fijo para una transmisión en modo ráfaga a través de […]

Método y aparato para la transmisión inalámbrica de datos sujeta a bloqueos de señal periódicos, del 23 de Octubre de 2019, de Hughes Network Systems, LLC: Un método para la transmisión inalámbrica de una primera corriente de datos, estando la transmisión sujeta a bloqueos periódicos, el método que comprende: segmentar una […]

Aparato y método de procesamiento de datos, del 25 de Septiembre de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos operable para mapear símbolos de datos recibidos de un número predeterminado de señales de subportadoras de símbolos […]

Aparato y método de procesamiento de datos, del 25 de Septiembre de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos operable para mapear símbolos de datos recibidos de un número predeterminado de señales de subportadoras de símbolos […]

Intercalador de bits para un sistema de BICM con códigos de QC-LDPC, del 3 de Julio de 2019, de PANASONIC CORPORATION: Un procedimiento de intercalación de bits para intercalar bits de una palabra de código generada en base a un esquema de codificación de comprobación de paridad de baja densidad […]

Aparato y método de procesamiento de datos, del 8 de Mayo de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos para mapear símbolos recibidos desde un número predeterminado de señales de subportadoras de un símbolo multiplexado por división ortogonal […]

Intercalador de bits para un sistema de BICM con códigos QC LDPC, del 6 de Marzo de 2019, de PANASONIC CORPORATION: Un procedimiento de entrelazado de bits para entrelazar bits de una palabra de código generada basándose en un esquema de codificación de verificación de paridad de baja densidad […]

Entrelazador de bits para un sistema BICM con códigos QC LDPC, del 28 de Febrero de 2019, de PANASONIC CORPORATION: Un método de entrelazado de bits para entrelazar bits de una palabra de código generada en base a un esquema de codificación con comprobación de paridad de baja densidad […]

Método de codificación del código polar y dispositivo de codificación, del 27 de Febrero de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación del código polar, caracterizado por comprender: asignar M bits reservados de una señalización de difusión a M bits […]