Señalización de los parámetros de la memoria intermedia indicativos de una arquitectura de memoria intermedia del receptor.

Un procedimiento para la señalización de los parámetros de la memoria intermedia,

que comprende: el envío (40) de los parámetros de la memoria intermedia desde un terminal (12) a un servidor (14), en el que dichos parámetros de la memoria intermedia se relacionan al menos con dos memorias intermedias de N memorias intermedias del terminal (16-1, 16-2, ... 16-N), y N es un número entero de al menos un valor de dos para la determinación (44) de un estado de al menos las dos memorias intermedias usando los parámetros de la memoria intermedia caracterizado porque dichos parámetros de la memoria intermedia comprenden al menos un índice del mecanismo de transferencia de la memoria intermedia para indicar un mecanismo de transferencia entre al menos las dos memorias intermedias.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/IB2006/000131.

Solicitante: NOKIA CORPORATION.

Nacionalidad solicitante: Finlandia.

Dirección: KEILALAHDENTIE 4 02150 ESPOO FINLANDIA.

Inventor/es: HANNUKSELA, MISKA, CURCIO,IGOR DANILO DIEGO, WANG,Ru-Shang.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04L12/56

- H04L29/06 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 29/00 Disposiciones, aparatos, circuitos o sistemas no cubiertos por uno solo de los grupos H04L 1/00 - H04L 27/00. › caracterizadas por un protocolo.

- H04N7/26

PDF original: ES-2381855_T3.pdf

Fragmento de la descripción:

Señalización de los parámetros de la memoria intermedia indicativos de una arquitectura de memoria intermedia del receptor Campo de la invención La presente invención se refiere a las comunicaciones multimedia y más específicamente a la señalización de los parámetros de la memoria intermedia indicativos del estado de la memoria intermedia del receptor.

Antecedente de la técnica Durante la reunión de la DLNA (Digital Living Network Alliance) RTP-TF (Real Time Protocol-Task Force) F2F (Face to Face) , celebrada el 26 de enero de 2005, se identificaron problemas al discutir los esquemas para la adaptación de la velocidad de bits. La conclusión fue que podría ser necesario considerar los diferentes modelos de memoria intermedia del receptor a fin de que la retroalimentación de recepción tenga sentido para el remitente, y para que el remitente lleve a cabo una adaptación eficiente.

Se proporciona la técnica anterior sobre este tema, por ejemplo, en lo que respecta al esquema de adaptación de la velocidad especificada para la transmisión en el 3GPP (3d Generation Partnership Project - Proyecto de Asociación de 3ª Generación ) y en el 3GPP2 (3d Generation Partnership Project 2 - Proyecto 2 de Asociación de 3ª Generación) de especificaciones tal como se describe en la especificación técnica 26.234 v.6.2.0 "Transparent Endto-end Packet Switched Streaming Service (PSS) Protocols and Codecs", y en la Especificación Técnica C.P0046

v.0.1.7 "3G Multimedia Streaming Services".

El modelo de memoria intermedia actual definido en los proyectos 3GPP/3GPP2 es una única memoria intermedia, y contiene una cabecera de RTP (Real Time Protocol - Protocolo en Tiempo Real) y una carga útil. Con el fin de soportar los diferentes modelos de memoria intermedia, (por ejemplo, los que contienen más de una memoria intermedia) los actuales esquemas de señalización de la técnica anterior no son suficientes para garantizar una solución factible y eficaz, por ejemplo, para la adaptación de la velocidad adecuada.

Una publicación "3G Multimedia Streaming Service, 3rd Generation Partnership Project 2, 3GPP2 Specifications, vol. TSG-C, no. WG 1, C.P0046, 10 de diciembre de 2004, páginas 1-50, Kauai, HI, USA, XP002650116" por Keith Miller desvela parámetros de la memoria intermedia que comprenden información sobre el tamaño de la memoria intermedia.

De manera similar, una publicación "3rd Generation Partnership Project; Technical Specification Group Service and System Aspects; Transparent end-to-end Packet-switched Streaming Service (PSS) ; Protocols and codecs (Release 6) , 3GPP STANDARD; 3GPP TS 26.234, 3RD GENERATION PARTNERSHIP PROJECT (3GPP) , MOBILE COMPETENCE CENTRE; 650, ROUTE DES LUCIOLES; F-06921 SOPHIA-ANTIPOLIS CEDEX; FRANCIA, no. V6.2.0, 1 de diciembre de 2004, páginas 1-124, XP050370103" desvela parámetros de la memoria intermedia en relación con el tamaño de la memoria intermedia.

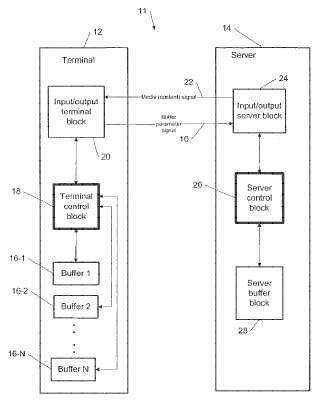

Las figuras 1-3 muestran diversas arquitecturas de memoria intermedia que se pueden emplear de acuerdo con la técnica anterior.

Divulgación de la invención Se presentan un nuevo procedimiento, un sistema, un aparato y un producto de software para la señalización de parámetros de las memorias intermedias múltiples por un terminal para un servidor y la determinación del estado de la memoria intermedia múltiple del terminal por el servidor que usa estos parámetros, por ejemplo, para una adaptación de velocidad adecuada de los servicios de transmisión multimedia proporcionados por el servidor al terminal.

De acuerdo con un primer aspecto de la invención, un procedimiento para la señalización de los parámetros de la memoria intermedia, comprende las etapas de: el envío de los parámetros de la memoria intermedia desde un terminal a un servidor, en el que los parámetros de la memoria intermedia se refieren al menos a dos memorias intermedias del terminal de N, y N es un número entero de al menos un valor de dos; la recepción de los parámetros de la memoria intermedia desde el terminal al servidor; y la determinación de un estado de al menos las dos memorias intermedias por el servidor usando los parámetros de la memoria intermedia, en el que los parámetros de la memoria intermedia comprenden al menos un índice del mecanismo de transferencia de la memoria intermedia para indicar un mecanismo de transferencia entre al menos las dos memorias intermedias.

De acuerdo además con el primer aspecto de la invención, los parámetros de la memoria intermedia pueden comprender al menos uno de: a) un número de al menos las dos memorias intermedias, b) los tamaños de la memoria intermedia de al menos las dos memorias intermedias, c) las unidades de tamaño de la memoria intermedia de al menos las dos memorias intermedias; d) un tamaño de cabecera parcial al menos en las dos memorias intermedias. Además, los parámetros de la memoria intermedia pueden comprender adicionalmente una unidad de retraso de difusión, para modificar una unidad de tiempo.

Además, de acuerdo con el primer aspecto de la invención, los parámetros de la memoria intermedia pueden comprender: un indicador de la memoria intermedia previa al decodificador de video; y un indicador de la memoria intermedia posterior al decodificador de video.

Aún más de acuerdo con el primer aspecto de la invención, al menos las dos memorias intermedias pueden estar fuera de: a) una memoria intermedia de oscilación, b) una memoria intermedia previa al decodificador, y c) una memoria intermedia posterior al decodificador.

De acuerdo además con el primer aspecto de la invención, al menos las dos memorias intermedias pueden comprender todas las N memorias intermedias del terminal.

De acuerdo con un segundo aspecto de la invención, un producto de programa de ordenador comprende: una estructura de almacenamiento legible por ordenador que contiene en ella el código del programa de ordenador para su ejecución por un procesador del ordenador con el código del programa de ordenador caracterizado por que incluye las instrucciones para llevar a cabo las etapas del primer aspecto de la invención, indicado para realizarse por cualquier componente o una combinación de los componentes del terminal o del servidor.

De acuerdo con un tercer aspecto de la invención, un sistema de comunicación, que se comprende de: un terminal, para proporcionar y enviar los parámetros de la memoria intermedia, en el que los parámetros de la memoria intermedia se relacionan al menos con dos memorias intermedias de las N memorias intermedias del terminal del terminal, en el que N es un número entero de al menos un valor de dos; y un servidor, para la recepción de los parámetros de la memoria intermedia desde el terminal y para determinar un estado de al menos las dos memorias intermedias usando los parámetros de la memoria intermedia, en el que los parámetros de la memoria intermedia comprenden al menos un índice del mecanismo de transferencia de la memoria intermedia para indicar un mecanismo de transferencia entre al menos las dos memorias intermedias.

De acuerdo además con el tercer aspecto de la invención, los parámetros de la memoria intermedia pueden comprender al menos uno de: a) un número de al menos las dos memorias intermedias, b) los tamaños de la memoria intermedia de al menos las dos memorias intermedias, c) las unidades de tamaño de la memoria intermedia de al menos las dos memorias intermedias d) un tamaño de cabecera parcial en al menos las dos memorias intermedias. Además, los parámetros de la memoria intermedia pueden comprender adicionalmente una unidad de retraso de difusión, para modificar una unidad de tiempo.

De acuerdo además con el tercer aspecto de la invención, los parámetros de la memoria intermedia pueden comprender: un indicador de la memoria intermedia anterior al decodificador de video; y un indicador de la memoria intermedia posterior al decodificador de video.

Además, de acuerdo con el tercer aspecto de la invención, al menos dos memorias intermedias pueden estar fuera de: a) una memoria intermedia de oscilación, b) una memoria intermedia previa al decodificador, y c) una memoria intermedia posterior al decodificador.

Además, de acuerdo con el tercer aspecto de la invención, al menos las dos memorias intermedias pueden comprender todas las N memorias intermedias del terminal.

De acuerdo con un cuarto aspecto de la invención, un terminal, comprende: N memorias intermedias del terminal, en el que N es un número entero de al... [Seguir leyendo]

Reivindicaciones:

1. Un procedimiento para la señalización de los parámetros de la memoria intermedia, que comprende:

el envío (40) de los parámetros de la memoria intermedia desde un terminal (12) a un servidor (14) , en el que dichos parámetros de la memoria intermedia se relacionan al menos con dos memorias intermedias de N

memorias intermedias del terminal (16-1, 16-2, ... 16-N) , y N es un número entero de al menos un valor de dos para la determinación (44) de un estado de al menos las dos memorias intermedias usando los parámetros de la memoria intermedia caracterizado porque dichos parámetros de la memoria intermedia comprenden al menos un índice del mecanismo de transferencia de la memoria intermedia para indicar un mecanismo de transferencia entre al menos las dos memorias intermedias.

2. Un procedimiento para la señalización de los parámetros de la memoria intermedia, que comprende:

la recepción (42) de los parámetros de la memoria intermedia, en el que dichos parámetros de la memoria intermedia se relacionan al menos con dos de las memorias intermedias de N memorias intermedias (16-1, 162, ... 16-N) del terminal, y N es un número entero de al menos un valor de dos, y la determinación (44) de un estado de al menos las dos memorias intermedias usando los parámetros de la memoria intermedia, caracterizado porque dichos parámetros de la memoria intermedia comprenden al menos un índice del mecanismo de transferencia de la memoria intermedia para indicar un mecanismo de transferencia entre al menos las dos memorias intermedias.

3. Un procedimiento de acuerdo con la reivindicación 1 o 2, caracterizado porque los parámetros de la memoria 20 intermedia comprenden además al menos uno de:

un número de al menos las dos memorias intermedias; los tamaños de la memoria intermedia de al menos las dos memorias intermedias; las unidades de tamaño de la memoria intermedia de al menos las dos memorias intermedias, y un tamaño de la cabecera parcial en al menos las dos memorias intermedias.

4. Un procedimiento de acuerdo con la reivindicación 3, caracterizado porque los parámetros de la memoria intermedia comprenden además una unidad de retraso de difusión, para modificar una unidad de tiempo.

5. Un procedimiento de acuerdo con cualquier reivindicación precedente, caracterizado porque los parámetros de la memoria intermedia comprenden:

un indicador de la memoria intermedia anterior al decodificador de video; y 30 un indicador de la memoria intermedia posterior al decodificador de video.

6. Un procedimiento de acuerdo con cualquier reivindicación precedente, caracterizado porque al menos las dos memorias intermedias están fuera de:

una memoria intermedia de des- oscilación; una memoria intermedia anterior al decodificador, y 35 una memoria intermedia posterior al decodificador.

7. Un procedimiento de acuerdo con cualquier reivindicación precedente, caracterizado porque al menos las dos memorias intermedias comprenden todas las N memorias intermedias (16-1, 16-2, ... 16-N) del terminal.

8. Un producto de programa de ordenador que comprende: una estructura de almacenamiento legible por ordenador que contiene en su interior el código del programa de ordenador para su ejecución por un procesador del ordenador

con dicho código del programa de ordenador, en el que dicho código del programa de ordenador comprende instrucciones para realizar un procedimiento de la reivindicación 1.

9. Un terminal (12) que comprende N memorias intermedias (16-1, 16-2, ... 16-N) del terminal, en el que N es un número entero de al menos un valor de dos;

45 un bloque de control del terminal (18) configurado para proporcionar los parámetros de la memoria intermedia relacionados al menos con dos memorias intermedias de las N memorias intermedias del terminal; y un bloque del terminal de entrada/salida (20) configurado para enviar los parámetros de la memoria intermedia del terminal (12) a un servidor (14) , para determinar un estado de al menos las dos memorias intermedias por el servidor (14) usando los parámetros de la memoria intermedia, caracterizado porque dichos parámetros de la memoria 50 intermedia comprenden al menos un índice del mecanismo de transferencia de la memoria intermedia para indicar un mecanismo de transferencia entre al menos las dos memorias intermedias.

10. Un terminal (12) de acuerdo con la reivindicación 9, caracterizado porque los parámetros de la memoria intermedia comprenden al menos uno de:

un número de al menos las dos memorias intermedias; los tamaños de la memoria intermedia de al menos las dos memorias intermedias; las unidades de tamaño de la memoria intermedia de al menos las dos memorias intermedias, y un tamaño de la cabecera parcial al menos en las dos memorias intermedias.

11. Un terminal (12) de acuerdo con la reivindicación 10, caracterizado porque los parámetros de la memoria intermedia comprenden además una unidad de retraso de difusión, para modificar una unidad de tiempo.

12. Un terminal (12) de acuerdo con la reivindicación 9 o 10, caracterizado porque los parámetros de la memoria intermedia comprenden:

un indicador de la memoria intermedia anterior al decodificador de video; y un indicador de la memoria intermedia posterior al decodificador de video.

13. Un terminal (12) de acuerdo con una cualquiera de las reivindicaciones 9 a 12, caracterizado porque al menos las dos memorias intermedias están fuera de:

una memoria intermedia de des-oscilación; una memoria intermedia anterior al decodificador, y una memoria intermedia posterior al decodificador.

14. Un terminal (12) de acuerdo con una cualquiera de las reivindicaciones 9 a 13, caracterizado porque al menos las dos memorias intermedias comprenden todas las N memorias intermedias (16-1, 16-2, ... 16-N) del terminal.

15. Un terminal (12) de acuerdo con una cualquiera de las reivindicaciones 9 a 14, caracterizado porque dicho terminal (12) es un dispositivo de comunicación para comunicaciones inalámbricas.

16. Un terminal (12) de acuerdo con la reivindicación 9, caracterizado porque se combinan el bloque del terminal de entrada/salida (20) y el bloque del terminal de entrada/salida (20) .

17. Un servidor (14) , que comprende:

un bloque de entrada/salida (24) configurado para recibir los parámetros de la memoria intermedia desde un terminal (12) , en el que dichos parámetros de la memoria intermedia se refieren al menos a dos memorias intermedias de las N memorias intermedias (16-1, 16-2, ... 16-N) del terminal del terminal (12) , en el que N es un número entero de al menos un valor de dos, y un bloque de control del servidor (26) configurado para determinar un estado de al menos las dos memorias intermedias usando los parámetros de la memoria intermedia, caracterizado porque dichos parámetros de la memoria intermedia comprenden al menos un índice del mecanismo de transferencia de la memoria intermedia para indicar un mecanismo de transferencia entre al menos las dos memorias intermedias.

18. Un servidor (14) de acuerdo con la reivindicación 17, caracterizado porque el bloque de control del servidor

(26) está configurado además para adaptar una velocidad de transmisión de acuerdo con dicho estado y usando un criterio predeterminado, y en el que el bloque de entrada/salida (24) está configurado además para enviar el contenido de los medios desde el servidor (14) al terminal (12) usando dicha velocidad de transmisión adaptada.

19. Un sistema de comunicación (11) que comprende:

un terminal (12) de acuerdo con una cualquiera de las reivindicaciones 9 a 16, y un servidor (14) de acuerdo con una cualquiera de las reivindicaciones 17 a 18.

Patentes similares o relacionadas:

Dispositivo inalámbrico y procedimiento para visualizar un mensaje, del 25 de Marzo de 2020, de QUALCOMM INCORPORATED: Un dispositivo inalámbrico para visualizar un mensaje, comprendiendo el dispositivo inalámbrico: un visualizador gráfico ; una unidad de comunicaciones inalámbricas […]

Método de indicación de disponibilidad de servicio para terminales de radiofrecuencia de corto alcance, con visualización de icono de servicio, del 26 de Febrero de 2020, de Nokia Technologies OY: Un método que comprende: recibir, en un dispositivo , información de icono de un dispositivo de origen en conexión con descubrimiento de dispositivo […]

Procedimiento y aparato para la transmisión de entramado con integridad en un sistema de comunicación inalámbrica, del 6 de Noviembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el entramado de paquetes en un sistema de transmisión inalámbrico que admite transmisiones de radiodifusión, el procedimiento que comprende: […]

Aparato y procedimiento para usar en la realización de peticiones de repetición automática en sistemas de comunicaciones de acceso múltiple inalámbricas, del 6 de Noviembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para usar en un sistema de comunicaciones inalámbricas que comprende al menos una estación base y al menos dos terminales inalámbricos […]

Procedimiento y aparato para sistemas inalámbricos de activación, del 31 de Octubre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para controlar de forma inalámbrica una tarjeta de interfaz de red NIC (108 A-N) usando una red inalámbrica , con la NIC (108 A-N) […]

Procedimiento y aparato para sistemas inalámbricos de activación, del 31 de Octubre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para controlar de forma inalámbrica una tarjeta de interfaz de red NIC (108 A-N) usando una red inalámbrica , con la NIC (108 A-N) […]

Método y sistema para visualizar un nivel de confianza de las operaciones de comunicación de red y la conexión de servidores, del 16 de Octubre de 2019, de Nokia Technologies OY: Un método que comprende: recibir, en un servidor , una primera solicitud para un análisis de una primera operación de comunicación desde […]

Un protocolo de red agile para comunicaciones seguras con disponibilidad asegurada de sistema, del 11 de Septiembre de 2019, de VirnetX Inc: Un método para un primer nodo para establecer una sesión con un segundo nodo , el método se realiza en el primer nodo , en el que […]

Dispositivo de nodo para una red de sensores inalámbricos, del 10 de Julio de 2019, de Wirepas Oy: Un dispositivo de nodo para una red de sensores inalámbricos, comprendiendo el dispositivo de nodo: - un transceptor […]