RESISTENCIA LINEAL INTEGRADA CON COMPENSACIÓN DE TEMPERATURA.

Resistencia lineal integrada con compensación de temperatura.

Permite proporcionar una resistencia cuya resistividad es esencialmente constante ante cambios de temperatura,

aportando una solución efectiva, sencilla, compacta y completamente compatible con la tecnología CMOS. Dicha resistencia lineal integrada destaca fundamentalmente por comprender una red MRC; y un primer circuito de control que comprende un espejo de corriente formado por dos transistores MOS (M31, M41) polarizados por una fuente de intensidad (IB1) independiente de la temperatura y que comprende un ramal con dos resistencias (RA1, RB1) en serie cuyo terminal está conectado a un primer grupo de puertas (G1) de la red MRC; y donde el valor de las dos resistencias (RA1, RB1) es tal que la variación de R1 = RA1 + RB1 compensa las desviaciones provocadas por la temperatura en RMRC.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201030916.

Solicitante: UNIVERSIDAD DE ZARAGOZA..

Nacionalidad solicitante: España.

Inventor/es: CELMA PUEYO,SANTIAGO, CALVO LOPEZ,BELEN, VALERO BERNAL,MARÍA DE RODANAS, MEDRANO MARQUÉS,NICOLÁS J.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G05F1/46 FISICA. › G05 CONTROL; REGULACION. › G05F SISTEMAS DE REGULACION DE VARIABLES ELECTRICAS O MAGNETICAS (regulación de la distribución en el tiempo o de la periodicidad de impulsos en los sistemas de radar o de radionavegación G01S; regulación de la corriente o de la tensión, especialmente adaptada para su uso en relojes electrónicos G04G 19/02; sistemas que funcionan en bucle cerrado para regular variables no eléctricas por medios eléctricos G05D; control de la alimentación de energía eléctrica a los computadores digitales G06F 1/26; para obtener las características de funcionamiento deseadas de electroimanes con armadura H01F 7/18; regulación de redes de distribución de energía eléctrica H02J; regulación de la carga de baterías H02J 7/00; regulación del valor de salida de convertidores estáticos, p. ej. reguladores de conmutación, H02M; regulación del valor de salida de generadores eléctricos H02N, H02P 9/00; control de transformadores, reactancias o bobinas de choque H02P 13/00; regulación de la respuesta de frecuencia, ganancia, potencia de salida máxima, amplitud o ancho de banda de amplificadores H03G; regulación de la sintonización de circuitos resonantes H03J; control de generadores de oscilaciones o de impulsos electrónicos H03L; regulación de las características de líneas de transmisión H04B; control de fuentes eléctricas de luz H05B 39/04, H05B 41/36, H05B 45/10, H05B 45/20, H05B 47/10; control eléctrico de aparatos de rayos X H05G 1/30). › G05F 1/00 Sistemas automáticos en los que las desviaciones de una magnitud eléctrica en relación a uno o a varios valores predeterminados son detectadas a la salida y reintroducidas en un dispositivo interior al sistema para llevar el valor detectado a su valor o a sus valores predeterminados, es decir, sistemas retroactivos. › en donde la variable efectivamente regulada por el dispositivo de regulación final es continua (G05F 1/625 tiene prioridad).

Fragmento de la descripción:

RESISTENCIA LINEAL INTEGRADA CON COMPENSACION DE TEMPERATURA

OBJETIVO DE LA INVENCION

La presente invencion se engloba dentro del campo de los sistemas microelectronicos, y mas concretamente en los sistemas de procesado y tratamiento de senales electricas analogicas realizados en tecnologfa CMOS que precisan de resistencias lineales con baja dependencia termica. Concretamente, el objeto de la presente invencion es proporcionar una resistencia cuya resistividad sea esencialmente constante ante cambios de temperatura. ANTECEDENTES DE LA INVENCION

Los parametros caracterfsticos de muchos circuitos analogicos estan directamente relacionados con sus componentes pasivos, tanto resistivos como capacitivos. Por ejemplo, la ganancia de un amplificador puede estar determinada por cocientes de resistencias y/o capacidades, mientras que las frecuencias crfticas de un filtro vienen dadas por productos RC. Por ese motivo, es extremadamente importante seleccionar resistencias adecuadas a cada aplicacion, normalmente en funcion de factores como la linealidad, el area, la complejidad del circuito de polarizacion o la variacion de la resistencia con la temperatura.

En procesos CMOS estandares, las resistencias mas ideales son simples tiras de polisilicio. Sin embargo, la resistencia específica o por cuadro es pequena incluso en el caso de polisilicio de alta resistividad. Otro inconveniente conocido es que con frecuencia se producen desviaciones de la resistencia de hasta un 20% respecto al valor esperado debido a variaciones en el proceso y a los elevados coeficientes de temperatura. Adicionalmente, hay que anadir a esto el efecto del envejecimiento de los circuitos. Sin embargo, el mayor inconveniente tanto de las resistencias pasivas integradas, como resistencias de polisilicio, resistencias de pozo N o P es que son extremadamente sensibles a las variaciones en la temperatura, a lo que se suma la relativamente elevada area de silicio requerida para su implementacion si su correspondiente valor resistivo es elevado Otra opcion es el uso de transistores MOS como elemento resistivo, lo cual no solo implica un considerable ahorro de area, sino que ademas posibilita el control directo del valor de la resistencia a traves de la tension de puerta del transistor. Siempre que los parametros de un circuito sean funcion del valor de una resistencia es posible implementar un ajuste fino de los mismos mediante el uso de transistores MOS en zona ohmica. Aunque el empleo de transistores MOS soluciona el problema del area de silicio requerido por las resistencias pasivas integradas, los transistores MOS distan de ser inmunes a las fluctuaciones de temperatura. Ademas, otro de los inconvenientes del empleo de transistores MOS como resistencias es la limitacion del rango dinamico, ya que los transistores presentan, incluso en esta region de operacion, una caracterfstica de salida altamente no lineal.

El circuito MOS resistivo, o MRC, que se muestra en la Fig. 1a, es una solucion estandar a estos problemas de no linealidad. Bajo unas determinadas condiciones de polarizacion y para un rango de permitido de tensiones de entrada (V1 y V2) , este circuito se comporta como una resistencia altamente lineal (vease la Fig. 1b) cuya magnitud es controlable a traves de la diferencia de unas tensiones de control VG1, VG2, como describe Zdzislaw Czarnul en "Novel MOS Resistive Circuit for Synthesis of Fully Integrated Continous - Time Filters", IEEE Trans. Circuit Syst., vol. CAS - 33, nQ. 7, pp. 718 - 721, Julio 1986) .

La caracterfstica de este circuito, supuesto que los transistores MOS trabajan en inversion fuerte y en la zona de triodo esta descrita por:

(1)

donde es la movilidad de los portadores en el canal del transistor, Cox es la capacidad del oxido de puerta por unidad de area, VG1-VG2 la diferencia de tensiones de puerta aplicadas a los transistores y V1-V2 la diferencia de tensiones de entrada. Reordenando esta ecuacion se obtiene:

donde Es decir, la resistencia diferencial RMRC de la red MRC es inversamente proporcional a la movilidad , la cual introduce la principal dependencia del valor resistivo con la temperatura, como se observa en la Fig. 1c.

Asf pues, serfa deseable proporcionar una resistencia activa compensada termicamente que no solamente sea economica en terminos de area de silicio, sino que ademas presente una elevada linealidad y su valor sea controlable e independiente de las variaciones de la temperatura.

DESCRIPCION DE LA INVENCION

La presente invencion propone una solucion efectiva, sencilla, compacta y completamente compatible con la tecnologfa CMOS. La resistencia lineal integrada que se propone esta formada por una red MRC cuyas variaciones con la temperatura se compensan empleando al menos un circuito de control. Aunque las topologfas definidas en esta solicitud estan implementadas utilizando transistores PMOS, se entiende que serfa posible tambien implementarlos utilizando transistores NMOS.

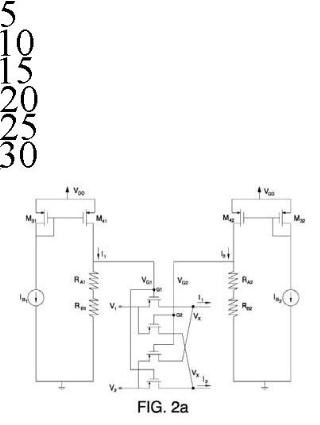

A continuacion se describen con mayor detalle las partes que componen la resistencia lineal integrada con compensacion de temperatura de la invencion, cuya implementacion con dos circuitos de control se muestra en la Fig. 2a:

a) Red MRC

En el presente documento, el termino "red MRC" hace referencia al circuito conocido en la tecnica que se describio anteriormente y que se representa en la Fig. 1a, formado por cuatro transistores identicos trabajando en triodo cuyas puertas estan conectadas dos a dos y cuyos terminales de canal se cruzan.

b) Circuito de control El circuito de control de la presente invencion tiene dos funciones principales:

- Proporcionar los niveles de tension VGi que fijan el valor resistivo RMRC deseado segun la formula (3) anterior.

- Compensar las variaciones termicas de RMRC por medio de valores adecuados de los voltajes VGi con el objeto de obtener una RMRC esencialmente constante con la temperatura.

Para ello, el circuito de control comprende un espejo de corriente MOS dotado de una fuente de intensidad (IBi) independiente de la temperatura, configurado para copiar en una rama de salida, dotada de un par de resistencias (RAi, RBi) , una intensidad proporcional a dicha intensidad (IBi) , obteniendose como resultado los voltajes VGi del circuito MRC. Con esta topologfa, una adecuada eleccion de las resistencias (RAi, RBi) permite obtener voltajes VGi cuya variacion con la temperatura compensa los cambios en RMRC, dando como resultado una resistencia constante.

Las resistencias (RAi, RBi) se implementan de modo que cada par de resistencias (RAi, RBi) en serie tenga unos coeficientes termicos tales que la variacion de Ri = RAi + RBi compense las desviaciones provocadas por la temperatura en RMRC. Es decir, si RAi y RBi son resistencias con diferentes coeficientes termicos TCAi y TCBi, es posible combinarlas para obtener una resistencia serie equivalente Ri = RAi+RBi con un coeficiente termico TCi dado por:

( )

donde =RAi/RBi es el cociente entre los valores resistivos de RAi y RBi La Fig. 2b muestra la variacion de la intensidad diferencial I1-I2 con la temperatura de la resistencia lineal integrada de la invencion formada por el circuito RMC mas los circuitos de control. Se aprecia que las desviaciones de la resistencia estan por debajo del 0, 3%, en contraste con las desviaciones del 32% del circuito RMC sin compensacion que se aprecian en la Fig. 1c.

BREVE DESCRIPCION DE LAS FIGURAS

La Fig. 1a muestra un circuito MRC segun la tecnica anterior.

La Fig. 1b muestra la caracterfstica V-I del circuito MRC de la Fig. 1a.

La Fig. 1c muestra la variacion de la resistencia RMRC del circuito MRC de la Fig. 1a en funcion de la temperatura.

La Fig. 2a muestra una realizacion preferida de la resistencia lineal integrada de la invencion.

La Fig. 2b muestra la variacion de la resistencia del circuito de la Fig. 2a en funcion de la temperatura.

La Fig. 3 muestra un ejemplo de resistencia lineal integrada segun la invencion que comprende un unico circuito de control.

La Fig. muestra otro ejemplo de resistencia lineal integrada segun la invencion.

REALIºACION PREFERIDA DE LA INVENCION

Como puede deducirse de (3) , utilizando la configuracion con dos circuitos de control mostrada en la Fig. 2 es posible hacer...

Reivindicaciones:

REIVINDICACIONESï

1. Resistencia lineal integrada con compensación de temperatura caracterizada porque comprende:

- una red MRC; y

- un primer circuito de control que comprende un espejo de corriente formado por dos transistores MOS (M31, M41) polarizados por una fuente de intensidad (IB1) independiente de la temperatura y que comprende un ramal con dos resistencias (RA1, RB1) en serie cuyo terminal esta conectado a un primer grupo de puertas (G1) de la red MRC,

y donde el valor de las dos resistencias (RA1, RB1) es tal que la variación de R1 = RA1 + RB1 compensa las desviaciones provocadas por la temperatura en RMRC.

2. Resistencia lineal integrada segun la reivindicación 1, donde el segundo grupo de puertas (G2) esta conectado a un segundo circuito de control igual que el primero, pudiendo así obtenerse una RMRC tanto positiva o como negativa.

3. Resistencia lineal integrada segun la reivindicación 1, donde el segundo grupo de puertas (G2) esta conectado a un nodo de referencia (Vref) , pudiendo así obtenerse una RMRC bien positiva o bien negativa.

4. Resistencia lineal integrada segun la reivindicación 1, donde el espejo de corriente del primer circuito de control esta conectado a dos transistores MOS (M1, M2) , los cuales estan a su vez conectados al primer (VG1) y al segundo (VG2) grupos de puertas, y que ademas comprende un ramal con dos resistencias (RA2, RB2) conectado a dicho segundo grupo de puertas (VG2) .

5. Resistencia lineal integrada segun cualquiera de las reivindicaciones anteriores, donde los transistores MOS se eligen entre transistores PMOS y transistores NMOS.

OFICINA ESPAÑOLA DE PATENTES Y MARCAS

Nº solicitud: 201030916

ESPAÑA

Fecha de presentación de la solicitud: 14.06.2010

Fecha de prioridad:

INFORME SOBRE EL ESTADO DE LA TECNICA

51 Int. Cl. : G05F1/46 (2006.01)

DOCUMENTOS RELEVANTES

Categoría 56 Documentos citados Reivindicaciones afectadas Y US 6650176 B1 (LORENZ PERRY S) 18.11.2003, todo el documento. 1-5 Y CZARNUL, Z.; "Novel MOS Resistive Circuit for Synthesis of Fully Integrated Continuous-Time Filters, " Circuits and Systems, IEEE Transactions on, vol. 33, no. 7, pp.71. 721, Jul 1986; doi: 10.1109/TCS.1986.1085974 1-5 A US 6348832 B1 (CHIH YUE-DER) 19.02.2002, todo el documento. 1-5 Y US 2006125462 A1 (ECKSTEIN WOLFGANG) 15.06.2006, todo el documento. 1-5 Y TAKAGI et al., "Generalized MRC [MOS Resistive Circuit], " Circuits and Systems, 1997. ISCAS '97., Proceedings of 1997 IEEE International Symposium on, vol. 1, pp.

22. 224 vol.1, 9-12 Jun 1997; doi: 10.1109/ISCAS.1997.608677 1-5 A FR 2832819 A1 (ST MICROELECTRONICS SA) 30.05.2003, páginas 11-13; figuras. A US 2006197585 A1 (KIM HYOUNGRAE et al.) 07.09.2006, descripción; figuras. 1-5 Categoría de los documentos citados X: de particular relevancia Y: de particular relevancia combinado con otro/s de la misma categoría A: refleja el estado de la técnica O: referido a divulgación no escrita P: publicado entre la fecha de prioridad y la de presentación de la solicitud E: documento anterior, pero publicado después de la fecha de presentación de la solicitud El presente informe ha sido realizado • para todas las reivindicaciones • para las reivindicaciones nº : Fecha de realización del informe 12.03.2012 Examinador M. P. López Sábater Página 1/4

INFORME DEL ESTADO DE LA TÉCNICA

Nº de solicitud: 201030916

Documentación mínima buscada (sistema de clasificación seguido de los símbolos de clasificación) G05F Bases de datos electrónicas consultadas durante la búsqueda (nombre de la base de datos y, si es posible, términos de búsqueda utilizados) INVENES, EPODOC

Informe del Estado de la Técnica Página 2/4

OPINIÓN ESCRITA

Nº de solicitud: 201030916

Fecha de Realización de la Opinión Escrita: 12.03.2012

Declaración

Novedad (Art. 6.1 LP 11/1986) Reivindicaciones Reivindicaciones 1-5 SI NO Actividad inventiva (Art. 8.1 LP11/1986) Reivindicaciones Reivindicaciones 1-5 SI NOSe considera que la solicitud cumple con el requisito de aplicación industrial. Este requisito fue evaluado durante la fase de examen formal y técnico de la solicitud (Artículo 31.2 Ley 11/1986) .

Base de la Opinión.

La presente opinión se ha realizado sobre la base de la solicitud de patente tal y como se publica.

Informe del Estado de la Técnica Página 3/4

OPINIÓN ESCRITA

Nº de solicitud: 201030916

1. Documentos considerados.

A continuación se relacionan los documentos pertenecientes al estado de la técnica tomados en consideración para la realización de esta opinión.

Documento Número Publicación o Identificación Fecha Publicación D01 US 6650176 B1 (LORENZ PERRY S) 18.11.2003 D02 CZARNUL, Z.; "Novel MOS Resistive Circuit for Synthesis of Fully Integrated Continuous-Time Filters, " Circuits and Systems, IEEE Transactions on, vol. 33, no.7, pp.71. 721, Jul 1986; doi: 10.1109/TCS.1986.1085974 D03 US 2006125462 A1 (ECKSTEIN WOLFGANG) 15.06.2006 D04 TAKAGI et al., "Generalized MRC [MOS Resistive Circuit], " Circuits and Systems, 1997. ISCAS '97., Proceedings of 1997 IEEE International Symposium on, vol. 1, pp.

22. 224 vol.1.

9. 12 Jun 1997; doi: 10.1109/ISCAS.1997.608677

2. Declaración motivada según los artículos 29.6 y 29.7 del Reglamento de ejecución de la Ley 11/1986, de 20 de marzo, de Patentes sobre la novedad y la actividad inventiva; citas y explicaciones en apoyo de esta declaración Reivindicación 1:

El documento del estado de la técnica anterior D01 presenta una red resistiva (R1 a R6) y un primer circuito de control que comprende un espejo de corriente (130) formado por dos transistores MOS (M31, M41) y un ramal con dos resistencias (R7, R8) . Además, el valor de las dos resistencias (R7, R8) es tal que la variación de la resistencia equivalente que forman compensa las desviaciones provocadas por la temperatura en las redes de resistencias posibles (R1-R4) y (R5, R6) . A diferencia del documento base, las distintas redes de resistencias que se contemplan no son del tipo MRC, pero para un experto en la materia interesado compensar las variaciones de temperatura de una red de este tipo sería inmediato sustituir la red resistiva (R1 a R6) de D01 por una red como la presentada en D02 aprovechando el funcionamiento del espejo de corriente y las resistencias de compensación sin que ello conlleve actividad inventiva según el artículo 8 de la Ley 11/86 de Patentes.

A la misma conclusión se llega con la combinación obvia de D03 y D04.

Reivindicaciones 2 a 5:

Estas reivindicaciones también ven su actividad inventiva afectada por la combinación obvia de los documentos D01 y D02, así como por la combinación de los documentos D03 y D04.

Informe del Estado de la Técnica Página 4/4

Patentes similares o relacionadas:

Dispositivo de generador de corriente y método de generación de una onda de corriente, del 26 de Febrero de 2020, de Prodit Engineering S.r.l: Dispositivo de generador de corriente que comprende una unidad de procesamiento que comprende: - un módulo de entrada diseñado para adquirir datos de […]

Circuito de alimentación eléctrica de espera para sistema de intercomunicación de bus de 2 hilos y su aparato, del 7 de Junio de 2019, de ABB SCHWEIZ AG: Un circuito de alimentación eléctrica de espera para un sistema de intercomunicación de bus de 2 hilos, en el que dicho circuito de alimentación eléctrica […]

Procedimiento y aparato de polarización y compensación de regulador de tensión de baja caída (LDO) con velocidad de encendido reducida, del 26 de Febrero de 2019, de QUALCOMM INCORPORATED: Un regulador de tensión de baja caída, LDO, con variación de tensión de encendido reducida, que comprende: una puerta de paso (M9) que acopla de forma ajustable, en respuesta […]

Ajuste a escala adaptativo de voltaje, del 18 de Abril de 2018, de QUALCOMM INCORPORATED: Un procedimiento para establecer un nivel de voltaje asociado a cada una de una o más frecuencias operativas, comprendiendo el procedimiento: aprender adaptativamente […]

Fuentes de corriente de baja fuga y circuitos activos, del 9 de Marzo de 2016, de QUALCOMM INCORPORATED: Un dispositivo, que comprende:

un primer transistor que puede funcionar para proporcionar una corriente de salida cuando está activado […]

Fuentes de corriente de baja fuga y circuitos activos, del 9 de Marzo de 2016, de QUALCOMM INCORPORATED: Un dispositivo, que comprende:

un primer transistor que puede funcionar para proporcionar una corriente de salida cuando está activado […]

Control de interregulador de múltiples fuentes de alimentación eléctrica, del 18 de Abril de 2012, de C.E. NIEHOFF & COMPANY: Un método para el control de las fuentes de potencia eléctrica en un sistema con al menos dos fuentes de potencia eléctrica que se conectan en paralelo, teniendo cada fuente […]

Control de interregulador de múltiples fuentes de alimentación eléctrica, del 18 de Abril de 2012, de C.E. NIEHOFF & COMPANY: Un método para el control de las fuentes de potencia eléctrica en un sistema con al menos dos fuentes de potencia eléctrica que se conectan en paralelo, teniendo cada fuente […]

FUENTE DE CORRIENTE DE SEGUIMIENTO BIPOLAR/COLECTOR CON CONEXION A TIERRA., del 1 de Noviembre de 2002, de PENBERTHY, INC.: UN SISTEMA PARA CONTROLAR UNA CORRIENTE CONSTANTE BIPOLAR CUANDO LA CORRIENTE ESTA SIENDO SUMINISTRADA A UN ELEMENTO ACTIVO O REACTIVO. EL RASTREO […]

DISPOSITIVO PARA UN CARGADOR DE BATERIA, del 25 de Noviembre de 2009, de CREATOR TEKNISK UTVECKLING AB: Dispositivo para reducir la corriente de salida de un cargador de batería primario conmutado, cuyo cargador comprende un circuito de potencia en […]

DISPOSITIVO PARA UN CARGADOR DE BATERIA, del 25 de Noviembre de 2009, de CREATOR TEKNISK UTVECKLING AB: Dispositivo para reducir la corriente de salida de un cargador de batería primario conmutado, cuyo cargador comprende un circuito de potencia en […]