COMPLEMENTO PARA SEÑALIZACION DE ERROR EN CIRCUITOS DE CONTROL DE POTENCIA.

1. Complemento para señalización de error en circuitos de control de potencia,

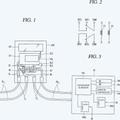

para aplicación en relación con un circuito de control de un dispositivo FET MOS (T1) de alimentación de una carga (R1), en el cual se incluye un termofusible (F1) de protección contra temperaturas excesivas, caracterizado porque comprende una red formada en torno a uno o más transistores adicionales conectados a los bornes del termofusible (F1) conectado en serie con el dispositivo FET MOS (T1) y la carga (R1), para cualquier posición del termofusible (F1) en dicho circuito serie, de tal manera que, al abrirse el termofusible (F1), dicha red fuerza a un terminal de control (V4) a adoptar una tensión tal que puede ser interpretada como una situación de error por una unidad de control exterior conectada al mencionado terminal de control (V4).

2. Complemento para señalización de error en circuitos de control de potencia, de acuerdo con la primera reivindicación, caracterizado porque comprende un transistor (Q3), el cual se conecte por su colector y su emisor, respectivamente, en relación con un terminal (V4) por el que se aplica una señal de control y en relación con un terminal (V3) de conexión del circuito de control del dispositivo FET MOS (T1), mientras que la base de dicho transistor (Q3) se conecta respecto de un punto intermedio entre el termofusible (F1) de protección y el dispositivo FET MOS (T1), en el circuito de control.

3. Complemento para señalización de error en circuitos de control de potencia, de acuerdo con la segunda reivindicación, caracterizado porque la conexión del colector del transistor (Q3) respecto del terminal (V4) de aplicación de la señal de control, se establece a través de una resistencia (R7).

4. Complemento para señalización de error en circuitos de control de potencia, de acuerdo con la segunda reivindicación, caracterizado porque la conexión de la base del transistor (Q3) respecto de un punto intermedio entre el termofusible (F1) y el dispositivo FET MOS (T1), se establece a través de una resistencia (R8).

Tipo: Modelo de Utilidad. Resumen de patente/invención. Número de Solicitud: U201101232.

Solicitante: ZERTAN, S.A..

Nacionalidad solicitante: España.

Inventor/es: DIEZ GARCIA,SERGIO, CREUS LLORENS,JAVIER, LANDATXE ZUGARRAMURDI,JOSE LUIS, ARTETA UNANUA,JAVIER.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G01R21/00 FISICA. › G01 METROLOGIA; ENSAYOS. › G01R MEDIDA DE VARIABLES ELECTRICAS; MEDIDA DE VARIABLES MAGNETICAS (indicación de la sintonización de circuitos resonantes H03J 3/12). › Disposiciones para proceder a las medidas de la potencia o del factor de potencia (G01R 7/12 tiene prioridad).

Fragmento de la descripción:

Complemento para señalización de error en circuitos de control de potencia.

Sector de la técnica

La presente invención está relacionada con la protección de circuitos de control de elementos eléctricos, tales como transistores de efecto campo metal-óxido semiconductores de potencia, proponiendo un complemento de dichos circuitos que permite señalizar anomalías de error en los mismos, para que puedan llevarse a cabo las medidas correctoras oportunas.

Estado de la técnica

Es cada vez más frecuente el uso de dispositivos de potencia para interrumpir o conectar, bajo las órdenes de una circuitería de control, la energía eléctrica suministrada a una carga. Las aplicaciones en tal sentido son muy numerosas, como control de ventiladores, cerraduras, inyectores y todo tipo de actuadores en general, así como válvulas, elementos de iluminación, elementos calefactores, etc.

Para esa función, los dispositivos de efecto campo metal-óxido semiconductor (FET MOS), presentan frente a los relés o interruptores electromagnéticos las ventajas siguientes:

- La relación volumen/capacidad de corte de potencia, es muy baja.

- Gran facilidad para integración sin solución de continuidad como partes de circuiterías de control y mando, permitiendo unos montajes ligeros y compactos, lo cual es muy importante, por ejemplo, en el campo de la automoción.

- Elevada fiabilidad bajo condiciones especificadas de funcionamiento, ya que apenas sufren desgaste.

- Gran resistencia a las vibraciones.

- Su costo es muy reducido en comparación con los dispositivos electromecánicos.

Dichos dispositivos presentan también, sin embargo, una serie de inconvenientes frente a los interruptores electromagnéticos, como por ejemplo:

- Suelen tener mayor caída de tensión y, por lo tanto, se calientan más al paso de la corriente eléctrica, necesitando estar provistos de medios de refrigeración.

- Presentan un margen más estrecho entre la corriente nominal y la máxima que provoca la destrucción del dispositivo, debiendo tomarse medidas para evitar los cortocircuitos.

- Son muy sensibles a las sobretensiones, de manera que impulsos de muy corta duración (< 1 segundo), de tensiones que apenas superan el doble de la tensión nominal de trabajo entre los terminales de conmutación (fuente y drenador), pueden causar un daño irreversible al dispositivo.

- Presentan una relación inversamente proporcional entre la corriente máxima que el dispositivo puede soportar en estado de cierre o conducción y la tensión máxima que puede soportar en estado de apertura o no conducción.

Todo ello cobra especial importancia en aplicaciones de automoción, ya que los sistemas alimentados a tensión nominal de 12 V, incluso en el manejo de potencias pequeñas (por ejemplo 350 W), implica la utilización de corrientes nominales muy elevadas (hasta de 30 A), con transitorios de arranque de 100 A y más; lo cual obliga a seleccionar dispositivos FET MOS tales que su tensión máxima continua en estado abierto entre los terminales fuente y drenador, sea escasamente 3,33 veces la tensión nominal de red (12 V).

Por otro lado, en las instalaciones eléctricas de los automóviles, alimentadas a 12 V, se producen impulsos de tensión, debido a la peculiaridad de tales instalaciones y de los elementos, tanto consumidores como generadores, que en ellas intervienen.

Cabe citar además, que cuando a un conjunto formado por una carga y un dispositivo FET MOS que se encuentra en estado de corte, se le aplica un impulso de tensión de valor suficientemente alto como para provocar que el dispositivo FET MOS entre en conducción por avalancha, es decir habiéndose superado la tensión de bloqueo inverso en la unión P-N que mantiene al circuito abierto, el parámetro que determina si el dispositivo sufrirá o no daño irreversible, es la energía que se disipa en la unión P-N, la cual depende en la práctica, no solo de la forma de onda, valor de pico y duración del impulso de tensión aplicado, sino también de otros parámetros, como las características de la carga eléctrica controlada, así como las características del propio dispositivo FET MOS.

En este contexto el mayor problema se presenta en relación con los impulsos 5a y 5b descritos en la norma ISO 7637-2 párrafo 5.6.5, descritos como impulsos "load dump".

Generalmente a la mayoría de los sistemas de los automóviles, distintos del propio generador o alternador, que es el único que lleva una protección centralizada para limitar la tensión de pico en caso de un evento "load dump", solo se les exigen los impulsos 5b, precisamente debido a la presencia de la protección mencionada en el generador o alternador.

En general los impulsos 5b que así resultan, son perfectamente compatibles con la tensión máxima permisible entre los terminales drenador y fuente de los modelos de dispositivos FET MOS más habituales para controlar las cargas eléctricas más elevadas presentes en los automóviles actuales con sistemas de alimentación eléctrica a 12 V, no presentándose ningún problema cuando se ensayan los componentes y sistemas bajo estas condiciones.

En la práctica, sin embargo, ocurre que se presentan de forma esporádica, durante el funcionamiento de los vehículos, impulsos de igual o mayor magnitud que los impulsos 5a, los cuales causan, a veces, daños irreversibles por avalancha en los dispositivos FET MOS, al superar la disipación de energía los valores máximos que soportan dichos dispositivos.

Estos daños se producen porque al fundirse parcialmente la pastilla semiconductora del dispositivo FET MOS, se crea un camino conductor permanente en la misma, quedando el dispositivo en estado permanente de conducción y alimentando a la carga, sin que la circuitería de control pueda actuar sobre ella, dando lugar a una situación que se conoce como "funcionamiento no comandado".

Aparte de las consecuencias indeseables, incluso con riesgos para la seguridad, que puede acarrear el "funcionamiento no comandado" de cualquier dispositivo, existe otra peculiaridad en el fallo de un dispositivo FET MOS, que es que el camino conductor que se forma no es un cortocircuito franco, sino que tiene una resistencia del orden de algunos ohmios, superior a la que presentarla el dispositivo en estado de conducción normal, con lo cual en el dispositivo FET MOS se produce una disipación de potencia y, por tanto, un calentamiento, muy superiores a los que se producen en un funcionamiento normal en condiciones de baja resistencia, resultando totalmente insuficientes los medios de refrigeración disponibles, por lo que se produce una peligrosa elevación de temperatura del dispositivo que puede conllevar riesgo de incendio.

Ante esta debilidad de los dispositivos FET MOS, se han desarrollado lo que se denomina FET MOS inteligentes o SMART MOSFET, los cuales incorporan junto al dispositivo interruptor semiconductor simple y formando una unidad con el, un segundo circuito integrado de monitorización y control, capaz de detectar condiciones anómalas, como sobre-corriente y sobre-temperatura, desactivando el circuito principal para protegerlo, en caso de producirse situaciones que excedan las condiciones de funcionamiento seguro.

El recurso más habitual para la protección contra las sobre-tensiones, es la monitorización de la tensión del terminal drenador y la puesta en conducción del dispositivo si la tensión entre dicho terminal drenador y el terminal fuente excede un valor prefijado, de forma que la energía del pulso sea disipada sobre todo en la carga exterior y no en una unión P-N forzada al estado de avalancha.

Ensayos realizados con los dispositivos SMART MOSFET comerciales, han demostrado, sin embargo, que en muchos casos estos dispositivos no tienen mejores prestaciones que los dispositivos FET MOS estándar no protegidos, siendo igualmente destruidos por los impulsos del rango 5a y superiores.

Otra solución orientada a evitar que, cuando se produce el deterioro de los dispositivos FET MOS, se alcancen temperaturas peligrosas en los circuitos de aplicación de los que forman parte, es la disposición de dispositivos miniaturizados de protección térmica que actúan como fusibles, interrumpiendo el circuito cuando la temperatura en el mismo sobrepasa un limite. Un dispositivo de este tipo se describe, por ejemplo, en la Patente US 20100245022.

Reivindicaciones:

1. Complemento para señalización de error en circuitos de control de potencia, para aplicación en relación con un circuito de control de un dispositivo FET MOS (T1) de alimentación de una carga (R1), en el cual se incluye un termofusible (F1) de protección contra temperaturas excesivas, caracterizado porque comprende una red formada en torno a uno o más transistores adicionales conectados a los bornes del termofusible (F1) conectado en serie con el dispositivo FET MOS (T1) y la carga (R1), para cualquier posición del termofusible (F1) en dicho circuito serie, de tal manera que, al abrirse el termofusible (F1), dicha red fuerza a un terminal de control (V4) a adoptar una tensión tal que puede ser interpretada como una situación de error por una unidad de control exterior conectada al mencionado terminal de control (V4).

2. Complemento para señalización de error en circuitos de control de potencia, de acuerdo con la primera reivindicación, caracterizado porque comprende un transistor (Q3), el cual se conecta por su colector y su emisor, respectivamente, en relación con un terminal (V4) por el que se aplica una señal de control y en relación con un terminal (V3) de conexión del circuito de control del dispositivo FET MOS (T1), mientras que la base de dicho transistor (Q3) se conecta respecto de un punto intermedio entre el termofusible (F1) de protección y el dispositivo FET MOS (T1), en el circuito de control.

3. Complemento para señalización de error en circuitos de control de potencia, de acuerdo con la segunda reivindicación, caracterizado porque la conexión del colector del transistor (Q3) respecto del terminal (V4) de aplicación de la señal de control, se establece a través de una resistencia (R7).

4. Complemento para señalización de error en circuitos de control de potencia, de acuerdo con la segunda reivindicación, caracterizado porque la conexión de la base del transistor (Q3) respecto de un punto intermedio entre el termofusible (F1) y el dispositivo FET MOS (T1), se establece a través de una resistencia (R8).

Patentes similares o relacionadas:

Módulo de sensor de compresor, del 18 de Diciembre de 2019, de EMERSON CLIMATE TECHNOLOGIES, INC: Un sistema que comprende: un compresor que comprende un motor eléctrico configurado para conectarse a una fuente de alimentación ; un módulo de […]

Contador de energía eléctrica que puede monitorizar un estado de contacto de un relé de enclavamiento, del 28 de Agosto de 2019, de LSIS Co., Ltd: Un contador de energía eléctrica que puede monitorizar un estado de contacto de un relé de enclavamiento, comprendiendo el contador de energía eléctrica:

[…]

Contador de energía eléctrica que puede monitorizar un estado de contacto de un relé de enclavamiento, del 28 de Agosto de 2019, de LSIS Co., Ltd: Un contador de energía eléctrica que puede monitorizar un estado de contacto de un relé de enclavamiento, comprendiendo el contador de energía eléctrica:

[…]

Dispositivo de visualización del objetivo de consumo de energía eléctrica, del 7 de Agosto de 2019, de Nihon Techno Co., Ltd: Un dispositivo de visualización del objetivo de demanda que comprende: una escala de doble finalidad para indicar la hora y el consumo de energía eléctrica; […]

Procedimiento y sistema de análisis de calidad de la energía e índice de calidad 2S2PQ, caracterización de la señal en un punto del suministro eléctrico, del 30 de Abril de 2019, de UNIVERSIDAD DE CADIZ: Procedimiento y sistema de análisis de la calidad de la energía e índice de calidad 2S2PQ para la caracterización de la señal en un punto del suministro eléctrico. El […]

Dispositivo de alimentación a pilas para un aparato contador de energía, y aparato contador de energía, del 25 de Marzo de 2019, de Itron Global SARL: Aparato contador de energía que comprende una tarjeta de circuito impreso , un dispositivo de alimentación a pilas para alimentar eléctricamente a la […]

Diagnóstico de calidad de potencia para el acondicionamiento de potencia, del 6 de Marzo de 2019, de Electronic Systems Protection, Inc: Un sistema de diagnóstico de potencia acondicionada que comprende: un monitor de potencia que comprende: un circuito de […]

Procedimiento y sistema de puesta en práctica para la medición de la potencia de desequilibrio en instalaciones eléctricas, así como el dispositivo para su calibración, del 9 de Octubre de 2018, de UNIVERSIDAD POLITECNICA DE VALENCIA: Procedimiento y sistema de puesta en práctica para la medida de la potencia de desequilibrio de una instalación o sistema eléctrico que comprende: i) adquirir valores instantáneos […]

Algoritmo para método de compensación pasiva de factor de potencia con cambio de condensador diferencial y ruido transitorio de línea reducido, del 8 de Octubre de 2018, de Edge Electrons Limited: Un método para realizar compensación pasiva de factor de potencia sobre la base de cambio de condensador diferencial, que comprende: adquirir mediciones […]