CAMBIO SIN JUNTURAS DE LA PROFUNDIDAD DE UN ENTRELAZADOR CONVOLUCIONAL GENERAL DURANTE UNA TRANSMISIÓN SIN PÉRDIDA DE DATOS.

Un transceptor (18, 38) configurado para transmitir datos sobre un medio de transmisión (4);

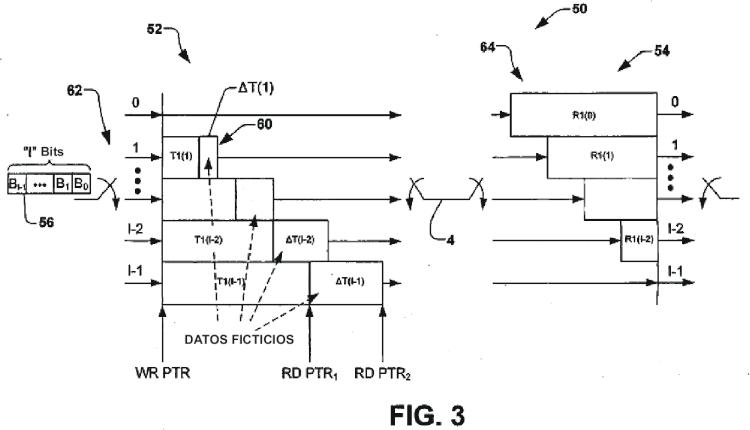

y Un sistema de corrección de error directo (34, 14) operablemente acoplado al transceptor (38,18), y configurado para transmitir los datos codificados al transceptor (38, 18) para la transmisión del mismo, en donde el sistema de corrección de error directo (34, 14) comprende un entrelazador convolucional (52, 50) configurado para recibir una pluralidad de palabras código o bloques de datos y entrelazar la pluralidad de palabras código o bloques de datos con base en la profundidad del entrelazador, y además ser configurado para variar la profundidad del entrelazador por una cantidad diferente de un múltiplo de entero de una longitud del bloque de la pluralidad de palabras código o bloques de datos, En donde el entrelazador (52, 50) comprende una pluralidad de los FIFO de transmisión (60), en donde el número de los FIFO de transmisión (60) es igual al número de bits de datos en una palabra código o un bloque de datos, En donde el entrelazador comprende un circuito de control (36, 16) configurado para alterar un tamaño del FIFO de transmisión (60) con base en un cambio en la profundidad del entrelazador comunicada a este

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2005/012298.

Solicitante: INFINEON TECHNOLOGIES AG.

Nacionalidad solicitante: Alemania.

Dirección: AM CAMPEON 1-12 85579 NEUBIBERG ALEMANIA.

Inventor/es: HEISE,BERND.

Fecha de Publicación: .

Fecha Solicitud PCT: 16 de Noviembre de 2005.

Clasificación PCT:

- H03M13/27 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › usando técnicas de entrelazado.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia.

PDF original: ES-2359008_T3.pdf

Fragmento de la descripción:

40

45

50

CAMPO DE LA INVENCIÓN

La presente invención se relaciona de manera general con sistemas de comunicaciones y más particularmente con métodos de comunicación adaptativos que utilizan una línea de suscriptor digital (DSL).

ANTECEDENTES DE LA INVENCIÓN

La tecnología de línea de suscriptor digital (DSL) suministra transferencia de datos a alta velocidad entre dos módems a través de líneas telefónicas ordinarias, en donde las tasas de transferencia de datos digitales desde decenas Kbps a decenas Mbps son soportadas sobre líneas telefónicas estándar (por ejemplo par entorchado), aunque aún suministre servicio telefónico antiguo normal (POTS). La línea de suscriptor digital asíncrona (ADSL) y la línea de suscriptor digital muy alta (VDSL) han surgido como implementaciones populares de los sistemas VDSL, donde el ADSL se define por o mediante el estándar del Instituto de Estándar Nacional Americano (ANSI) T1.413 y los estándares de la Unión de Telecomunicación Internacional (ITU-T) G.992.3, G.992.5, y VDSL se define por el estándar ANSI T 1.424 y el estándar ITU-T G.993.1. El ADSL, VDSL y otros sistemas DSL similares (denominados colectivamente como “xDSL”) suministran típicamente transferencias de datos digitales en un rango de frecuencia por encima de la banda POTS (aproximadamente 300 Hz a 400 kHz), por ejemplo el ADSL G.992.3 opera a frecuencias desde aproximadamente 25 kHz a aproximadamente 1.1 mHz.

La mayoría de las instalaciones DSL son operadas como sistemas multiportadores que utilizan modulación multitono discreta (DMT), en los cuales se transmiten datos mediante una pluralidad de subportadoras (tonos), algunas veces de manera alternativa como subcanales, sub-bandas, subportadoras, o bins, con cada soportadora individual utilizando una porción preferida del rango de frecuencia descrito. En el ADSL, por ejemplo, se utilizan 256 subportadoras para transmitir un símbolo DMT, teniendo cada subportadora un ancho de banda de 4.3125 kHz. La transmisión de datos digitales se codifica y se modula en el transmisor utilizando Modulación de Amplitud en Cuadratura (QAM) y Transformación de Fourier Discreta Inversa (IDFT) para crear la señal multiportadora modulada para la transmisión a lo largo de un ciclo o canal DSL, que es luego desmodulado en el extremo receptor y decodificado para recuperar los datos transmitidos. Los bits de datos a ser transmitidos sobre cada subportadora son codificados como puntos de señal en las constelaciones de señal QAM utilizando un codificador o un sistema de mapeo de bits. Las constelaciones de señal son entonces moduladas sobre la subportadora correspondiente. El número total de bits de datos transmitidos sobre el canal es una suma de los bits transmitidos por cada subportadora.

Como en la mayoría de los tipos de sistemas de comunicación, es deseable maximizar la cantidad de datos transferidos exitosamente a través del medio de comunicación entre los módems DSL, algunas veces denominados como las tasa de bits o la tasa de datos. La tasa de datos, a su vez, depende de las características de ruido de un canal de comunicación particular. En el caso de los sistemas DLS, se conecta un par de módems a un par entorchado de alambres (algunas veces denominados como un aro) que forma el medio de comunicación. En esta situación, el ruido puede ser generado por señales de pares de alambres vecinos (por ejemplo ruido de charlas) en un sistema de telefonía distribuido, así como también fuentes externas de interferencia de radiofrecuencia (RFI) u otros ruidos. El ruido sobre un canal de comunicación particular se puede modelar o caracterizar de manera general como un ruido continuo o ruido de impulso o ambos. El ruido continuo es algunas veces modelado como un ruido Gausiano Aditivo (AGN) con valores aleatoriamente distribuidos de ruido durante el tiempo, mientras que el ruido de impulso es generalmente explosiones cortas de niveles relativamente altos de ruido de canal. Se emplean varios mecanismos o técnicas en DSL y otros sistemas de comunicaciones para combatir el ruido continuo y de impulso y/o corregir los errores de transferencia de datos relacionados con el ruido.

El ruido continuo se maneja típicamente al transmitir más bits de datos sobre las subportadoras con pequeñas cantidades de ruido continuo, y más pocos bits de datos sobre las subportadoras con mayor ruido continuo. La ubicación de los bits de datos a las subportadoras particulares se denomina algunas veces como ubicación de bit o distribución de bit, mientras que los parámetros de distribución de bit se pueden ajustar para acomodar las condiciones de ruido continuo particulares sobre el canal. Sin embargo, simplemente maximizar la protección de ruido continuo al reducir el número de bits transmitidos por las subportadoras específicas puede conducir a una tasa de datos de un sistema no óptimo, en razón en que maximizar la protección de ruido continuo de esta manera reduce el número de bits de datos sobre las subportadoras. De acuerdo con esto, los sistema DSL son inicialmente configurados con protección de ruido continuo (por ejemplo distribución de bits) configuraciones o parámetros que son seleccionados de acuerdo a la evaluación de ruido de la subportadora con base en la estimación del ruido del canal durante la inicialización del sistema. Aunque tales aproximaciones que utilizan las configuraciones de protección de ruido continuo suministran una buena protección al ruido continuo y unas altas tasas de transferencia de datos, las configuraciones de protección de ruido continuo suministran una buena protección de ruido continuo y unas altas tasas de transferencia de datos, las condiciones de ruido continuo del canal de comunicación tienden a cambiar durante el tiempo. A este respecto, si el ruido continuo disminuye, los parámetros de modulación fijos serán suficientes para proteger contra los errores de datos, pero no se logran tasas de datos incrementadas potenciales. Por el contrario, si el ruido continuo se incrementa, los parámetros de protección ampliamente ajustados pueden ya no ser suficientes para suministrar una protección adecuada contra los errores de transferencia de datos en el canal.

Con el fin de manejar esta situación, el sistema DSL suministra sintonización adaptativa de las configuraciones del parámetro de distribución de bit para acomodar el cambio del ruido continuo, incluyendo intercambio de bit, adaptación de la tasa, y técnicas de repartición de ancho de banda, cada una de las cuales involucra cambios en un número de los parámetros de modulación. En una situación típica, la proporción de señal a ruido (SNR) para cada subportadora se mide durante la iniciación del sistema, y se determina la capacidad de bit máxima de cada subportadora. Una vez que se evalúa de esta manera la capacidad de transmisión del sistema, se asignan más bits, (por ejemplo tamaños de constelaciones mayores) a las subportadoras con mayores SNR comparados con las subportadoras que tienen SNR inferior y se asignan las potencias de transmisión relativas de la subportadora (ganancias). El servicio DLS es luego iniciado y la subportadora SNR son medidas durante la transmisión de datos; la redistribución de bits (intercambio de bits) que son efectuados y las ganancias de la subportadora que son ajustadas de acuerdo a los cambios en las mediciones SNR de la subportadora.

El intercambio de bits en sí mismo no cambia la tasa de datos total del canal de comunicaciones, sino que sirve para incrementar o mantener, la inmunidad de ruido continuo al relocalizar los bits de datos desde las subportadoras ruidosas a más subportadoras libres de ruido. Donde el ruido del canal se incrementa significativamente, el intercambio de bits solo puede no ser adecuado para evitar los errores de la transmisión de datos, y la adaptación de la tasa sin junturas (SRA) se puede emplear para disminuir el número de bits de datos transmitidos sobre algunas subportadoras. Si el ruido continuo del canal posteriormente disminuye, (por ejemplo se incrementa el SNR), el SRA puede entonces ser utilizado para incrementar el número de bits de datos. Aunque estas técnicas pueden reaccionar efectivamente al cambiar las condiciones de ruido continuo, la protección del ruido de impulso no se afecta mayormente por las configuraciones de distribución de bits y la adaptación de las tasas sin junturas.

El ruido de impulso en los sistemas DSL usualmente origina el borrado de una señal modulada completa durante un periodo relativamente corto de tiempo, sin importar el número de bits ubicados en el canal... [Seguir leyendo]

Reivindicaciones:

1. Un sistema de transmisión que comprende:

Un transceptor (18, 38) configurado para transmitir datos sobre un medio de transmisión (4); y

Un sistema de corrección de error directo (34, 14) operablemente acoplado al transceptor (38,18), y configurado para transmitir los datos codificados al transceptor (38, 18) para la transmisión del mismo, en donde el sistema de corrección de error directo (34, 14) comprende un entrelazador convolucional (52, 50) configurado para recibir una pluralidad de palabras código o bloques de datos y entrelazar la pluralidad de palabras código o bloques de datos con base en la profundidad del entrelazador, y además ser configurado para variar la profundidad del entrelazador por una cantidad diferente de un múltiplo de entero de una longitud del bloque de la pluralidad de palabras código o bloques de datos,

En donde el entrelazador (52, 50) comprende una pluralidad de los FIFO de transmisión (60), en donde el número de los FIFO de transmisión (60) es igual al número de bits de datos en una palabra código o un bloque de datos,

En donde el entrelazador comprende un circuito de control (36, 16) configurado para alterar un tamaño del FIFO de transmisión (60) con base en un cambio en la profundidad del entrelazador comunicada a este.

2. El sistema de transmisión de la reivindicación 1, en donde el sistema de corrección de error directo (34, 14) se configura para alterar la profundidad del entrelazador convolucional con base en los datos de ruido de impulso recibidos.

3. El sistema de transmisión de la reivindicación 1, en donde el circuito de control (36, 16) se configura para alterar el tamaño de los FIFO de transmisión (60) de acuerdo a ºT (z,y) = ºTraw (z, y) – ºTmin (y), en donde ºT (z,y) comprende un cambio en el tamaño en el FIFO del z avo FIFO (60) en un momento anterior a que se lea una salida del y avo FIFO (60), en donde ºTmin (y) es cero cuando existe un incremento en la profundidad del entrelazador y en donde ºTmin (y) = min (ºTraw(z,y)), en donde ºTmin(y) es el valor mínimo de ºTraw(z,y) para z = (1,…I-1) cuando existe una disminución en la profundidad del entrelazador, en donde un tamaño de un cero avo FIFO permanece sin cambio, y en donde

**(Ver fórmula)**

En donde

**(Ver fórmula)**

En donde Dj representa la profundidad del entrelazador antes del cambio de la profundidad del entrelazador, en donde Dj es D1, o después del cambio de la profundidad del entrelazador, en donde Dj es D2, y en donde el piso (m) es un operador matemático en donde el valor “m” se redondea en el siguiente valor entero más bajo.

4. El sistema de transmisión de la reivindicación 1, en donde el circuito de control (36, 16) se configura además para alterar un orden en el cual los bits de datos se leen de los FIFO de transmisión (60) con base en el cambio en la profundidad del entrelazador.

5. El sistema de transmisión de la reivindicación 1, en donde el circuito de control, (36, 16) se configura adicionalmente para averiguar una disminución en la profundidad del entrelazador desde una profundidad inicial D1 a una nueva profundidad D2, en donde D2<D1, y además se configura para simular un cambio en la profundidad del entrelazador de D2 a D1 como un incremento hipotético en la profundidad del entrelazador, obteniendo de esta manera un patrón simulado y un orden de datos transmitidos desde un lado del receptor a un lado del transmisor, en donde el patrón simulado se basa en la transmisión selectiva simulada de bits de datos o bits ficticios, y en donde el circuito de control (36, 16) se configura además para formar un patrón invertido y un orden invertido de transferencia de datos con base en el patrón simulado, y emplea el patrón invertido y el orden invertido para transmitir selectivamente los bits de datos y los bits ficticios desde el lado del transmisor al lado del receptor, en donde el patrón invertido da como resultado una disminución en la profundidad del entrelazador D1 a D2.

Patentes similares o relacionadas:

Método y aparato para la transmisión inalámbrica de datos sujetos a bloqueos de señal periódicos, del 6 de Mayo de 2020, de Hughes Network Systems, LLC: Un método, que comprende: segmentar (S311, S321, S331) un flujo de datos en paquetes de un tamaño fijo para una transmisión en modo ráfaga a través de […]

Método y aparato para la transmisión inalámbrica de datos sujeta a bloqueos de señal periódicos, del 23 de Octubre de 2019, de Hughes Network Systems, LLC: Un método para la transmisión inalámbrica de una primera corriente de datos, estando la transmisión sujeta a bloqueos periódicos, el método que comprende: segmentar una […]

Aparato y método de procesamiento de datos, del 25 de Septiembre de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos operable para mapear símbolos de datos recibidos de un número predeterminado de señales de subportadoras de símbolos […]

Aparato y método de procesamiento de datos, del 25 de Septiembre de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos operable para mapear símbolos de datos recibidos de un número predeterminado de señales de subportadoras de símbolos […]

Intercalador de bits para un sistema de BICM con códigos de QC-LDPC, del 3 de Julio de 2019, de PANASONIC CORPORATION: Un procedimiento de intercalación de bits para intercalar bits de una palabra de código generada en base a un esquema de codificación de comprobación de paridad de baja densidad […]

Aparato y método de procesamiento de datos, del 8 de Mayo de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos para mapear símbolos recibidos desde un número predeterminado de señales de subportadoras de un símbolo multiplexado por división ortogonal […]

Intercalador de bits para un sistema de BICM con códigos QC LDPC, del 6 de Marzo de 2019, de PANASONIC CORPORATION: Un procedimiento de entrelazado de bits para entrelazar bits de una palabra de código generada basándose en un esquema de codificación de verificación de paridad de baja densidad […]

Entrelazador de bits para un sistema BICM con códigos QC LDPC, del 28 de Febrero de 2019, de PANASONIC CORPORATION: Un método de entrelazado de bits para entrelazar bits de una palabra de código generada en base a un esquema de codificación con comprobación de paridad de baja densidad […]

Método de codificación del código polar y dispositivo de codificación, del 27 de Febrero de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación del código polar, caracterizado por comprender: asignar M bits reservados de una señalización de difusión a M bits […]