DISPOSITIVO DE COMPENSACION DEL ERROR DE FASE ESTATICA EN UN SISTEMA DE BUCLE DE BLOQUEO DE FASE DE ESTRUCTURA SIMETRICA.

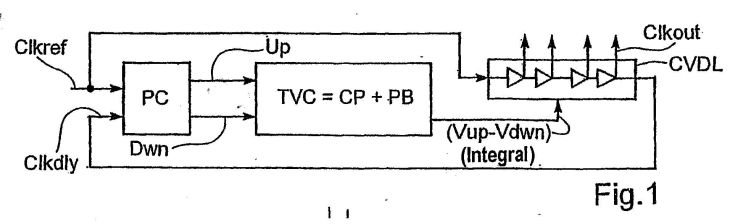

Un dispositivo de bucle de bloqueo de fase que comprende un comparador de fase (PC),

que posee unas primera y segunda entradas que reciben, respectivamente, unas primera y segunda señales de reloj (Clkref y Clkdly), y unas primera y segunda salidas que suministran, respectivamente, unas primera y segunda señales lógicas (Up y Dwn), un bloque de conversión de tiempo-tensión simétrico que posee al menos unas primera y segunda entradas que reciben, respectivamente, las primera y segunda señales lógicas (Up y Dwn), y unas primera y segunda salidas que suministran, respectivamente, una tensión (Vup, Vdwn, Vdiff+ y Vdiff-) que es función de las primera y/o segunda señales lógicas (Up y Dwn), así como un bloque de tratamiento de tensión, que posee unas primera y segunda entradas que reciben, respectivamente, unas primera y segunda tensiones que se han de tratar (Vup, Vdwn, Vdiff+ y Vdiff-), caracterizado por que comprende, además, unos primer (I1P1 e I1P2) y segundo (I2P1 e I2P2) pares de conmutadores de apertura / cierre alterno de acuerdo con unas primera y segunda fases (P1 y P2), intercalados entre las primera y segunda salidas del bloque de conversión tiempo-tensión simétrico, por una parte, y las primera y segunda entradas del bloque de tratamiento de tensión, por otra parte, unos tercer (I3P1 e I3P2) y cuarto (I4P1 e I4P2) pares de conmutadores de apertura / cierre alterno de acuerdo con las primera y segunda fases (P1 y P2), dispuestos aguas arriba de las primera y segunda entradas del comparador de fase (PC), así como medios de gobierno, apropiados para gobernar la apertura / cierre de los primer a cuarto pares de conmutadores de manera que se conecte durante la primera fase (P1) la primera señal de reloj (Clkref) a la primera entrada del comparador y la segunda señal de reloj (Clkdly) a la segunda entrada del comparador, y la primera salida del bloque de conversión a la segunda entrada del bloque de tratamiento, y la segunda salida del bloque de conversión a la primera entrada del bloque de tratamiento, y, durante la segunda fase (P2), la primera señal de reloj (Clkref) a la segunda entrada del comparador y la segunda señal de reloj (Clkdly) a la primera entrada del comparador, y la primera salida del bloque de conversión a la primera entrada del bloque de tratamiento, y la segunda salida del bloque de conversión a la segunda entrada del bloque de tratamiento.

Tipo: Resumen de patente/invención.

Solicitante: COMMISSARIAT A L'ENERGIE ATOMIQUE.

Nacionalidad solicitante: Francia.

Dirección: 25, RUE LEBLANC IMMEUBLE "LE PONANT D",75015 PARIS.

Inventor/es: MASSON, GILLES.

Fecha de Publicación: .

Fecha Concesión Europea: 23 de Enero de 2008.

Clasificación PCT:

- H03L7/089 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › generando el detector de fase o de frecuencia impulsos de aumento o de disminución (H03L 7/087 tiene prioridad).

Patentes similares o relacionadas:

Convertidor de fase a digital en bucle de bloqueo de fase totalmente digital, del 3 de Junio de 2020, de QUALCOMM INCORPORATED: Un procedimiento de conversión de fase a digital, comprendiendo el procedimiento: recibir por medio de un multiplexor de selección de ruta […]

Bucle cerrado de retardo analógico/digital, del 23 de Mayo de 2012, de MOSAID TECHNOLOGIES INCORPORATED: Un bucle cerrado de retardo incluyendo: un circuito de retardo digital que permite que elementos de retardo digital proporcionen ajuste […]

BUCLE DE ENGANCHE DE FASE., del 16 de Abril de 2006, de FUJITSU GENERAL LIMITED: Bucle de enganche de fase que comprende: un comparador de fase para comparar una señal de referencia (REF) y una señal de comparación (VAR) para generar una señal […]

METODO PARA REALIZAR COMPARACIONES DE FASE Y COMPARADOR DE FASE., del 16 de Septiembre de 2003, de NOKIA NETWORKS OY: ESTA INVENCION SE REFIERE A UN PROCEDIMIENTO DE COMPARACION DE FASE Y A UN COMPARADOR DE FASE. EN LA SOLUCION, SE COMPARAN DOS SEÑALES BINARIAS […]

CIRCUITO INYECTOR DE CARGA DE ALTA VELOCIDAD Y BAJA DERIVA., del , de GENNUM CORPORATION: UN DISPOSITIVO PARA CONVERTIR PULSOS LOGICOS BINARIOS EN CORRIENTE DE SALIDA Y SIENDO LA CORRIENTE DE SALIDA CONMUTABLE ENTRE POLARIDAD POSITIVA Y […]

REDUCCION DE CORRIENTE EN UN SINTETIZADOR., del 16 de Enero de 1997, de MOTOROLA, INC.: SE PROPORCIONA UN SINTETIZADOR PARA INCLUIR UN DETECTOR , UN FILTRO DE BUCLE , UNA FUENTE DE CORRIENTE Y DOS ACUMULADORES . LA FUENTE DE CORRIENTE […]

SINTETIZADOR CON BUCLE DE ENGANCHE DE FASE Y ADAPTACION CONTINUA, del 16 de Mayo de 1995, de MOTOROLA, INC.: SE REVELA UN SINTETIZADOR ENGANCHADO EN FASE Y ADAPTACION CONTINUA EN EL QUE LOS IMPULSOS DE CORRECCION DE ERROR PROVENIENTES DE UN DETECTOR DE FASE […]

DETECCION DE FASE DIGITAL, LINEAL, SIN BANDA MUERTA, del 1 de Julio de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un bucle de bloqueo de fase fraccionario en N que comprende: un detector de fase que comprende: una primera entrada dispuesta para […]

DETECCION DE FASE DIGITAL, LINEAL, SIN BANDA MUERTA, del 1 de Julio de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un bucle de bloqueo de fase fraccionario en N que comprende: un detector de fase que comprende: una primera entrada dispuesta para […]