CIRCUITO CERRADO DE FASE ADAPTATIVA.

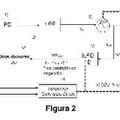

SE PRESENTA UN SISTEMA PLL QUE TIENE UN OSCILADOR VARIABLE Y UN APARATO PARA GENERAR SEÑALES DE ERROR TANTO DE FASE COMO DE FRECUENCIA PARA CONTROLAR EL OSCILADOR VARIABLE.

EL SISTEMA INCLUYE UN APARATO SENSIBLE A LA POLARIDAD DE LA SEÑAL DE ERROR DE FRECUENCIA, PARA DESCONECTAR DE FORMA SELECTIVA LA SEÑAL DE ERROR DE FRECUENCIA DEL OSCILADOR VARIABLE CUANDO EL SISTEMA PLL ALCANZA LA FRECUENCIA.

Tipo: Resumen de patente/invención.

Solicitante: THOMSON CONSUMER ELECTRONICS, INC..

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 600 NORTH SHERMAN DRIVE,INDIANAPOLIS INDIANA 46201.

Inventor/es: RUMREICH, MARK, FRANCIS, CANFIELD, BARTH, ALAN, SCHEMMANN, HEINRICH.

Fecha de Publicación: .

Fecha Concesión Europea: 27 de Mayo de 1998.

Clasificación Internacional de Patentes:

- H03L7/08 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › Detalles del bucle cerrado en fase.

Patentes similares o relacionadas:

Linealizador de forma de onda, del 12 de Junio de 2019, de MBDA UK LIMITED: Una fuente de barrido de frecuencia para un radar FMCW que comprende un sintetizador de frecuencia de bucle de bloqueo de fase, incluyendo el bucle bloqueado […]

Circuito de generación de reloj y procedimiento de generación de la señal de reloj, del 12 de Junio de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un circuito de generación de reloj , que comprende una primera fuente de reloj , una segunda fuente de reloj y un circuito de puerta lógica , […]

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Sistema de bloqueo y procedimiento del mismo, del 25 de Febrero de 2015, de ZTE CORPORATION: Sistema de bloqueo, caracterizado por comprender una unidad de discriminación y conversión de fase digital, una unidad de filtro del bucle digital y una unidad de oscilación […]

Procedimiento, circuito de mando de bus CAN y sistema bus CAN para la recuperación de una frecuencia de pulso de reloj de un bus CAN, del 15 de Enero de 2014, de ROBERT BOSCH GMBH: Procedimiento para la recuperación de una frecuencia de pulso de reloj (T) de un bus CAN con un dispositivomaestro con un generador […]

SINTETIZADOR DE FRECUENCIA Y DIVISOR DE FRECUENCIA POR D BASADO EN LA TOPOLOGÍA DE ENGANCHE POR INYECCIÓN, del 1 de Marzo de 2013, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sintetizador de frecuencia y divisor de frecuencia por D basado en la topología de enganche por inyección.

El sintetizador comprende:

- un […]

SINTETIZADOR DE FRECUENCIA Y DIVISOR DE FRECUENCIA POR D BASADO EN LA TOPOLOGÍA DE ENGANCHE POR INYECCIÓN, del 1 de Marzo de 2013, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sintetizador de frecuencia y divisor de frecuencia por D basado en la topología de enganche por inyección.

El sintetizador comprende:

- un […]

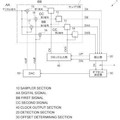

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

CALIBRACION DEL ANCHO DE BANDA PARA UN BUCLE BLOQUEADO EN FRECUENCIA., del 16 de Marzo de 2006, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): Un método para calibrar un bucle bloqueado o fijado en frecuencia, que está destinado a filtrar una señal de referencia extraída de una red de transporte para utilizarla […]