SISTEMA DE TRATAMIENTO DE DATOS REDUNDANTE DE ALTA VELOCIDAD.

Un sistema de tratamiento de datos que comprende una entrada de datos (IN),

un primer módulo (10), y un segundo módulo (14) de tratamiento de datos, y un primer (12) y segundo (16) módulos de comprobación de datos, en el que: dichos primer y segundo (10, 14) módulos de tratamiento de datos están cada uno dispuestos para realizar las mismas operaciones de tratamiento sobre datos recibidos en dicha entrada de datos (IN), proporcionando cada uno una salida; dicho primer módulo de comprobación tiene una primera y segunda entradas y dicho segundo módulo de comprobación tiene una primera y segunda entradas, en el que dichas primera y segunda entradas de dicho primer módulo de comprobación reciben las salidas de dichos primer y segundo módulos de tratamiento de datos respectivamente; y dichos primer y segundo módulos de comprobación (12, 16) están dispuestos para comparar las salidas de dichos primer y segundo módulos de tratamiento de datos (10, 14); dicho primer módulo de comprobación emite una primera señal de error indicativa de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos; y dicho segundo módulo de comprobación está también dispuesto para emitir una señal de error indicativa de si dichos primer y segundo módulos de tratamiento de datos (10, 14) han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos; caracterizado porque dichos primer y segundo módulos de comprobación (12, 16) están situados en dispositivos separados físicamente; dicho segundo módulo de comprobación tiene una tercera entrada; dicho primer módulo de comprobación emite una primera y segunda señales de datos correspondientes a dichas salidas de dichos primer y segundo módulos de tratamiento de datos respectivamente; y dicha primera y segunda entradas de dicho segundo módulo de comprobación reciben dicha primera y segunda señales de datos procedentes de dicho primer módulo de comprobación y dicha tercera entrada de dicho segundo módulo de comprobación recibe dicha primera señal de error procedente de dicho primer módulo de comprobación; estando dispuesto el segundo módulo de comprobación para comprobar las salidas del primer módulo de comprobación

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/GB2006/004720.

Solicitante: EADS DEFENCE AND SECURITY SYSTEMS LIMITED.

Nacionalidad solicitante: Reino Unido.

Dirección: QUADRANT HOUSE CELTIC SPRINGS COEDKERNEW,NEWPORT NP10 8FZ.

Inventor/es: LEARMONTH,DARREN,STEWART.

Fecha de Publicación: .

Fecha Concesión Europea: 20 de Enero de 2010.

Clasificación Internacional de Patentes:

- G06F11/16C6R

Clasificación PCT:

- G06F11/16 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Detección o corrección de errores en un dato por redundancia en el hardware.

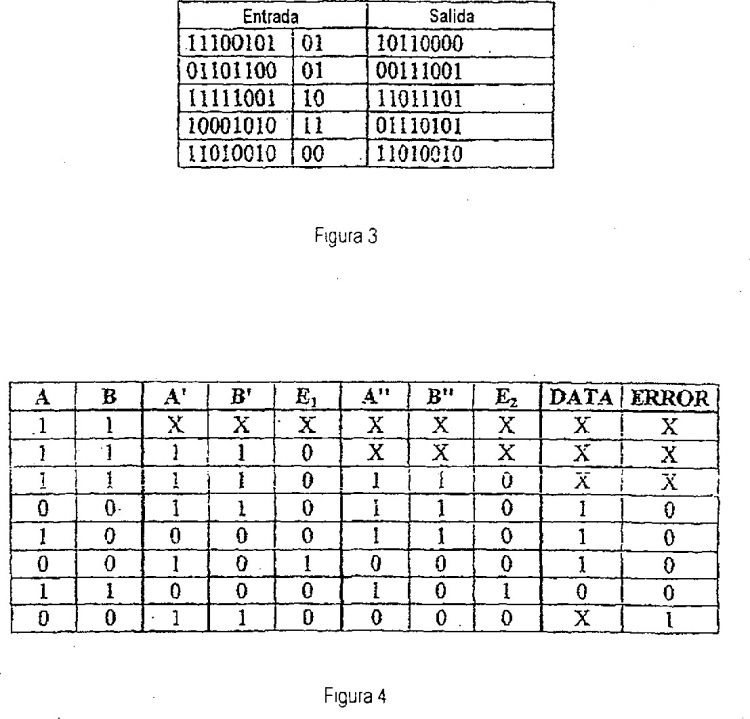

Fragmento de la descripción:

Sistema de tratamiento de datos redundante de alta velocidad.

El invento se refiere a sistemas y métodos de tratamiento de datos, en particular a sistemas de tratamiento de datos que operan a altas velocidades, con elevados niveles de exactitud.

Dos de las cuestiones clave para cualquier sistema de tratamiento de datos son la velocidad y exactitud del tratamiento de datos. Se han propuesto muchas disposiciones para aumentar la exactitud; sin embargo, tales disposiciones a menudo requieren operaciones de tratamiento adicionales, que, o bien disminuyen la velocidad de funcionamiento, o bien aumentan el coste de puesta en práctica, o ambas cosas. Por consiguiente, en algunos sistemas de tratamiento de datos la velocidad, exactitud y coste son requisitos conflictivos que necesitan ser equilibrados de acuerdo con las exigencias del sistema de tratamiento de datos.

Muchos métodos para aumentar la exactitud hacen uso de la redundancia. Por ejemplo, una función particular puede ser puesta en práctica tres veces usando tres circuitos funcionalmente idénticos que operan en paralelo, siendo aceptada la salida si al menos dos de los tres circuitos dan la misma salida. Tal disposición tiene la atracción de la simplicidad, pero el uso de tres (o más) circuitos en paralelo puede ser considerado demasiado poco económico en algunas circunstancias.

Otras disposiciones para aumentar la exactitud hacen uso de códigos de corrección de error. Tal disposición tiene la ventaja de ser capaz de corregir algunos errores, en vez de identificar errores simplemente, pero los costes generales en términos de datos, y las exigencias de tratamiento de datos, pueden ser caros de poner en práctica, y pueden afectar adversamente a la velocidad de tratamiento de los datos.

El documento DE 19529434 A1 describe un sistema de microprocesador destinado a sistemas de control de seguridad críticos. El sistema de microprocesador incluye dos unidades centrales hechas funcionar de modo síncrono (que reciben los mismos datos de entrada y procesan el mismo programa), memorias de lectura solamente y memorias de acceso aleatorio para datos útiles y datos de ensayo, y comparadores que comprueban las señales de salida de las unidades centrales, y las señales de desconexión en cuestión en el caso de no existencia de correlación. Las unidades centrales están conectadas a las memorias y las unidades de entrada y salida por medio de sistemas de buses o líneas de transmisión separadas y acopladas por etapas de unidades de accionamiento que permiten que la unidades centrales lean y traten conjuntamente los datos disponibles en los dos sistemas de buses.

El documento US-5.086.429 describe un sistema de tratamiento de datos que usa una arquitectura de compartir una única memoria entre dos procesadores ("spare-pair"), que es llamada así para obviar la necesidad de agrupaciones de memorias separadas para cada procesador. Una memoria única es compartida entre cada par de procesadores y un esquema de detección de error de código de bloque lineal es implantado con cada memoria compartida, en el que es detectado el efecto de fallos de memoria aleatoria de modo que no comprometa la tolerancia de fallo inherente de una arquitectura de memoria compartida entre dos procesadores.

Los circuitos de tratamiento de datos son propensos a muchas formas de errores. Una forma particularmente problemática de error son los errores inducidos por radiación, que a veces son denominados como "errores suaves" o "trastornos de un solo evento". Los errores inducidos por radiación son causados por partículas cargadas, tales como partículas radioactivas (por ejemplo, partículas alfa), o partículas causadas por rayos cósmicos de alta energía o partículas solares, causando la ionización del semiconductor de un dispositivo de memoria. Si la carga recogida es lo bastante grande, entonces el estado percibido de una celda de memoria particular puede ser incorrecto. Los errores inducidos por radiación tienden a ser aleatorios por naturaleza y pueden ser difíciles de detectar.

El presente invento busca resolver o mitigar algunos de los problemas esquematizados más arriba, o proporcionar soluciones alternativas a los existentes actualmente.

El presente invento proporciona un sistema de tratamiento de datos que tiene las características descritas en la reivindicación 1ª siguiente. El presente invento también proporciona un método de tratamiento de datos que tiene las características descritas en la reivindicación 12ª siguiente.

En una forma del invento, los módulos de comprobación son circuitos lógicos que determinan si las salidas del primer y segundo módulos de tratamiento son las mismas (indicando que no ha ocurrido ningún error) o diferentes (indicando que ha ocurrido un error). En una forma del invento, la salida de uno de los circuitos de tratamiento de datos es invertida de modo que los módulos de comprobación determinen si las salidas del primer y segundo módulos de tratamiento son las mismas (indicando que ha ocurrido un error) o diferentes (indicando que no ha ocurrido ningún error).

El presente invento proporciona la duplicación del tratamiento de datos, introduciendo por ello la redundancia para detectar errores. Además, como las operaciones de tratamiento de datos son realizadas en paralelo, sin algoritmos de comprobación de cualquier error durante el tratamiento, la velocidad de tratamiento de datos puede ser alta.

Además, previendo los módulos de comprobación de datos en dispositivos separados físicamente, la probabilidad de que no se detecte un error inducido por radiación es reducida.

En una forma del invento, el primer y segundo módulos de comprobación están previstos en circuitos integrados separados que están situados en la misma placa de circuito. Sin embargo, los módulos de comprobación podrían estar previstos en placas de circuito diferentes, o incluso, separadas adicionalmente, particularmente si se han usado sistemas de comunicación inalámbricos para pasar datos para comprobación a los módulos de comprobación. En la totalidad de tales disposiciones, los dispositivos han de ser considerados como estando separados físicamente. Una ventaja de separar físicamente los módulos de comprobación es reducir la probabilidad de errores inducidos por radiación que ocurren en ambos módulos de comprobación de la misma manera. Es muy improbable que ocurran errores idénticos en dos dispositivos separados físicamente.

Dichos primer y segundo módulos de tratamiento de datos pueden estar situados en dispositivos separados físicamente. El primer y segundo módulos de tratamiento de datos podrían estar previstos en circuitos integrados separados que están situados en la misma placa de circuito. Sin embargo, como se ha descrito antes con referencia a los módulos de comprobación, el primer y segundo módulos de tratamiento de datos podrían estar previstos en diferentes placas de circuitos, o incluso, separados adicionalmente. En una realización ejemplar del invento, el primer y segundo módulos de tratamiento de datos están implantados en agrupaciones de puerta programable de campo separadas (FPGAs) que, en uso, están situadas en la misma placa de circuito.

El primer módulo de tratamiento de datos y el primer módulo de comprobación pueden estar situados en la misma posición física, por ejemplo, pueden ser puestos en práctica usando la misma FPGA. Alternativamente, el primer módulo de tratamiento de datos y el primer módulo de comprobación pueden ser implantados en diferentes circuitos integrados; esos circuitos integrados pueden estar situados juntos, lo cual tiene varias ventajas, incluyendo un cableado más simple que tiende a aumentar la velocidad de funcionamiento.

El segundo módulo de tratamiento de datos y el segundo módulo de comprobación pueden estar situados en la misma posición física, por ejemplo, pueden ser puestos en práctica usando la misma FPGA. Alternativamente, el segundo módulo de tratamiento de datos y el segundo módulo de comprobación pueden ser implantados en diferentes circuitos integrados; esos circuitos integrados pueden estar situados juntos, lo cual tiene varias ventajas, incluyendo un cableado más simple que tiende a aumentar la velocidad de funcionamiento.

En una forma del invento, el primer módulo de tratamiento de datos y el primer módulo de comprobación son implantados en un primer circuito integrado y el segundo módulo de tratamiento de datos y el segundo módulo de comprobación son implantados en un segundo circuito integrado.

Las salidas de dichos primer y segundo...

Reivindicaciones:

1. Un sistema de tratamiento de datos que comprende una entrada de datos (IN), un primer módulo (10), y un segundo módulo (14) de tratamiento de datos, y un primer (12) y segundo (16) módulos de comprobación de datos, en el que: dichos primer y segundo (10, 14) módulos de tratamiento de datos están cada uno dispuestos para realizar las mismas operaciones de tratamiento sobre datos recibidos en dicha entrada de datos (IN), proporcionando cada uno una salida; dicho primer módulo de comprobación tiene una primera y segunda entradas y dicho segundo módulo de comprobación tiene una primera y segunda entradas, en el que dichas primera y segunda entradas de dicho primer módulo de comprobación reciben las salidas de dichos primer y segundo módulos de tratamiento de datos respectivamente; y dichos primer y segundo módulos de comprobación (12, 16) están dispuestos para comparar las salidas de dichos primer y segundo módulos de tratamiento de datos (10, 14); dicho primer módulo de comprobación emite una primera señal de error indicativa de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos; y dicho segundo módulo de comprobación está también dispuesto para emitir una señal de error indicativa de si dichos primer y segundo módulos de tratamiento de datos (10, 14) han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos; caracterizado porque dichos primer y segundo módulos de comprobación (12, 16) están situados en dispositivos separados físicamente; dicho segundo módulo de comprobación tiene una tercera entrada; dicho primer módulo de comprobación emite una primera y segunda señales de datos correspondientes a dichas salidas de dichos primer y segundo módulos de tratamiento de datos respectivamente; y dicha primera y segunda entradas de dicho segundo módulo de comprobación reciben dicha primera y segunda señales de datos procedentes de dicho primer módulo de comprobación y dicha tercera entrada de dicho segundo módulo de comprobación recibe dicha primera señal de error procedente de dicho primer módulo de comprobación; estando dispuesto el segundo módulo de comprobación para comprobar las salidas del primer módulo de comprobación.

2. Un sistema de tratamiento de datos según la reivindicación 1ª, en el que dichos primer y segundo módulos de tratamiento de datos están situados en dispositivos separados físicamente.

3. Un sistema de tratamiento de datos según cualquiera de las reivindicaciones 1ª y 2ª, que comprende además un tercer módulo de comprobación dispuesto para comparar las salidas de dichos primer y segundo módulos de tratamiento de datos y para emitir una señal indicativa de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos.

4. Un sistema de tratamiento de datos según la reivindicación 3ª, en el que dicho módulo de comprobación tiene una primera, segunda y tercera entradas, en el que: dicho segundo módulo de comprobación emite una tercera y cuarta señales de datos correspondientes a dichas salidas de dichos primer y segundo módulos de tratamiento de datos respectivamente y una segunda señal de error indicativa de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos; dichas primera y segunda entradas de dicho tercer módulo de comprobación reciben dicha tercera y cuarta señales de datos procedentes de dicho segundo módulo de comprobación y dicha tercera entrada de dicho tercer módulo de comprobación recibe dicha segunda señal de error procedente de dicho primer módulo de comprobación.

5. Un sistema de tratamiento de datos según la reivindicación 3ª o 4ª, en el que el tercer módulo de comprobación está separado físicamente de cada uno de dichos primer y segundo módulos de comprobación.

6. Un sistema de tratamiento de datos según cualquiera de las reivindicaciones 3ª a 5ª, en el que dicha señal indicativa de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos emitida por dicho tercer módulo de comprobación es proporcionada como una entrada a dicho primer módulo de comprobación.

7. Un sistema de tratamiento de datos según cualquier reivindicación precedente, en el que al menos una de dichas señales indicativas de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos es proporcionada como una entrada al menos a uno de dichos primer y segundo módulos de tratamiento de datos.

8. Un sistema de tratamiento de datos según cualquier reivindicación precedente, comprendiendo además un indicador de salida de error, en el que dicho indicador de salida de error es ajustada cuando cualquiera de dichos módulos de comprobación emite una señal que indica que el primer y segundo módulos de tratamiento de datos no ha realizado las mismas operaciones de tratamiento en dichos datos recibidos en dicha entrada de datos.

9. Un sistema de tratamiento de datos según cualquier reivindicación precedente, en el que la funcionalidad de cada uno de dichos primer y segundo módulos de tratamiento está definida por datos almacenados en uno o más módulos de memoria.

10. Un sistema de tratamiento de datos según la reivindicación 9ª, en el que la funcionalidad de dicho primer módulo de tratamiento está definida por datos almacenados en un primer módulo de memoria y la funcionalidad de dicho segundo módulo de tratamiento es definida por datos almacenados en un segundo módulo de memoria.

11. Un sistema de tratamiento de datos según la reivindicación 9ª o la reivindicación 10ª, en el que los datos recibidos en dicha entrada de datos contienen una código que hace referencia a una posición de memoria en dichos módulos de memoria que define la funcionalidad de dichos módulos de tratamiento de datos.

12. Un método de tratamiento de datos que comprende las operaciones de: pasar una entrada de datos tanto a un primer (10) como a un segundo (14) módulos de tratamiento de datos (10, 14); disponer para dichos primer y segundo módulos (10, 14) de tratamiento de datos para realizar el mismo tratamiento sobre dicha entrada de datos; pasar salidas de dichos primer y segundo módulos de tratamiento de datos a dicho primer módulo de comprobación; y disponer para el primer (12) y segundo (16) módulos de comprobación (10, 14) para emitir una señal de error indicativa de si dichos primer y segundo módulos (10, 14) de tratamiento de datos han realizado o no las mismas operaciones sobre dicha entrada de datos; caracterizado porque: dichos primer y segundo módulos (12, 16) están situados en dispositivos separados físicamente; y dicho método comprende además las operaciones de: pasar dichas salidas de dichos primer y segundo módulos de tratamiento de datos desde dicho primer módulo de comprobación a dicho segundo módulo de comprobación, junto con una primer señal de error indicativa de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos, comprobando el segundo módulo de comprobación las salidas del primer módulo de comprobación.

13. Un método según la reivindicación 12ª, en el que dichos primer y segundo módulos de tratamiento de datos están situados en dispositivos separados físicamente.

14. Un método según una cualquiera de las reivindicaciones 12ª y 13ª, comprendiendo además la operación de hacer pasar las salidas de tanto dicho primer como dicho segundo módulos de tratamiento de datos a un tercer módulo de comprobación, en el que dicho tercer módulo de comprobación está dispuesto para emitir una señal de error indicativa de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dicha entrada de datos.

15. Un método según la reivindicación 14ª, que comprende además las operaciones de: hacer pasar dichas salidas de dichos primer y segundo módulos de tratamiento de datos desde dicho segundo módulo de comprobación a dicho tercer módulo de comprobación, junto con una segunda señal de error indicativa de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos.

16. Un método según la reivindicación 14ª o la reivindicación 15ª, en el que el tercer módulo de comprobación está separado físicamente de cada uno de dichos primer y segundo módulos de comprobación.

17. Un método según cualquiera de las reivindicaciones 14ª a 16ª, que comprende además la operación de proporcionar dicha señal indicativa de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mimas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos emitida por dicho tercer módulo de comprobación como una entrada a dicho primer módulo de comprobación.

18. Un método según cualquiera de las reivindicaciones 12ª a 17ª, que comprende además la operación de proporcionar al menos una de dichas señales indicativas de si dichos primer y segundo módulos de tratamiento de datos han realizado o no las mismas operaciones de tratamiento sobre dichos datos recibidos en dicha entrada de datos como una entrada al menos a uno de dichos primer y segundo módulos de tratamiento de datos.

19. Un método según cualquiera de las reivindicaciones 12ª a 18ª, en el que dicha entrada de datos incluye un código que hace referencia a una posición de memoria en uno o más módulos de memoria a los que dichos primer y segundo módulos de tratamiento de datos tienen acceso, definiendo dicha posición de memoria la funcionalidad de dichos módulos de tratamiento de datos.

Patentes similares o relacionadas:

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Procedimiento de parada de emergencia y sistema de seguridad asociado, del 20 de Mayo de 2020, de CLEARSY: Procedimiento de parada de emergencia de un elemento de seguridad de un conjunto de seguridad , comprendiendo el conjunto de seguridad […]

Actualización de software de componentes no críticos en sistemas distribuidos críticos para la seguridad dual, del 13 de Mayo de 2020, de Siemens Mobility GmbH: Procedimiento para el funcionamiento de un sistema crítico para la seguridad con al menos un primer dispositivo de datos con un software aprobado y relevante […]

Sistemas críticos de seguridad ferroviaria con redundancia de tareas y capacidad de comunicaciones asimétricas, del 22 de Enero de 2020, de Siemens Mobility, Inc: Sistema de control para un sistema de aplicación crítico de seguridad ferroviaria, que comprende: al menos un controlador, que comprende un procesador […]

Circuito integrado digital protegido contra errores transitorios, del 9 de Octubre de 2019, de THALES: Circuito integrado digital que comprende un conjunto lógico que comprende un bloque lógico funcional, una unidad lógica de detección […]

Circuito de generación de reloj y procedimiento de generación de la señal de reloj, del 12 de Junio de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un circuito de generación de reloj , que comprende una primera fuente de reloj , una segunda fuente de reloj y un circuito de puerta lógica , […]

Sistema informático de seguridad de tipo relevante, del 7 de Mayo de 2019, de Siemens Mobility GmbH: Sistema informático de seguridad de tipo relevante, particularmente un sistema de seguridad ferroviario, con al menos dos canales hardware (A; B), en donde los […]

Método, ordenador y aparato para migrar datos de memoria, del 6 de Marzo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un ordenador, que comprende: un procesador ; un sistema básico de entrada/salida ; una memoria principal , configurada para cargar […]