SISTEMA Y PROCEDIMIENTO DE COMPUTO DE CEROS DE CABEZA Y DE COMPUTO DE UNOS DE CABEZA EN UN PROCESADOR DE SEÑAL DIGITAL.

Un procedimiento de procesamiento de una palabra de datos, comprendiendo el procedimiento:

recibir la palabra de datos;

determinar si la palabra de datos tiene un primer ancho o un segundo ancho, siendo el segundo ancho superior al primer ancho; y

tras determinar que la palabra de datos tiene el primer ancho, extender el signo de la palabra de datos para crear una palabra de datos temporal que tiene el segundo ancho;

y caracterizado por

restar un valor de un cómputo provisional de bits de datos de cabeza de la palabra de datos temporal que tiene el segundo ancho para determinar un cómputo final de bits de datos de cabeza

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2006/025300.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE,SAN DIEGO, CALIFORNIA 92121.

Inventor/es: LIANG, JIAN, KOOB,CHRISTOPHER EDWARD.

Fecha de Publicación: .

Fecha Concesión Europea: 3 de Marzo de 2010.

Clasificación Internacional de Patentes:

- G06F7/74 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Selección o codificación dentro de una palabra de la posición de uno o más bits que tengan un valor específico, p.ej detección del más o menos significativo o de cero, codificadores de prioridad.

Clasificación PCT:

- G06F7/74 G06F 7/00 […] › Selección o codificación dentro de una palabra de la posición de uno o más bits que tengan un valor específico, p.ej detección del más o menos significativo o de cero, codificadores de prioridad.

Fragmento de la descripción:

Sistema y procedimiento de cómputo de ceros de cabeza y de cómputo de unos de cabeza en un procesador de señal digital.

I. Campo

La presente memoria descriptiva se refiere en general a procesadores de señal digital y a dispositivos que usan tales procesadores. Más particularmente, la memoria descriptiva se refiere a componentes dentro de un procesador de señal digital que cuentan ceros de cabeza o cuentan unos de cabeza dentro de palabras de datos.

II. Descripción de la técnica relacionada

Los avances en la tecnología han dado como resultado dispositivos de computación personales más pequeños y más potentes. Por ejemplo, actualmente existe una variedad de dispositivos de computación personales portátiles, que incluyen dispositivos de computación inalámbricos, tales como teléfonos inalámbricos portátiles, asistentes digitales personales (PDA) y dispositivos de radiomensajería que son pequeños, ligeros y fácilmente transportables por los usuarios. Más específicamente, los teléfonos inalámbricos portátiles, tales como los teléfonos celulares y teléfonos IP, pueden comunicar paquetes de voz y datos a través de redes inalámbricas. Además, muchos de tales teléfonos inalámbricos incluyen otros tipos de dispositivos que se incorporan en éstos. Por ejemplo, un teléfono inalámbrico también puede incluir una cámara fotográfica digital, una cámara de video digital, un grabador digital y un reproductor de archivos de audio. Asimismo, tales teléfonos inalámbricos pueden incluir una interfaz de web que puede usarse para acceder a Internet. Como tal, estos teléfonos inalámbricos incluyen capacidades competitivas significativas.

Algunos de los programas que proporcionan la funcionalidad de los diferentes dispositivos incorporados dentro de un teléfono inalámbrico incluyen instrucciones que requieren un cómputo de ceros de cabeza o un cómputo de unos de cabeza para palabras de datos particulares. Normalmente, se usan múltiples tamaños de palabra de datos con diferentes programas. Como tal, pueden usarse múltiples componentes de hardware para contar los ceros de cabeza y unos de cabeza dentro de las diferentes palabras de datos.

Por consiguiente sería ventajoso proporcionar un sistema y procedimiento mejorados para contar ceros de cabeza y contar unos de cabeza dentro de un procesador de señal digital. En "ARM DSP-Enhanced Extensions" Hedley Francis, ARM Ltd., se explica la mejora de la arquitectura ARM DSP y ampliaciones de conjuntos de instrucciones que dan a los diseñadores acceso a núcleos incrustados que pueden implementar algoritmos de procesamiento de señales de alto rendimiento sin comprometer el rendimiento de control. Los núcleos ARM 'E' aumentan la flexibilidad y amplían el espacio de aplicación de las soluciones programables. Estas arquitecturas, cuando se implementan como el núcleo de un diseño de sistema monochip, pueden proporcionar una solución óptima a muchos de los algoritmos que surgen que requieren procesamiento pico de alto rendimiento en combinación con capacidad de control compleja. El enfoque de ARM para mejorar la capacidad DSP de sus populares núcleos RISC es equilibrar el aumento de recursos de hardware de modo que se consigue un rendimiento suficiente para muchas operaciones de procesamiento de señal críticas sin aumentos inaceptables en el consumo de área y potencia. Así como una variedad de procesadores IP incrustados líderes en el mercado, ARM proporciona soluciones para desarrollo SoC basado en núcleo, incluyendo un paquete de desarrollo de software incrustado avanzado (ADS) y placas de desarrollo, bloques IP PrimeCell periféricos, y el bus AMBA SoC estándar monochip.

Sumario

Un procedimiento de procesamiento de una palabra de datos se da a conocer en el presente documento con referencia a las reivindicaciones adjuntas e incluye recibir la palabra de datos y determinar si la palabra de datos es una palabra de datos de treinta y dos bits o una palabra de datos de sesenta y cuatro bits. Además, el procedimiento incluye extender el signo de la palabra de datos de treinta y dos bits para crear una palabra de datos de sesenta y cuatro bits temporal tras determinar que la palabra de datos es una palabra de datos de treinta y dos bits.

En una realización particular, el procedimiento puede incluir determinar si va a determinarse un valor de ceros de cabeza o un valor de unos de cabeza. Asimismo, en una realización particular, el procedimiento puede incluir comunicar la palabra de datos de sesenta y cuatro bits temporal a un contador de bits que tiene un ancho de sesenta y cuatro bits tras determinar que va a determinarse el valor de ceros de cabeza. Además, en una realización particular, el procedimiento puede incluir contar los ceros de cabeza dentro de la palabra de datos de sesenta y cuatro bits temporal para generar un cómputo de ceros de cabeza de signo extendido, restar un valor fijo de treinta y dos del cómputo de ceros de cabeza de signo extendido, siempre que el cómputo no sea cero, para generar un cómputo de ceros de cabeza determinado, y escribir el cómputo de ceros de cabeza determinado en un registro.

En otra realización particular, el procedimiento puede incluir invertir la palabra de datos de sesenta y cuatro bits temporal para crear una palabra de datos de sesenta y cuatro bits invertida cuando va a determinarse un valor de unos de cabeza. Asimismo, en una realización particular, el procedimiento puede incluir comunicar la palabra de datos de sesenta y cuatro bits temporal invertida a un contador de bits con un ancho de sesenta y cuatro bits, contar los ceros de cabeza dentro de la palabra de datos de sesenta y cuatro bits temporal invertida para generar un cómputo de unos de cabeza de signo extendido, restar el valor fijo de treinta y dos del cómputo de unos de cabeza de signo extendido, siempre que el cómputo no sea cero, para generar un cómputo de unos de cabeza determinado, y escribir el cómputo de unos de cabeza determinado en un registro.

En otra realización particular, el procedimiento puede incluir además determinar si va a usarse un valor de ceros de cabeza o un valor de unos de cabeza, tras determinar que la palabra de datos es una palabra de datos de sesenta y cuatro bits. De manera adicional, en una realización particular, el procedimiento puede incluir comunicar la palabra de datos de sesenta y cuatro bits a un contador de bits con un ancho de sesenta y cuatro bits tras determinar que va a usarse el valor de ceros de cabeza, contar los ceros de cabeza dentro de la palabra de datos de sesenta y cuatro bits para ge- nerar un cómputo de ceros de cabeza determinado, y escribir el cómputo de ceros de cabeza determinado en un registro.

En otra realización particular más, el procedimiento puede incluir invertir la palabra de datos de sesenta y cuatro bits para crear una palabra de datos de sesenta y cuatro bits invertida cuando va a usarse un valor de unos de cabeza, comunicar la palabra de datos de sesenta y cuatro bits invertida a un contador de sesenta y cuatro bits, contar los ceros de cabeza dentro de la palabra de datos de sesenta y cuatro bits invertida para generar un cómputo de unos de cabeza determinado, y escribir el cómputo de unos de cabeza determinado en un registro.

En otra realización, se da a conocer un procedimiento y puede incluir usar un contador de bits con un ancho de sesenta y cuatro bits para contar uno o más ceros de cabeza dentro de una palabra de datos de treinta y dos bits.

En otra realización más, se da a conocer una unidad de ejecución de instrucciones para un procesador de señal digital y puede incluir un módulo de control, un extensor de signo que está acoplado al módulo de control, un inversor que está acoplado al módulo de control, y un contador de bits con un ancho de sesenta y cuatro bits que está acoplado al módulo de control. En esta realización, el módulo de control puede incluir lógica para indicar al contador de bits que cuente los ceros de cabeza dentro de una o más palabras de datos de treinta y dos bits recibidas en la unidad de ejecución de instrucciones y lógica para indicar al contador lógico de sesenta y cuatro bits que cuente los ceros de cabeza dentro de una o más palabras de datos de sesenta y cuatro bits recibidas en la unidad de ejecución de instrucciones.

En otra realización más, se proporciona un procesador de señal digital e incluye una memoria, un secuenciador que es sensible a la memoria, un archivo de registro que está acoplado a la memoria, y una unidad de ejecución de instrucciones que es sensible al secuenciador. En esta realización, la unidad de ejecución...

Reivindicaciones:

1. Un procedimiento de procesamiento de una palabra de datos, comprendiendo el procedimiento:

2. El procedimiento según la reivindicación 1, en el que el primer ancho es treinta y dos bits y el segundo ancho es sesenta y cuatro bits, en el que el cómputo provisional indica ceros de cabeza y en el que el valor que se resta del cómputo provisional, siempre que el cómputo provisional no sea cero, es un valor fijo.

3. El procedimiento según la reivindicación 2, en el que el valor fijo es treinta y dos.

4. El procedimiento según la reivindicación 2, que comprende además escribir el cómputo final en un registro.

5. El procedimiento según la reivindicación 1, que comprende además invertir la palabra de datos que tiene el segundo ancho para crear una palabra de datos invertida que tiene el segundo ancho cuando va a determinarse un valor de unos de cabeza.

6. El procedimiento según la reivindicación 4, que comprende además comunicar la palabra de datos invertida que tiene el segundo ancho a un contador de bits que tiene el segundo ancho.

7. El procedimiento según la reivindicación 1, en el que el primer ancho es treinta y dos bits y el segundo ancho es sesenta y cuatro bits, en el que el cómputo provisional indica unos de cabeza y en el que el valor que se resta del cómputo provisional, siempre que el cómputo provisional no sea cero, es un valor fijo.

8. El procedimiento según la reivindicación 7, que comprende además escribir el cómputo final en un registro.

9. El procedimiento según la reivindicación 1, que comprende además determinar si va a usarse un valor de ceros de cabeza o un valor de unos de cabeza, tras determinar que la palabra de datos tiene el segundo ancho.

10. El procedimiento según la reivindicación 9, que comprende además:

11. El procedimiento según la reivindicación 9, que comprende además:

12. El procedimiento según la reivindicación 1, que comprende además:

13. El procedimiento según la reivindicación 12, que comprende además contar los ceros de cabeza de la palabra de datos temporal invertida del segundo ancho para obtener un segundo resultado provisional.

14. El procedimiento según la reivindicación 13, que comprende además restar un valor fijo del segundo resultado provisional, siempre que el cómputo de los ceros de cabeza no sea cero, para obtener un segundo resultado final.

15. El procedimiento según la reivindicación 7 o la reivindicación 14, en el que el valor fijo es treinta y dos.

16. El procedimiento según la reivindicación 15, que comprende además escribir el segundo resultado final en un registro como un valor de unos de cabeza.

17. El procedimiento según la reivindicación 1, en el que el primer ancho es 2 a la potencia N y el segundo ancho es 2 a la potencia M y el valor es igual a 2 a la potencia M menos 2 a la potencia N.

18. El procedimiento según la reivindicación 17, que comprende además establecer el cómputo igual a cero cuando el resultado es cero.

19. El procedimiento según la reivindicación 17, que comprende además contar los ceros de cabeza dentro de la palabra de datos temporal para obtener un resultado que tiene M+1 bits, en el que el resultado incluye un bit cero como el bit menos significativo, un bit M como el bit más significativo, y un bit N entre el bit cero y el bit M.

20. El procedimiento según la reivindicación 17, que comprende además: copiar el bit M en la ubicación del bit N; y sustituir desde el bit M hasta el bit N + 1 por cero.

21. Un dispositivo procesador configurado para procesar una palabra de datos, que comprende:

22. El dispositivo procesador según la reivindicación 21, en el que el primer ancho es 2 a la potencia N y el segundo ancho es 2 a la potencia M y el valor es igual a 2 a la potencia M menos 2 a la potencia N.

23. El dispositivo según la reivindicación 22, que comprende además medios para establecer el cómputo igual a cero cuando el resultado es cero.

24. El dispositivo según la reivindicación 22, en el que el resultado tiene M+I bits y en el que el resultado incluye un bit cero como el bit menos significativo, un bit M como el bit más significativo, y un bit N entre el bit cero y el bit M.

25. El dispositivo según la reivindicación 24, que comprende además: medios para copiar el bit M en la ubicación de bit N; y medios para sustituir desde el bit M hasta el bit N + 1 por cero.

26. Una unidad de ejecución de instrucciones para un procesador de señal digital, comprendiendo la unidad de ejecución de instrucciones:

27. La unidad de ejecución de instrucciones según la reivindicación 26, en la que el módulo de control comprende además lógica para controlar el inversor para invertir la palabra de datos de sesenta y cuatro bits temporal para producir una palabra de datos de sesenta y cuatro bits temporal invertida.

28. La unidad de ejecución de instrucciones según la reivindicación 27, en la que el módulo de control comprende además lógica para indicar al contador de bits de sesenta y cuatro bits de ancho que cuente los ceros de cabeza de la palabra de datos de sesenta y cuatro bits temporal invertida para obtener un cómputo de unos de cabeza provisional.

29. La unidad de ejecución de instrucciones según la reivindicación 28, en la que el módulo de control comprende además lógica para restar un valor fijo del cómputo de unos de cabeza provisional, siempre que el cómputo de los ceros de cabeza de la palabra de datos de sesenta y cuatro bits temporal invertida no sea cero, para obtener un cómputo de unos de cabeza final.

30. Un procesador de señal digital, que comprende: la unidad de instrucción según cualquiera de las reivindicaciones 26 a 29 y que comprende además

31. Un dispositivo (820) de comunicación portátil, que comprende el procesador de señal digital según la reivindicación 30 y que comprende además:

32. El dispositivo de comunicación portátil según la reivindicación 31, en el que el procesador (926) de banda base incluye un procesador (926) de banda base analógico, en el que el CODEC incluye un CODEC (950) de audio estéreo y en el que la antena está acoplada al transceptor RF a través de un conmutador (970) RF.

33. El dispositivo de comunicación portátil según la reivindicación 31, en el que el CODEC incluye un CODEC (1022) de voz, en el que el procesador de banda base incluye un procesador (1030) de banda base de control de acceso al medio de red de área local (WLAN MAC) y que comprende además;

34. El dispositivo de comunicación portátil según la reivindicación 31, en el que el CODEC incluye un CODEC estéreo y que comprende además:

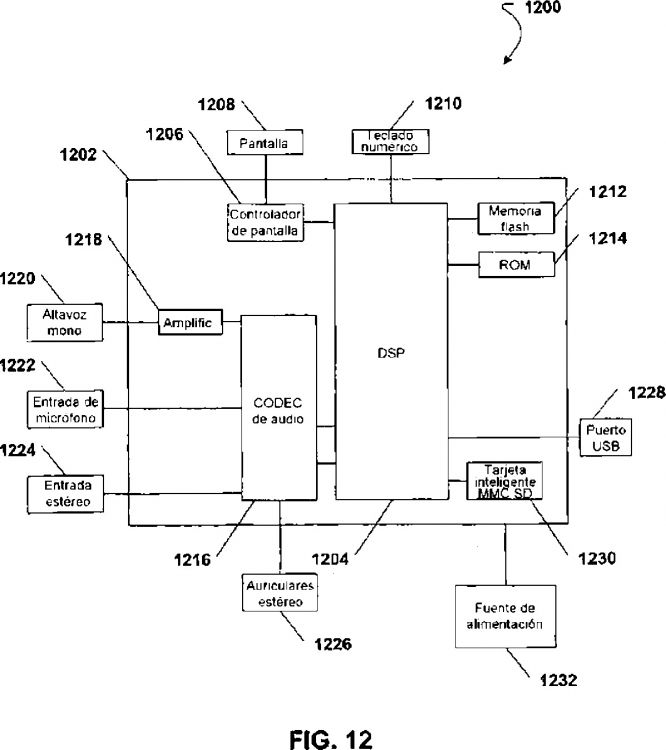

35. Un reproductor (1200) de archivos de audio, que comprende: