Un sistema y un método para generar un voltaje de error.

Método para generar un voltaje de error (Verr) a través de un condensador de acoplamiento (CC) en un dispositivo de circuito de conmutación y para amplificar e integrar dicho voltaje de error (Verr),

siendo usado dicho método en un sistema que comprende el dispositivo de circuito de conmutación y un generador de reloj (CGEN) para controlar el dispositivo de circuito de conmutación, dicho dispositivo de circuito de conmutación comprende además un voltaje de referencia (VR), un condensador conmutado (CSW), una corriente de polarización (IBB) para cargar el condensador conmutado (CSW), un amplificador (AMP) para recibir el voltaje de error (Verr) a través del condensador de acoplamiento (CC) y un condensador de integración (CINT) sobre el que integrar el voltaje de error amplificado (Verr), dicho método caracterizado por el hecho de que comprende la ejecución de tres fases sin superposición, es decir una fase de carga (ph1), una fase de agarre (ph2) y una fase de descarga (ph3), donde: durante la fase de carga (ph1) son realizados los siguientes pasos:

- cargar el condensador conmutado (CSW),

- poner a cero automáticamente el amplificador (AMP) por lo cual su entrada está hecha para permanecer en su punto operativo inerte,

durante la fase de agarre (ph2) son realizados los siguientes pasos:

- retener el condensador conmutado (CSW) en un voltaje cargado alcanzado al final de la fase de carga (ph1),

- conectar el condensador conmutado (CSW) al condensador de acoplamiento (CC),

- mantener la configuración de puesta a cero automática del amplificador (AMP),

durante la fase de descarga (ph3) son realizados los siguientes pasos:

- descargar el condensador conmutado (CSW),

- desconectar el condensador conmutado (CSW) del condensador de acoplamiento (CC) y conectar el voltaje de referencia (VR) al condensador de acoplamiento (CC) almacenando así el voltaje de error (Verr) a través del condensador de acoplamiento (CC), siendo dicho voltaje de error (Verr) la diferencia entre el voltaje de referencia (VR) y el voltaje cargado,

- amplificar el voltaje de error (Verr) utilizando el amplificador (AMP) e integrar el voltaje de error amplificado sobre el condensador de integración (CINT) para obtener un voltaje de error amplificado integrado (VINT), siendo dichas tres fases en ciclos consecutivamente en una base continua.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2009/062399.

Solicitante: Moscad Design & Automation Sàrl.

Nacionalidad solicitante: Suiza.

Dirección: Chemin des Curtils 1261 Le Vaud SUIZA.

Inventor/es: BALLENEGGER,FLORIAN.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G05F3/26 FISICA. › G05 CONTROL; REGULACION. › G05F SISTEMAS DE REGULACION DE VARIABLES ELECTRICAS O MAGNETICAS (regulación de la distribución en el tiempo o de la periodicidad de impulsos en los sistemas de radar o de radionavegación G01S; regulación de la corriente o de la tensión, especialmente adaptada para su uso en relojes electrónicos G04G 19/02; sistemas que funcionan en bucle cerrado para regular variables no eléctricas por medios eléctricos G05D; control de la alimentación de energía eléctrica a los computadores digitales G06F 1/26; para obtener las características de funcionamiento deseadas de electroimanes con armadura H01F 7/18; regulación de redes de distribución de energía eléctrica H02J; regulación de la carga de baterías H02J 7/00; regulación del valor de salida de convertidores estáticos, p. ej. reguladores de conmutación, H02M; regulación del valor de salida de generadores eléctricos H02N, H02P 9/00; control de transformadores, reactancias o bobinas de choque H02P 13/00; regulación de la respuesta de frecuencia, ganancia, potencia de salida máxima, amplitud o ancho de banda de amplificadores H03G; regulación de la sintonización de circuitos resonantes H03J; control de generadores de oscilaciones o de impulsos electrónicos H03L; regulación de las características de líneas de transmisión H04B; control de fuentes eléctricas de luz H05B 39/04, H05B 41/36, H05B 45/10, H05B 45/20, H05B 47/10; control eléctrico de aparatos de rayos X H05G 1/30). › G05F 3/00 Sistemas no retroactivos para la regulación de variables eléctricas por utilización de un elemento no controlado, o de una combinación de elementos no controlados, siendo dicho elemento o dicha combinación aptos para ejercer por sí mismos una regulación. › Reflectores de corriente.

- H03F3/00 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03F AMPLIFICADORES (medidas, ensayos G01R; amplificadores ópticos paramétricos G02F; circuitos con tubos de emisión secundaria H01J 43/30; másers, lásers H01S; amplificadores dinamoeléctricos H02K; control de la amplificación H03G; dispositivos para el acoplamiento independientes de la naturaleza del amplificador, divisores de tensión H03H; amplificadores destinados únicamente al tratamiento de impulsos H03K; circuitos repetidores en las líneas de transmisión H04B 3/36, H04B 3/58; aplicaciones de amplificadores de voz a las comunicaciones telefónicas H04M 1/60, H04M 3/40). › Amplificadores que tienen como elementos de amplificación solamente tubos de descarga o solamente dispositivos de semiconductores.

- H03F3/45 H03F […] › H03F 3/00 Amplificadores que tienen como elementos de amplificación solamente tubos de descarga o solamente dispositivos de semiconductores. › Amplificadores diferenciales.

- H03H19/00 H03 […] › H03H REDES DE IMPEDANCIA, p. ej. CIRCUITOS RESONANTES; RESONADORES (medidas, ensayos G01R; disposiciones para producir una reverberación sonora o un eco G10K 15/08; redes de impedancia o resonadores que se componen de impedancias distribuidas, p. ej. del tipo guía de ondas, H01P; control de la amplificación, p. ej. control del ancho de banda de los amplificadores, H03G; sintonización de circuitos resonantes, p. ej. sintonización de circuitos resonantes acoplados, H03J; redes para modificar las características de frecuencia de sistemas de comunicación H04B). › Redes que utilizan elementos diferentes en función del tiempo, p. ej. filtros con N vías.

PDF original: ES-2523445_T3.pdf

Fragmento de la descripción:

Un sistema y un método para generar un voltaje de error

INTRODUCCiÓN

10001J La presente invención se refiere al dominio de circuitos y técnicas de condensador conmutados y más particularmente al uso de tales circuitos en la realización de generadores de corriente de precisión y osciladores de precisión.

ANTECEDENTES DE LA INVENCiÓN

10002j Redes de condensador conmutado son ampliamente usadas en el diseño de circuitos electrónicos en vista de su capacidad para simular una carga resistente en un circuito. Usando un condensador conmutado Csw, accionado a una frecuencia fsw, se puede realizar una resistencia equivalente de Req donde Req=lI (fsw x Csw) . Es bien conocido que en la fabricación de circuitos integrados semiconductores, no es fácilmente alcanzable una precisión absoluta de valores de resistencia mientras que una precisión absoluta de va lores de capacitancia está bien en el conlrol de la mayoría de procesos de fabricación de semiconductor. Por esta razón, el uso de circuitos de condensador conmutados en el diserio de circuito semiconductor analógico, en situaciones donde son requeridos valores de resistencia precisos, es de particular importancia.

10003J Circuitos de referencia de voltaje preciso conocidos como "circuitos de referencia de intervalo de banda" son hoy en día bien conocidos y están ampliamente disponibles. Un ejemplo de tal circuito de referencia de intervalo de banda de precisión es descrito por D. Susak en la Patente Estadounidense Número 5, 900, 773. No obstante, la generación de una referencia de corriente precisa y estable es una tarea más dificil. La disponibilidad de generadores de referencia de corriente de precisión es necesaria para consegu ir exactitud en los sensores que requieren aplicaciones (por ejemplo polarización del elemento Hall) , convertidores de datos (por ejemplo conducción de corriente DAC) , etc.

10004] Tales circuitos de referencia de corriente se pueden realizar utilizando un condensador conmutado, un comparador, una referencia de voltaje y un reloj de referencia en un circuito de bucle cerrado de serial mixta como es descrito en la Publicación de Solicitud de la Patente Estadounidense 2006f0119422A1 , Dispositivo Semiconductor que Incluye Circuito de Control de Corriente de Fuente de Corriente de Referencia, Sakurai et al., Jun. 8, 2006. Este circuito tiene un inconveniente debido a que es sensible al retraso en el comparador, conduciendo así a defectos de exactitud significativos debido a variaciones en el proceso de fabricación, variación de suministro de energía y variaciones de temperatura.

10005] Mientras un circuito de protección análogo basado en condensadores accionados es descrito por Cheol-Min et al. en la Publicación de Solicitud de la Patente Estadounidense nO 2005f0258997 A1 , este circuito proporciona una copia de un voltaje de entrada con una ganancia fija de 1 mientras que un amplificador capaz de ampl ificar e integrar una señal de error diferencial sería requerido resolver el problema de proporcionar un generador de referencia de corriente de precisión.

10006] En la Publicación de Solicitud de la Patente Europea nO 1, 712, 973 A2, Moro et al. se describe un circuito de generación de corriente de polarización constante gm tradicional donde el elemento resistente es directamente sustituido por su red equivalente de condensador conmutado junto con un condensador de protección. El objetivo principal de este circuito no es tanto proporcionar una referencia de corriente absoluta precisa, sino más bien polarizar circuitos análogos para un rendimiento significativamente constante (que depende del gmiC) adaptando la corriente de polarización a variaciones de proceso y de temperatura. Este circuito tiene varias inexactitudes que se describirán a continuación, evitando que este circuito ser útil como un generador de referencia de corriente de precisión alta.

10007J Otro bloque de construcción importante en el diseño de circu ito de serial análoga y mixta es un oscilador. Normalmente, para construir un oscilador preciso, se usaría un resonador de cristal o cerámico. Esto lleva a soluciones pesadas y costosas que no son muy flexibles debido al hecho de que estas normalmente tienen frecuencias programadas que corresponden a la frecuencia de cristales o cerámicas disponibles. Usando una red de condensador conmutado con un oscilador controlable y un separador en una configuración de bucle cerrado puede ser realizado un oscilador muy preciso y flexible. Un ejemplo de tal circuito es descrito por T.R. Viswanathan, S. Murtuza, V.H. Syed y M. Staszel, en "Switched Capacitar Frequency Control Loop", IEEE Joumal of Salid State circuits, Vol. 17, Edición nO 4, agosto 1982, págs. 774-778.

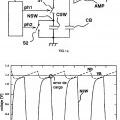

¡0008) La FIG.1a ilustra la manera en la que un condensador conmutado (CSW) y un amplificador (AMP) se usan

generalmente en circuitos inspirados por el trabajo de Viswanathan et al. para obtener un voltaje deseado a través del condensador conmutado (CSW) , y así fluye la corriente deseada. En este circu ito, un condensador conmutado (CSW) se usa en un circuito de realimentación con un amplificador operativo (AMP) configurado para responder a la diferencia entre un voltaje de referencia (VR) y el voltaje a través de la red de condensador conmutado en el punto NB. La diferencia asl detectada se utiliza para controlar la cantidad de corriente en el condensador conmutado.

10009] El disei'io anterior tiene algunas inexactitudes, las cuales serán ahora descritas con referencia a la onda en la Fig.1b. En una primera fase (ph1) , el condensador conmutado se conecta al amplificador operativo (AMP) . Debido a que la entrada del amplificador operativo (NB) tiene un condensador de protección (CB) conectado en paralelo con el condensador conmutado (CSW) , en el momento en el que el condensador conmutado (CSW) se conecta al amplificador operativo (AMP) , el voltaje en la entrada del amplificador operativo (NB) cae debido a la combinación paralela del condensador conmutado (CSW) y el condensador de protección (CB) . La fuente de corriente (lB) carga el parde condensadores (CSW y CB) hasta el final de la primera fase (ph1) . En una segunda fase (ph2) , el condensador conmutado (CSW) es desvinculado del amplificador operativo (AMP) y es descargado. El resultado es que la entrada de amplificador operativo (NB) está sujeta a una onda de diente de sierra cuya pendiente durante la primera fase (ph1) es ligeramente menor que la pendiente durante la segunda fase (ph2) debido a la capacitancia extra del condensador conmutado (CSW) en la primera fase.

10010J Se puede mostrar que para una operación correcta del circuito anterior, un bucle de regulación que incluye el amplificador operativo (AMP) debe tener un ancho de banda que es significativamente inferior a la frecuencia de conmutación. Bajo estas condiciones, el bucle responde aproximadamente al promedio de tiempo del voltaje diferencial en la entrada del ampl ificador. Así el voltaje medio de tiempo en el nodo NSW se regula a través del bucle de retroalimentación para servir al voltaje de referencia (VR) .

10011) Cabe observar que el condensador conmutado (CSW) se carga hasta el voltaje alcanzado al final de la primera fase (ph1 l, al que nosotros nos referiremos como Vcharge, y luego descargado durante la segunda fase (ph2) . No obstante, debido a que la onda de diente de sierra en el nodo NSW no es perfectamente simétrica, debido a las inclinaciones diferentes durante la primera y segunda fase, el promedio de tiempo real del voltaje en el nodo NSW es mayor que el voltaje alcanzado al final de la primera fase (ph1) por una cantidad positiva no puesta a cero a la que nosotros nos referiremos como un voltaje de offset (Voffsetl. Además, la caída de voltaje a través del interruptor (S1) debido a su resistencia parásita contribuye además al voltaje de offset (Voffset) . Además, cualquier discrepancia de coordinación de tiempo entre la primera y la segunda fase llevará a un ciclo de funcionamiento desequilibrado y contribu irá además al voltaje de offset (Voffset) .

[0012) La carga transferida durante un periodo es igual al Vcharge x CSW, la cual corresponde a una corriente equivalente de I=Vcharge x CSW x fsw donde fsw es la frecuencia de conmutación. Hemos mostrado antes que, una vez se ha conseguido la estabilización del bucle de retroalimentación, Vcharge no es exactamente igual al voltaje de referencia (VR) . Más específicamente Vcharge = VR -Voffsel. Así el flujo de corriente equivalente es I= (VR-Voffset) x CSW x fsw en vez del valor deseado de VRxCSWxfsw. La cantidad de offset (Voffset) depende de las características del interruptor y op-amp, que cambian con... [Seguir leyendo]

Reivindicaciones:

1. Método para generar un voltaje de error (Verr) a través de un condensador de acoplamiento (CC) en un dispositivo de circuito de conmutación y para amplificar e integrar dicho voltaje de error (Verr) , siendo usado dicho 5 método en un sistema que comprende el dispositivo de circuito de conmutación y un generador de reloj (CGEN) para controlar el dispositivo de circuito de conmutación, dicho dispositivo de circuito de conmutación comprende además un voltaje de referencia (VR) , un condensador conmutado (CSW) , una corriente de polarización (188) para cargar el condensador conmutado (CSW) , un amplificador (AMP) para recibir el voltaje de error (Verr) a través del condensador de acoplamiento (CC) y un condensador de integración (CINT) sobre el que integrar el voltaje de error

amplificado (Verr) , dicho método caracterizado por el hecho de que comprende la ejecución de tres fases sin superposición, es decir una fase de carga (ph1) , una fase de agarre (ph2) y una fase de descarga (ph3) , donde:

durante la fase de carga (ph1) son realizados los siguientes pasos:

-cargar el condensador conmutado (CSW) , -poner a cero automáticamente el amplificador (AMP) por lo cual su entrada está hecha para permanecer en su punto operativo inerte,

durante la fase de agarre (ph2) son realizados los siguientes pasos:

- retener el condensador conmutado (CSW) en un voltaje cargado alcanzado al final de la fase de carga (ph1) , -conectar el condensador conmutado (CSW) al condensador de acoplamiento (CC) , -mantener la configuración de puesta a cero automática del amplificador (AMP) ,

durante la fase de descarga (ph3) son realizados los siguientes pasos:

-descargar el condensador conmutado (CSW) , -desconectar el condensador conmutado (CSW) del condensador de acoplamiento (CC) y conectar el voltaje de referencia (VR) al condensador de acoplamiento (CC) almacenando asl el voltaje de error (Verr) a través del

condensador de acoplamiento (CC) , siendo dicho voltaje de error (Verr) la diferencia entre el voltaje de referencia (VR) y el voltaje cargado, -amplificar el voltaje de error (Verr) utilizando el ampl ificador (AMP) e integrar el voltaje de error amplificado sobre el condensador de integración (C1NT) para obtener un voltaje de error amplificado integrado (VINT) ,

siendo dichas tres fases en ciclos consecutivamente en una base continua.

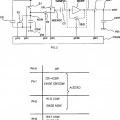

2. Método según la reivindicación 1, donde dicho sistema comprende además un oscilador (XOSC) para manejar el generador de reloj (CGEN) , dicho método comprende además los siguientes pasos:

-controlar la corriente de polarización (IB8) utilizando el voltaje de error amplificado integrado (VINT) .

3. Método según la reivindicación 1, donde dicho circuito de conmutación comprende además un resistor de referencia (RREF) y dicho sistema comprende además un oscilador controlado (ICO) y un divisor de frecuencia (DIV) , comprendiendo dicho método los pasos siguientes:

- forzar una corriente de polarización de referencia (IBR) a través del resistor de referencia (RREF) para generar el voltaje de referencia (VR) , -manejar el oscilador controlado que utiliza el voltaje de error amplificado integrado (VINT) para dar un reloj de salida (CKOUT) ,

-dividir el reloj de salida (CKOUT) por al menos uno, usando el divisor de frecuencia, -manejar el generador de reloj (CGEN) utilizando el reloj de salida dividido.

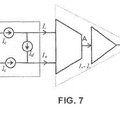

4. Sistema para generar un voltaje de error (Verr) a través de un condensador de acoplamiento (CC) en un dispositivo de circuito de conmutación que comprende un voltaje de referencia (VR) , un condensador conmutado 55 (CSW) , una corriente de polarización (IBB) , un amplificador (AMP) para recibir el voltaje de error (Verr) a través del condensador de acoplamiento (CC) , un condensador de integración (C1NT) sobre el que integrar el voltaje de error amplificado, y una pluralidad de interruptores configurados para permitir:

que el condensador conmutado (CSW) sea cargado por la corriente de polarización (IB8) o sujetado en una 60 presente carga o descargado, que el condensador conmutado (CSW) o el voltaje de referencia sea conectado al condensador de acoplamiento (CC) , que el amplificador (AMP) sea puesto a cero automáticamente, por el cual su entrada está hecha para permanecer en su punto operativo inerte, o para amplificar el voltaje de error (Verr) ,

y que la salida del amplificador (AMP) sea conectada o desconectada del condensador de integración (C1NT) ,

comprendiendo dicho sistema además un generador de reloj (CGEN) , dicho sistema caracterizado por el hecho de que dicho generador de reloj se configura para controlar dicho circuito cíclicamente a través de tres fases sin superposición, es decir una fase de carga (ph1) , una fase de agarre (ph2) y una fase de descarga (ph3) , donde:

-durante la fase de carga (ph1) el condensador conmutado (CSW) se carga a través de la corriente de polarización (IBB) y el amplificador (AMP) es puesto a cero automáticamente por lo cual su entrada está hecha para permanecer en su punto operativo inerte, -durante la fase de agarre (ph2) la carga del condensador conmutado (CSW) es cesada, reteniendo as1 el condensador conmutado a un voltaje cargado, el condensador conmutado (CSW) se conmuta en el condensador de acoplamiento (CC) y la condición de puesta a cero del amplificador (AMP) es mantenida, -durante la fase de descarga (ph3) el condensador conmutado (CSW) es descargado, el voltaje de referencia (VR) se acciona sobre el condensador de acoplamiento (CC) , almacenando así el voltaje de error (Verr) a través del condensador de acoplamiento (CC) , dicho voltaje de error (Verr) siendo la diferencia entre el voltaje de referencia (VR) y el voltaje cargado, el voltaje de error (Verr) se amplifica por el amplificador (AMP) y el voltaje de error amplificado se integra sobre el condensador de integración (C1NT) para dar un voltaje de error amplificado integrado (VINT) .

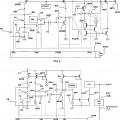

5. Sistema según la reivindicación 4, donde el circuito de conmutación comprende además un condensador de protección (CS) desviado por la corriente de polarización (lBS) en una manera continua.

6. Sistema según cualquiera de las reivindicaciones 4 o 5, donde dicho amplificador (AMP) comprende un elemento de amplificación (MAMP) , dicho elemento de amplificación (MAMP) siendo un transistor MOS tipo N polarizado por una corriente de polarización amplificadora (ISA) , dicha puesta a cero automática siendo conseguida conectando la salida del amplificador a su entrada.

7. Sistema según cualquiera de las reivindicaciones de 4 a 6, donde dicho dispositivo de circuito de conmutación comprende además un conductor de salida para convertir el voltaje de error amplificado integrado (VINT) a una corriente de salida (tOUT) , un generador de voltaje de referencia de intervalo de banda (BG) para generar dicho voltaje de referencia (VR) y un oscilador (XOSC) para manejar el generador de reloj (CGEN) , dicha corriente de salida (IOUT) siendo usada en una configuración de espejo de corriente para controlar la corriente de polarización (IBB) y la corriente de polarización amplificadora (IBA) .

8. Sistema según cualquiera de las reivindicaciones de 4 a 7, donde el dispositivo de circuito de conmutación comprende además una fase cascode plegable (FASC) conectada entre la salida del amplificador y el condensador de integración (CINT) para reducir la sensibilidad de la corriente de salida (IOUT) a la onda de suministro de energía.

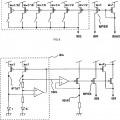

9. Sistema según la reivindicación 6, donde el voltaje de referencia (VR) se genera forzando una corriente de polarización de referencia (IBR) a través de una resistencia de referencia (RREF) , dicha corriente de polarización de referencia (ISR) siendo relacionada con la corriente de polarización (lBS) a través de una configuración de espejo de corriente, y donde dicho dispositivo de circuito de conmutación comprende además un conductor de salida para convertir el voltaje de error amplificado integrado (VINT) en una corriente de salida (IOUT) y para generar la corriente de polarización del amplificador (IBA) proporcional a la corriente de salida (IOUT) utilizando una configuración de espejo de corriente, dicho sistema comprende además un oscilador de corriente controlado (ICO) y un separador de reloj (DIV) , dicho oscilador de corriente controlado (ICO) siendo manejado por la corriente de salida (tOUT) para dar un reloj de salida (CKOUT) , comprendiendo dicha configuración de retroalimentación el uso de la salida de separador de reloj para controlar el generador de reloj (CGEN) .

10. Sistema según cualquiera de las reivindicaciones de 4 a 9, donde dicho circuito de conmutación comprende además un circuito de puesta en marcha (START) para asegurar que dicha corriente de salida (IOUT) no es puesta a cero por inyección de una corriente de puesta en marcha sobre el condensador de integración (CINT) .

11. Sistema según cualquiera de las reivindicaciones de 4 a 10, donde al menos uno de los condensadores en el circuito de conmutación está al menos parcialmente hecho de una capacitancia parásita.

12. Sistema según cualquiera de las reivindicaciones de 9 a 11, donde dicho dispositivo de circuito de conmutación comprende un sistema para compensar por variaciones en resistividad de la resistencia de referencia (RREF) , dicho sistema de compensación comprendiendo al menos una de las siguientes provisiones:

-la resistencia de referencia (RREF) comprende una pluralidad de secciones resistentes cada una asociada al menos con un interruptor programable para permitir que dicha sección resistente participe en o sea excluida de la resistencia total de dicha resistencia de referencia (RREF) , -el condensador conmutado (CSW) comprende una pluralidad de secciones capacitivas cada una asociada al menos con un interruptor programable para permitir que dicha sección capacitiva participe en o sea exduida de la capacitancia total de dicho condensador conmutado (CSW) , -al menos una derivación de cualquiera de las configuraciones de espejo de corriente comprende al menos un transistor y una pluralidad de secciones paralelas de transistor, cada una de dichas secciones de transistor

siendo conectada a través de un interruptor programable a dicha derivación para permitir que dicha sección sea incluida en o sea excluida de dicha derivación.

13. Sistema según la reivindicación 4, donde dicho dispositivo de circuito de conmutación comprende además un sistema para compensar por variaciones en el valor de la resistencia de referencia (RREF) y/o por variaciones en el valor del condensador conmutado (CSW) debido a variaciones en la temperatura, dicho sistema comprendiendo un espejo de corriente de compensación de temperatura para reflejar una proporción de una corriente cuyo valor es proporcional a la temperatura, dicha proporción de corriente siendo usada para ajustar la corriente de polarización (IBB) o la corriente de polarización de referencia (IBR) .

Patentes similares o relacionadas:

Estructura de amplificador de señal para radiotransmisor, del 5 de Junio de 2019, de Nokia Technologies OY: Un método que comprende: proporcionar una estructura de amplificador modular que comprende una pluralidad de subunidades de amplificador […]

Amplificadores de bajo ruido con salidas combinadas, del 8 de Octubre de 2018, de QUALCOMM INCORPORATED: Un aparato que incluye: un módulo delantero , comprendiendo el módulo delantero: una pluralidad de amplificadores de bajo ruido , LNA, que tienen […]

Receptor de bajo ruido de alta linealidad con conmutación de carga, del 28 de Marzo de 2018, de QUALCOMM INCORPORATED: Un aparato que comprende: un amplificador de bajo ruido (LNA) (130, 130a, 130b) configurado para recibir una señal de entrada de LNA y proporcionar al menos una […]

Amplificador de baja disipación, del 3 de Enero de 2018, de THX Ltd: Un sistema de amplificación, que comprende: un primer amplificador operable para recibir una señal de fuente de entrada; un […]

Un circuito que comprende al menos un primer grupo de transistores y un segundo grupo de transistores, del 1 de Julio de 2015, de SAAB AB: Un circuito que comprende una primera parte (1a) y una segunda parte (1b), comprendiendo la primera parte (1a) un primer y un segundo par de transistores con emisores […]

Circuito amplificador para sensores del tipo carga y del tipo corriente, del 3 de Abril de 2013, de AZKOYEN , S.A: Circuito acondicionador y amplificador con entrada diferencial para un sensor generador de carga o decorriente con terminales del sensor adecuado para generar […]

Circuito amplificador para sensores del tipo carga y del tipo corriente, del 3 de Abril de 2013, de AZKOYEN , S.A: Circuito acondicionador y amplificador con entrada diferencial para un sensor generador de carga o decorriente con terminales del sensor adecuado para generar […]

Sistema y procedimiento de reducción de ruido de chasquidos y crepitaciones en dispositivos de reproducción de audio, del 19 de Septiembre de 2012, de QUALCOMM INCORPORATED: Un sistema de audio que comprende: un medio para amplificar una señal de audio de entrada para generar una señal de audio de salida; y un […]

ANTENA SUBMARINA CON AL MENOS UN HIDRÓFONO Y CON UN CIRCUITO DE AMPLIFICACIÓN ELÉCTRICO ASOCIADO AL HIDRÓFONO, del 22 de Febrero de 2012, de ATLAS ELEKTRONIK GMBH: Antena submarina con al menos un hidrófono y con un circuito de amplificación eléctrico simétrico, asociado al hidrófono , cuyo circuito presenta dos […]