SISTEMA INFORMATICO.

EN UN SISTEMA DE ORDENADOR CON UN PROCESADOR RISC (14) QUE UTILIZA INSTRUCCIONES DE 32 BITS,

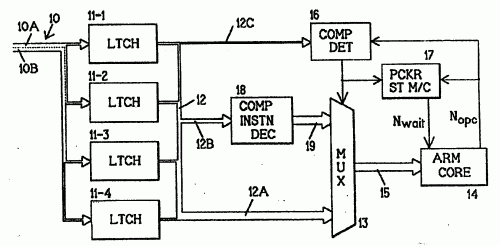

CIERTAS INSTRUCCIONES SE ALMACENAN EN FORMA COMPRIMIDA DE 16 BITS Y SE EXPANDEN PARA SU USO POR EL PROCESADOR, REDUCIENDO EL TIEMPO DE ACCESO. UNA INSTRUCCION ES EXTRAIDA DE LA MEMORIA (POR MEDIO DEL BUS (10)) POR MEDIO DE UN CONJUNTO DE MEMORIAS INTERMEDIAS (11-1 A 11-4) QUE SON CARGADAS SECUENCIALMENTE CON PALABRAS DE 8 O DE 16 BITS. EL FORMATO DE LAS INSTRUCCIONES INCLUYE UN CAMPO DE CONDICION EN SU PRIMERA PALABRA, QUE DEFINE LA CONDICION PARA EJECUTAR LA INSTRUCCION. UN CODIGO NV (=NEVER) EN ESE CAMPO INDICA QUE LA INSTRUCCION NO SE VA A EJECUTAR; ESTE CODIGO (QUE NO SE UTILIZA NORMALMENTE) SE UTILIZA PARA IDENTIFICAR INSTRUCCIONES COMPRIMIDAS. UNA UNIDAD DETECTORA DE INSTRUCCIONES COMPRIMIDAS (18) EXPANDE LA INSTRUCCION COMPRIMIDA; Y EL DETECTOR (18) CONTROLA UN MULTIPLEXOR (13) PARA PASAR CUALQUIERA DE LAS INSTRUCCIONES EXPANDIDAS DESDE EL MISMO O LAS INSTRUCCIONES DE LONGITUD COMPLETA DIRECTAMENTE DESDE LAS MEMORIAS INTERMEDIAS (11-1 A 11-4) AL PROCESADOR (14). UNA UNIDAD DE MAQUINA DE ESTADO EMPAQUETADORA (17) TERMINA EL ACCESO DE LA INSTRUCCION UNA VEZ QUE SE HA ACCEDIDO A SUS 16 BITS.

Tipo: Resumen de patente/invención.

Solicitante: COMMUNICATE LTD.

Nacionalidad solicitante: Reino Unido.

Dirección: THE TECHNOLOGY TRANSFER CENTRE, IMPERIAL COLLEGE, SILWOOD PARK, BUCKHURST ROAD, ASCOT, BERKS SL5 7PW.

Inventor/es: DENMAN, PAUL WILLIAM, 498 STAINES ROAD.

Fecha de Publicación: .

Fecha Solicitud PCT: 5 de Abril de 1995.

Fecha Concesión Europea: 1 de Marzo de 2000.

Clasificación Internacional de Patentes:

- G06F9/30 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

- G06F9/318 G06F 9/00 […] › con extensión o modificación de operaciones.

- G06F9/38 G06F 9/00 […] › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Mónaco, Irlanda, Oficina Europea de Patentes.

Patentes similares o relacionadas:

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]

Aumento de protocolo de coherencia para indicar estado de transacción, del 4 de Diciembre de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método implementado por ordenador para implementar un protocolo de coherencia, comprendiendo el método: enviar , por un procesador (112a) solicitante, […]

Método y aparato para un acceso a memoria basado en hilos en un procesador multihilo, del 11 de Septiembre de 2019, de QUALCOMM INCORPORATED: Método para acceder a una memoria por un procesador multihilo , comprendiendo el método: determinar un identificador de hilo asociado a un […]

Procedimientos y aparatos para predecir la no ejecución de instrucciones de no bifurcación condicional, del 15 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para manejar una instrucción de no bifurcación condicional, que comprende: identificar una instrucción […]

Procesamiento transaccional, del 17 de Abril de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método de controlar la ejecución de una transacción en un entorno informático, comprendiendo el método los pasos de: Iniciar, mediante un procesador, la ejecución […]

Guardar/restablecer registros seleccionados en procesamiento transaccional, del 13 de Marzo de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para facilitar el procesamiento de transacciones dentro de un entorno de computación, comprendiendo dicho método: obtener una instrucción […]