REGISTRO DINAMICO INVERSOR CON MECANISMO DE REDUCCION DE TIEMPO DE MANTENIMIENTO DEPENDIENTE DEL DATO.

Un registro lógico dinámico inversor (300), que comprende:

un par complementario de dispositivos de evaluación (P1,

N2) que responden a una señal de reloj;

una lógica evaluadora (302), acoplada entre dicho par complementario de dispositivos de evaluación en un nodo (307) pre-cargado, configurado para evaluar una función lógica en base a al menos una señal de datos de entrada, en donde dicha función lógica evalúa a cualquiera de entre un primer estado, en el que dicho nodo pre-cargado es mantenido a un primer nivel lógico, y un segundo estado, en el que dicho nodo pre-cargado es mantenido a un segundo nivel lógico;

una lógica de retraso (I1, I2, P3, N3), acoplada a dicha señal de reloj, configurada para generar una señal "kill", en donde dicha señal "kill" es una versión retrasada de dicha señal de reloj, y en donde el retraso entre dichas señales de reloj y "kill" comprende un tiempo de mantenimiento; y

una lógica de enclavamiento (P4, P5, N5, N6), que responde a dichas señales de reloj y "kill" y al estado de dicho nodo pre-cargado, configurada para controlar el estado de un nodo (308) de salida en base al estado de dicho nodo pre-cargado durante un periodo de evaluación entre un flanco operativo de dicha señal de reloj y el siguiente flanco de dicha señal "kill", y configurada para presentar, de otra manera, una condición tri-estado a dicho nodo de salida;

caracterizado porque

dicha lógica de retraso está configurada de manera que el tiempo de mantenimiento es más corto, cuando dicha función lógica evalúa a dicho primer estado y dicho nodo pre-cargado es mantenido en el primer nivel lógico, que cuando dicha lógica evalúa a dicho segundo estado y dicho nodo pre-cargado es mantenido en dicho segundo nivel lógico

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E06250241.

Solicitante: VIA TECHNOLOGIES, INC..

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: 8F, NO.535, CHUNG-CHENG RD, HSIEN-TIEN,TAIPEI 231.

Inventor/es: BERTRAM,RAYMOND A.

Fecha de Publicación: .

Fecha Solicitud PCT: 16 de Enero de 2006.

Fecha Concesión Europea: 25 de Noviembre de 2009.

Clasificación Internacional de Patentes:

- H03K19/096C

Clasificación PCT:

- H03K19/00 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Registro dinámico inversor con mecanismo de reducción de tiempo de mantenimiento dependiente del dato.

Antecedentes de la invención

La presente invención se refiere a funciones de registro y lógica dinámica, y, más particularmente, a un registro lógico dinámico que proporciona salidas registradas para funciones de evaluación lógicas, en las que el tiempo de mantenimiento del registro depende del estado del dato de entrada al registro.

Los circuitos integrados usan un número de registros extraordinario, particularmente los que tienen una arquitectura canalizada síncrona. La lógica de registro se emplea para mantener las salidas de los dispositivos y circuitos durante un periodo de tiempo para que estas salidas puedan ser recibidas por otros dispositivos o circuitos. En un sistema sincronizado, tal como un microprocesador canalizado, los registros se usan para enclavar y mantener las salidas de una etapa canalizada determinada durante un periodo de un ciclo de reloj, de manera que los circuitos de entrada en una etapa subsiguiente puedan recibir las salidas durante ese periodo, mientras que la etapa canalizada determinada está generando concurrentemente nuevas salidas.

En el pasado, ha sido una práctica común preceder y seguir circuitos de evaluación lógicos complejos, tales como multiplexores (muxes) de múltiples entradas, codificadores multi-bit, etc., con registros para mantener las entradas y las salidas de los circuitos de evaluación. Generalmente, estos registros tienen requisitos de tiempo de establecimiento y mantenimiento asociados, que condicionan a los circuitos de evaluación en la etapa precedente. Además, los registros tienen unas características reloj-a-salida correspondientes, que restringen los circuitos de evaluación en las etapas subsiguientes. La "velocidad" de un registro se juzga típicamente en términos de su tiempo dato-a-salida, es decir, la suma de su tiempo de establecimiento y tiempo de reloj-a-salida.

La precedencia y el seguimiento de un circuito de evaluación lógico con circuitos de registro tradicionales introducen retrasos en un sistema canalizado, cuyo efecto acumulativo resulta en velocidades operativas considerablemente más lentas. Más específicamente, una fuente importante de estos retrasos son los requisitos de tiempo de establecimiento que deben ser satisfechos por los circuitos de evaluación lógicos con el fin de asegurar salidas registradas estables. Se desea reducir estos retrasos para proporcionar tiempo adicional en cada etapa y para incrementar, de esta manera, la velocidad global del sistema canalizado. Las técnicas usadas para reducir los retrasos de establecimiento y reloj-a-salida (por ejemplo, configuraciones de tipo dominó) introducen frecuentemente requisitos de tiempo de mantenimiento incrementados. Particularmente, cuando una entrada de datos es sincronizada en estos circuitos de registro, el estado de la entrada de datos debe mantenerse constante durante un periodo de tiempo especificado (es decir, el tiempo de "mantenimiento") antes de que pueda cambiar. Si cambia antes de que expire el tiempo de mantenimiento, entonces es posible una salida registrada incorrecta.

Muchos dispositivos, incluyendo circuitos de tipo dominó convencionales, exhiben un requisito de tiempo de mantenimiento que es aproximadamente la anchura de un pulso de reloj correspondiente. Consecuentemente, para reducir el requisito del tiempo de mantenimiento para un circuito dominó convencional, muchos diseñadores emplean una señal de reloj a impulsos, es decir, una señal de reloj cuyo estado de sincronización (clocking) es de una duración considerablemente corta comparada con su estado de no sincronización (non-clocking). No es infrecuente, en la actualidad, encontrar señales de reloj a impulsos que tienen menos del 10 por ciento de los ciclos de trabajo para sus estados de sincronización correspondientes.

Por consiguiente, también se desea proporcionar un aparato de circuito de evaluación registrado y procedimientos que exhiban requisitos de tiempo de mantenimiento marcadamente reducidos, y que además exhiban requisitos de tiempo de mantenimiento que no dependan de la provisión de una señal de reloj a impulsos correspondiente.

El documento US2004/0113658 describe un registro lógico dinámico en el que un evaluador dinámico evalúa una función lógica basándose en una señal de datos, la evaluación se realiza durante un periodo de evaluación definido por una señal de reloj y una señal de reloj invertida retrasada.

Resumen de la invención

La presente invención, entre otras aplicaciones, está dirigida a resolver los problemas indicados anteriormente y aborda otros problemas, desventajas y limitaciones de la técnica anterior.

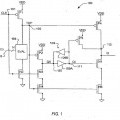

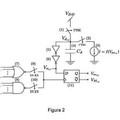

La presente invención proporciona una técnica superior para registrar una función lógica mientras reduce los requisitos de tiempo de mantenimiento. En una realización, se proporciona un registro lógico dinámico inversor. El registro lógico dinámico inversor incluye un par complementario de dispositivos de evaluación, lógica de evaluación, lógica de retraso, y lógica de enclavamiento. El par complementario de dispositivos de evaluación responde a una señal de reloj. La lógica de evaluación está acoplada entre el par complementario de dispositivos de evaluación en un nodo pre-cargado. La lógica de evaluación evalúa una función lógica en base a al menos una señal de datos de entrada, donde la función lógica evalúa a cualquiera de entre un primer estado y un segundo estado. La lógica de retraso está acoplada a la señal de reloj. La lógica de retraso genera una señal "kill", en la que la señal "kill" es una versión retrasada de la señal de reloj, y en la que el retraso entre el reloj y las señales "kill" comprende un tiempo de mantenimiento, y en la que el tiempo de mantenimiento es acortado cuando la función lógica evalúa al primer estado. La lógica de enclavamiento responde al reloj y a las señales "kill" y al estado del nodo pre-cargado. La lógica de enclavamiento controla el estado de un nodo de salida en base al estado del nodo pre-cargado durante un periodo de evaluación entre un flanco operativo de la señal de reloj y el siguiente flanco de la señal "kill", y, por lo demás, presenta una condición tri-estado al nodo de salida.

Un aspecto de la presente invención contempla un circuito de registro dinámico. El circuito de registro dinámico incluye un circuito dinámico, lógica de retraso, un circuito de enclavamiento y un circuito mantenedor. El circuito dinámico pre-carga un primer nodo mientras una señal de reloj está baja, y evalúa una función lógica a cualquiera de entre un primer estado y un segundo estado, y controla el estado del primer nodo cuando la señal de reloj sube. La lógica de retraso recibe la señal de reloj, y proporciona una señal "kill", siendo la señal "kill" una versión retrasada de la señal de reloj, en la que el retraso entre la señal de reloj y la señal "kill" comprende un tiempo de mantenimiento, y en la que el tiempo de mantenimiento es acortado cuando la función lógica evalúa al primer estado. El circuito de enclavamiento está acoplado al circuito dinámico y la lógica de retraso, y está configurado para controlar el estado de un nodo de salida en base al estado del primer nodo durante un periodo de evaluación que empieza cuando la señal de reloj sube y que acaba cuando la señal "kill" sube, y, por lo demás, presenta una condición tri-estado al nodo de salida. El circuito mantenedor está acoplado al nodo de salida.

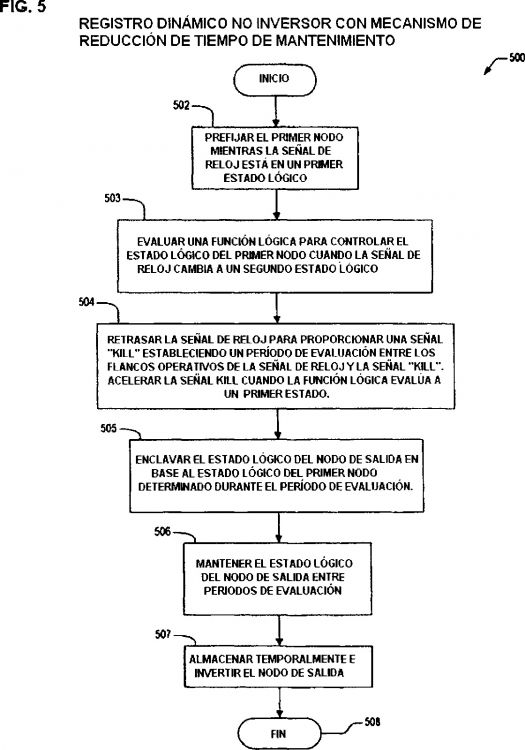

Otro aspecto de la presente invención comprende un procedimiento de registro dinámico de una señal de salida. El procedimiento incluye prefijar un primer nodo mientas una señal de reloj está en un primer estado lógico; evaluar dinámicamente una función lógica a cualquiera de entre un primer estado y un segundo estado para controlar el estado lógico del primer nodo cuando la señal de reloj cambia a un segundo estado lógico; retrasar la señal de reloj y proporcionar una señal "kill", en la que la señal "kill" es una réplica retrasada de la señal de reloj; acelerar la señal "kill" cuando la función lógica evalúa al primer estado; enclavar un estado lógico de un nodo de salida en base al estado lógico del primer nodo determinado durante un periodo de evaluación inicial que empieza cuando la señal de reloj cambia al segundo estado lógico y que acaba con la siguiente transición correspondiente de la señal "kill"; y mantener el estado lógico del nodo de salida entre los...

Reivindicaciones:

1. Un registro lógico dinámico inversor (300), que comprende:

2. Registro lógico dinámico inversor según la reivindicación 1, en el que dicho par complementario de dispositivos de evaluación comprende:

3. Registro lógico dinámico inversor según la reivindicación 1, en el que dicha lógica de evaluación comprende un circuito lógico complejo.

4. Registro lógico dinámico inversor según la reivindicación 1, en el que dicha lógica de retraso comprende un almacenamiento temporal (I1).

5. Registro lógico dinámico inversor según la reivindicación 1, en el que dicha lógica de retraso comprende una cadena de inversores (I1, I2) en serie.

6. Registro lógico dinámico inversor según la reivindicación 1, en el que dicha lógica de retraso comprende un inversor (I2) acoplado a la puerta de un dispositivo de canal-P (P3), configurado para propagar dicha señal "kill" cuando dicha función lógica evalúa a dicho segundo estado y dicho nodo pre-cargado es mantenido en un segundo nivel lógico.

7. Registro lógico dinámico inversor según la reivindicación 1, en el que dicha lógica de retraso comprende un dispositivo de paso de canal-N (N3), configurado para acortar dicho tiempo de mantenimiento cuando dicha función lógica evalúa a dicho primer estado y dicho nodo pre-cargado es mantenido en un primer nivel lógico.

8. Registro lógico dinámico inversor según la reivindicación 1, en el que dicha lógica de enclavamiento comprende:

9. Registro lógico dinámico inversor según la reivindicación 1, que comprende además un inversor (I5) de salida que tiene una entrada acoplada a dicho nodo de salida y una salida acoplada a un nodo (315) de salida invertida.

10. Registro lógico dinámico inversor según la reivindicación 1, que comprende además un circuito (311) mantenedor, acoplado a dicho nodo de pre-carga, y configurado para preservar el estado de dicho nodo de pre-carga a dicho segundo nivel lógico cuando dicha lógica de evaluación evalúa dicha función lógica a dicho segundo estado durante dicho periodo de evaluación y dicha al menos una señal de entrada de datos cambia de estado después de eso.

11. Procedimiento de registro dinámico de una señal de salida, que comprende:

12. Procedimiento según la reivindicación 11, en el que dicha pre-fijación de un primer nodo comprende pre-cargar el primer nodo a un estado lógico alto.

13. Procedimiento según la reivindicación 11, que comprende además almacenar temporalmente e invertir el nodo de salida.

14. Procedimiento según la reivindicación 11, en el que dicho mantenimiento del estado lógico del nodo de salida comprende presentar una condición tri-estado al nodo de salida y acoplar un circuito mantenedor (313) al nodo de salida.

15. Procedimiento según la reivindicación 11, en el que dicha aceleración comprende:

acortar el tiempo de retraso entre la señal de reloj y la señal "kill".

Patentes similares o relacionadas:

CIRCUITO DE ENGANCHE DE SALIDA DOMINÓ N, del 23 de Diciembre de 2011, de VIA TECHNOLOGIES, INC.: Un circuito de enganche dominó N que comprende: una etapa dominó (P1, N2, 301) acoplada a una señal (CLK) de reloj aproximadamente simétrica, y para evaluar una función […]

REGISTRO DE TIPO DOMINÓ P, del 25 de Mayo de 2011, de VIA TECHNOLOGIES, INC.: Registro de tipo dominó P, que comprende: una etapa dominó, acoplada a una señal de impulsos de reloj, y destinada a evaluar una función lógica según […]

REGISTRO DE TIPO DOMINÓ P, del 25 de Mayo de 2011, de VIA TECHNOLOGIES, INC.: Registro de tipo dominó P, que comprende: una etapa dominó, acoplada a una señal de impulsos de reloj, y destinada a evaluar una función lógica según […]

Sistema y procedimiento de control de distribución de energía de un circuito integrado, del 6 de Mayo de 2020, de QUALCOMM INCORPORATED: Un circuito integrado de administración de energía que comprende: un primer pin para suministrar energía a un primer dominio de energía de un dispositivo […]

Aplicación de un lenguaje cuaternario para ordenador, del 14 de Febrero de 2017, de PORRAS VILA,F. JAVIER: La aplicación de un lenguaje cuaternario para ordenador, es un sistema básico de hardware que cada letra del teclado de un ordenador, multiplicará por cuatro para significar […]

Un labio de cuchara para una excavadora, del 7 de Septiembre de 2016, de ESCO CORPORATION: Un labio de cuchara que comprende: Una cara interior posicionada dentro de una cavidad de recogida de tierra de una cuchara de excavadora; Una cara […]

Conjunto de desgaste para el borde de excavación de una excavadora, del 8 de Junio de 2016, de ESCO CORPORATION: Un elemento de desgaste para acoplarse a lo largo del labio de una cuchara, comprendiendo el elemento de desgaste : Un extremo de trabajo frontal ; […]

Dispositivo para interconexionar una línea de bus bidireccional de tipo I2C, del 21 de Enero de 2015, de INDESIT COMPANY S.P.A.: Dispositivo para la interconexión a una línea de bus bidireccional de tipo IIC, que comprende: - una primera patilla (IIC_uC) adaptada para ser conectada […]

Dispositivo para la detección Hardware de extremos locales en una imagen, del 12 de Mayo de 2014, de UNIVERSIDAD DE SEVILLA: Dispositivo y método para la detección hardware de extremos locales en una imagen que comprende una pluralidad de celdas elementales de procesamiento de señal mixta interconectadas […]

Dispositivo para la detección Hardware de extremos locales en una imagen, del 12 de Mayo de 2014, de UNIVERSIDAD DE SEVILLA: Dispositivo y método para la detección hardware de extremos locales en una imagen que comprende una pluralidad de celdas elementales de procesamiento de señal mixta interconectadas […]