Puerto de procesadores múltiples.

Puerto de procesadores múltiples para varios buses en serie (3),

que transmiten datos en paquetes, en el que elpuerto de procesadores múltiples (1) presenta

(a) varios módulos de comunicación (2), que están previstos, respectivamente, para la conexión de un bus en serie (3);

(b) varios procesadores (4) para el procesamiento de datos, que son transmitidos por palabras a través de unsistema de bus interno (5), que pertenece al procesador (4) respectivo, entre el procesador (4) y los módulos decomunicaciones (3);

(c) caracterizado porque buses internos del sistema (5) del puerto (1) de varios procesadores están conectados enlos módulos de comunicaciones (2), que presentan, respectivamente, para cada bus del sistema (5) una unidad deinterfaz (2A, 2B) correspondiente;

(d) en el que cada procesador (4) intercambia datos a través de su sistema de bus (5) correspondiente y a través dela unidad de interfaz, que corresponde al bus del sistema, de un módulo de comunicación (2), independientementede los restantes procesadores (4) con el bus en serie (3), conectado en el módulo de comunicación (2), sin tiempode espera.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2007/053732.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20 70442 STUTTGART ALEMANIA.

Inventor/es: IHLE,MARKUS, TAUBE,JAN, LORENZ,TOBIAS, BLEECK,STEFAN.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F13/40 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › Estructura del bus.

PDF original: ES-2427827_T3.pdf

Fragmento de la descripción:

Puerto de procesadores múltiples La invención se refiere a un puerto de procesadores múltiples para varios buses en serie, que transmiten datos en paquetes.

La interconexión de aparatos de control, instalaciones de sensores e instalaciones de actuadores con la ayuda de una red o bien de un sistema de comunicación, que está constituido por una conexión de comunicación, en particular un bus, y módulos de comunicación correspondientes, se ha incrementado drásticamente en los últimos años en la construcción de automóviles modernos o también en la construcción de máquinas, especialmente en el sector de máquinas herramientas o también en la automatización. En este caso se pueden conseguir efectos de sinergia a través de la distribución de funciones sobre varios usuarios, en particularmente aparatos de control. A este respecto se habla de sistemas distribuidos. Tales sistemas distribuidos o redes están constituidos, por lo tanto, por los usuarios y por el sistema de bus que conecta estos usuarios o por varios sistemas de bus de conexión. La comunicación entre diferentes estaciones o bien usuarios tiene lugar cada vez más a través de un sistema de comunicación, un sistema de bus o una red de este tipo, a través de la cual se trasmiten los datos a transmitir en mensajes o envíos. Este tráfico de la comunicación sobre el sistema de bus, los mecanismos de acceso y de recepción así como el tratamiento de errores son regulados a través de un protocolo correspondiente, en el que el nombre del protocolo respectivo se utiliza también aquí como sinónimo de la red o bien del sistema de bus.

Por ejemplo, en el sector del automóvil se ha establecido como protocolo el Bus CAN (Controller Area Network) .Éste es un protocolo controlado por eventos, es decir, que las actividades del protocolo como la emisión de un mensaje son iniciadas a través de eventos, que tienen su origen fuera del sistema de comunicación. El acceso unívoco al sistema de comunicación o bien al sistema de bus se soluciona a través de un arbitraje binario basado en prioridad. Una condición previa para ello es que se asocie una prioridad a los datos a transmitir y, por lo tanto, a cada mensaje. El protocolo CAN es muy flexible; por lo tanto, la adición de otro usuario y de mensajes es posible sin problemas, con tal que existan todavía prioridades libres (identificadores de mensajes) . La acumulación de todos los mensajes a enviar en la red con prioridades y sus usuarios emisores o bien receptores o bien los módulos de comunicación correspondientes son depositados en una lista, la llamada matriz de comunicación.

Un principio alternativo para la comunicación espontánea, controlado por evento, es el principio puramente controlado por tiempo. Todas las actividades de comunicación sobre el bus son estrictamente periódicas. Las actividades de protocolo como la emisión de un mensaje son activadas solamente por el progreso de un tiempo válido para el sistema de bus. El acceso a este medio se basa en la distribución de divisiones de tiempo, en las que un emisor tiene derecho exclusivo de emisión. En este caso, la secuencia de mensajes se puede establecer, en general, ya antes de la puesta en servicio. Por lo tanto, se crea un itinerario, que cumple los requerimientos de los mensajes en lo que se refiere a tasas de repetición, redundancia, fecha límite, etc. Se habla del llamado programa del bus. Tal sistema de bus es, por ejemplo, el TTP/C.

Una combinación de las ventajas de ambos tipos de bus mencionados se lleva a cabo en el principio de solución del CAN controlado por tiempo, del llamado TTCAN (Time Triggered Controller Area Network) . Éste cumple los requerimientos esbozados anteriormente de la comunicación controlada en el tiempo así como los requerimientos de una cierta medida de flexibilidad. El TTCAN cumple esto a través de la estructura de las rondas de comunicación en las llamadas ventanas de tiempo exclusivas para mensajes periódicos de terminados usuarios de la comunicación y en las llamadas ventanas de tiempo de arbitraje para mensajes espontáneos de varios usuarios de la comunicación. TTCAN se basa en este caso esencialmente en una comunicación periódica controlada en el tiempo, que es sincronizada a través de un usuario o bien módulo de comunicación emisor de tiempo principal, el llamado maestro de tiempo con la ayuda de un mensaje de referencia de tiempo.

Otra posibilidad para combinar diferentes tipos de transmisión ofrece el protocolo FlexRay, con el que se describe un sistema de bus rápido, determinista y tolerante de errores, especialmente para el empleo en un automóvil. Este protocolo trabaja según el procedimiento de Acceso Múltiple por División de Tiempo (TDMA) , en el que se signan a los usuarios o bien a los mensajes a transmitir unas divisiones de tiempo fijas, en las que tienen un acceso exclusivo a la conexión de comunicación, al bus. Las divisiones de tiempo se repiten en este caso en un ciclo establecido, de manera que el instante, en el que se transmite un mensaje a través del bus, se puede predecir con exactitud y el acceso al bus se realiza de forma determinista. Para aprovechar de una manera óptima la anchura de banda para la transmisión del mensaje sobre el sistema de bus, se divide el ciclo en una parte estática y una parte dinámica. Las divisiones de tiempo fijas se encuentran en este caso en la parte estática al comienzo de un ciclo del bus. En la parte dinámica se predeterminan de forma dinámica las divisiones de tiempo. En ellas se posibilita ahora el acceso exclusivo al bus en cada caso solamente durante un tiempo corto, siendo liberado el acceso para el usuario siguiente. Este periodo de tiempo se designa como minidivisión, en la que se espera el acceso del primer usuario.

Como se acaba de representar, existe una pluralidad de técnicas de transmisión diferentes y, por lo tanto, de tipos de sistemas de bus o redes. Es frecuencia que varios sistemas de bus del mismo o de diferente tipo deban ser conectados entre sí. A tal fin, sirve una unidad de interfaz, un llamado puerto. Por lo tanto, un puerto es una interfaz entre diferentes buses, que pueden ser del mismo o de diferente tipo, transmitiendo el puerto mensajes desde un bus sobre uno u otros varios buses. Los puertos conocidos están constituidos por varios módulos de comunicación independientes, siendo realizado el intercambio de mensajes en este caso a través de la interfaz de procesador (interfaz CPU) del usuario respectivo o bien del módulo de interfaz correspondiente del módulo de comunicación respectivo. En este caso, esta interfaz de CPU es cargada fuertemente a través de este intercambio de datos adicionalmente a los mensajes a transmitir hacia el propio usuario, con lo que resulta junto con la estructura de transmisión que resulta de ello una velocidad de transmisión relativamente baja. Además, existen controladores de comunicación o módulos de comunicación integrados, que dividen una memoria de mensajes común, la llamada memoria de mensajes o bien RAM de mensajes para compensar de esta manera los inconvenientes de la estructura. Sin embargo, tales módulos de comunicación integrados son de esta manera muy insensibles con respecto a la transmisión de datos y están establecidos para un número determinado de conexiones de bus y la mayoría de las veces también para el mismo sistema de bus.

La solicitud de patente DE 10 2004 033761 A1 publica un dispositivo para el intercambio de datos con al menos dos sistemas de bus, en el que está contenido un puerto, que presenta al menos dos unidades de control, que procesan funciones relacionadas con interfaces paralelamente al intercambio de datos. El número de las unidades de control corresponde en este caso al número de los sistemas de bus de datos, que intercambian datos entre sí.

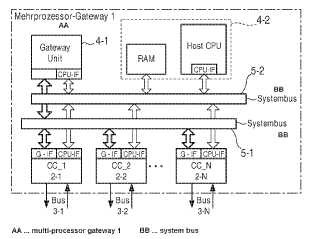

La figura 1 muestra un sistema de bus de acuerdo con el estado de la técnica. El sistema de bus contiene varios módulos de comunicación o bien Controladores de la Comunicación (CC) , en los que se pueden conectar los buses de datos en serie. El puerto de varios procesadores representado en la figura 1 contiene un bus del sistema interno y un bus de la periferia, respectivamente, en los que están conectados, además de los módulos de la comunicación, una unidad CPU y una llamada unidad de puerto, que representa un segundo procesador. La comunicación dentro del puerto de varios procesadores se realiza de acuerdo con el principio maestro/subordinado, de manera que los módulos de comunicación trabajan como unidades subordinadas y la unidad de CPU así como la unidad de puerto funcionan como unidades maestras. Los módulos de comunicación no inician en este caso como unidades subordinadas ellas mismas una transferencia de datos, sino solamente a demanda de un maestro.

... [Seguir leyendo]

Reivindicaciones:

1. Puerto de procesadores múltiples para varios buses en serie (3) , que transmiten datos en paquetes, en el que el puerto de procesadores múltiples (1) presenta (a) varios módulos de comunicación (2) , que están previstos, respectivamente, para la conexión de un bus en serie (3) ;

(b) varios procesadores (4) para el procesamiento de datos, que son transmitidos por palabras a través de un sistema de bus interno (5) , que pertenece al procesador (4) respectivo, entre el procesador (4) y los módulos de comunicaciones (3) ;

(c) caracterizado porque buses internos del sistema (5) del puerto (1) de varios procesadores están conectados en los módulos de comunicaciones (2) , que presentan, respectivamente, para cada bus del sistema (5) una unidad de interfaz (2A, 2B) correspondiente;

(d) en el que cada procesador (4) intercambia datos a través de su sistema de bus (5) correspondiente y a través de la unidad de interfaz, que corresponde al bus del sistema, de un módulo de comunicación (2) , independientemente de los restantes procesadores (4) con el bus en serie (3) , conectado en el módulo de comunicación (2) , sin tiempo de espera.

2. Puerto de varios procesadores de acuerdo con la reivindicación 1, en el que cada módulo de comunicación (2) presenta (a1) una unidad de protocolo de la comunicación (2C) conectada en el bus en serie (3) para la conversión entre paquetes de datos (DP) y mensajes (MSG) , que están constituidos en cada caso por varias palabras de datos (DW) ;

(a2) una unidad de transmisión de mensajes (2D) para la transmisión de mensajes (MSG) entre una memoria de mensajes (2E) y la unidad de protocolo de comunicación (2C) así como memorias tampón (2F, 2G) ;

(a3) varias unidades de interfaz (2A, 2B) , que están conectadas, respectivamente, en un bus de sistema (5-1, 5-2) correspondiente del puerto de varios procesadores (1) ;

(a4) en el que cada unidad de interfaz (2A, 2B) está conectada con al menos una memoria tampón (2F, 2G) correspondiente, que memoriza temporalmente un mensaje, en el que se realiza una transmisión de palabras de datos (SW) a través de varios buses del sistema (5-1, 5-2) y sus unidades de interfaz (2A, 2B) correspondientes desde y hacia las memorias tampón (2F, 2G) de las unidades de interfaz al mismo tiempo sin tiempo de espera.

3. Puerto de varios procesadores de acuerdo con la reivindicación 1, en el que el bus en serie (3) es un bus de Ethernet.

4. Puerto de varios procesadores de acuerdo con la reivindicación 1, en el que el bus en serie (3) es un bus de campo.

5. Puerto de varios procesadores de acuerdo con la reivindicación 3, en el que el bus de campo es un bus CAN.

6. Puerto de varios procesadores de acuerdo con la reivindicación 4, en el que el bus de campo es un bus FlexRay.

7. Puerto de varios procesadores de acuerdo con la reivindicación 4, en el que el bus de campo es un bus MOST.

8. Puerto de varios procesadores de acuerdo con la reivindicación 4, en el que el bus de campo es un bus LIN.

9. Puerto de varios procesadores de acuerdo con la reivindicación 1, en el que cada procesador (4) forma un maestro de bus para su bus de sistema (5) correspondiente.

10. Puerto de varios procesadores de acuerdo con la reivindicación 1, en el que los módulos de comunicación (2) forman unidades subordinadas para los buses del sistema (5) .

11. Puerto de varios procesadores de acuerdo con la reivindicación 1, en el que cada bus del sistema (5) presenta un bus de datos, un bus de direcciones y un bus de control.

12. Puerto de varios procesadores de acuerdo con la reivindicación 1, en el que una unidad de procesamiento (4-1) conectada en el bus del sistema (5) está diseñada como procesador, que controla una transferencia de datos entre los buses en serie (3) conectados en los módulos de comunicaciones (2) .

13. Puerto de varios procesadores de acuerdo con la reivindicación 1, en el que una unidad de procesamiento de datos (4-1) conectada en los buses del sistema (5) está diseñada como co-procesador, que controla una transferencia de datos entre los buses en serie (3) conectados en el módulo de comunicaciones (2) .

14. Puerto de varios procesadores de acuerdo con la reivindicación 1, en el que una unidad de procesamiento (4-1) conectada en los buses del sistema (5) está diseñada como Finite State Machine, que controla una transferencia de datos entre los buses en serie (3) conectados en el módulo de comunicaciones (2) .

Patentes similares o relacionadas:

Método y aparato para detectar contrapresión de mensajes, del 8 de Abril de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de detección de contrapresión de paquetes, en donde el método se aplica a un dispositivo que tiene un puerto de Interconexión de […]

Sistema de procesamiento de datos y método de procesamiento de datos, del 1 de Enero de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un sistema de procesamiento de datos , que comprende una unidad central de procesamiento, CPU , una memoria , un controlador […]

Dispositivo de inserción de terminal, del 27 de Noviembre de 2019, de Ingenico Group: Dispositivo de conexión de un terminal de comunicación, dispositivo que comprende:

- una superficie plana ;

- un conector macho destinado a conectarse a […]

Dispositivo de inserción de terminal, del 27 de Noviembre de 2019, de Ingenico Group: Dispositivo de conexión de un terminal de comunicación, dispositivo que comprende:

- una superficie plana ;

- un conector macho destinado a conectarse a […]

Dispositivo de conmutación, sistema de interconexión de componentes periféricos rápida y procedimiento de inicialización del mismo, del 13 de Noviembre de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un dispositivo de conmutación que comprende: múltiples puertos de Interconexión de Componentes Periféricos rápidos, PCIe, aguas arriba , […]

Solución Ethernet universal, del 2 de Octubre de 2019, de SCHNEIDER ELECTRIC INDUSTRIES SAS: Un circuito integrado monolítico , que comprende: al menos un núcleo de procesador de aplicaciones utilizable para ejecutar una aplicación industrial y código de […]

Método y aparato para extender el dominio PCIE, del 18 de Septiembre de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método para acceder a un dominio de interconexión de componente periférico exprés PCIe, en donde el método se utiliza para un sistema que comprende un dominio primario […]

Método y servidor para presentar el grado de inicialización del hardware en un servidor, del 28 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un servidor, que comprende una tarjeta gráfica y que comprende además un conmutador de selección de señal , un sistema fuera de banda y un módulo BIOS, […]

Red de comunicación para un equipamiento eléctrico de baja tensión, del 24 de Julio de 2019, de ABB S.P.A.: Una red de comunicación para un cuadro de distribución de baja tensión, comprendiendo dicho cuadro de distribución al menos un dispositivo de interrupción eléctrica […]