PROCEDIMIENTO Y DISPOSITIVO PARA LA RECONFIGURACIÓN DINÁMICA DE UN SISTEMA DE RADIOCOMUNICACIONES.

Sistema de radiocomunicaciones con un circuito de procesamiento (2),

en el que el circuito de procesamiento (2) procesa señales de recepción y señales de emisión, en el que el circuito de procesamiento (2) comprende un circuito lógico libremente programable, en el que el circuito de procesamiento (2) es adaptable a un servicio de recepción y a un servicio de emisión del sistema de radiocomunicaciones gracias al cambio de la programación del circuito lógico libremente programable, en el que, en el momento de la conmutación del servicio de recepción al servicio de emisión y/o del servicio de emisión al servicio de recepción mediante el cambio de la programación del circuito lógico libremente programable se exportan bloques funcionales (30-39, 50-59, 70-79, 90-99, 120-129, 150-159) del sistema de radiocomunicaciones del circuito lógico y/o se importan en el circuito lógico, en el que la reprogramación del circuito lógico libremente programable se realiza en áreas parciales y en el que las áreas parciales no afectadas por la reprogramación del circuito lógico libremente programable no sufren ninguna interrupción de su función durante la reprogramación

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2008/002065.

Solicitante: ROHDE & SCHWARZ GMBH & CO. KG.

Nacionalidad solicitante: Alemania.

Dirección: MUHLDORFSTRASSE 15 81671 MUNCHEN ALEMANIA.

Inventor/es: FOAG,JURGEN.

Fecha de Publicación: .

Fecha Solicitud PCT: 14 de Marzo de 2008.

Fecha Concesión Europea: 6 de Octubre de 2010.

Clasificación Internacional de Patentes:

- H04B1/00D

Clasificación PCT:

- G06F9/445 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Carga o inicio de programas (arranque G06F 9/4401; disposiciones de seguridad para la carga o inicio de programas G06F 21/57).

- H04B1/00 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04B TRANSMISION. › Detalles de los sistemas de transmision, no cubiertos por uno de los grupos H04B 3/00 - H04B 13/00; Detalles de los sistemas de transmisión no caracterizados por el medio utilizado para la transmisión.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Procedimiento y dispositivo para la reconfiguración dinámica de un sistema de radiocomunicaciones.

La invención se refiere a un procedimiento y un dispositivo para la reconfiguración dinámica de un sistema de radiocomunicaciones.

Habitualmente, en los sistemas de radiocomunicaciones se montan todas las unidades funcionales que se necesitan para el procesamiento de las señales de forma independiente y se conectan formando el sistema global. Para la reducción de la complejidad del montaje de los equipos, del volumen de los equipos y de los costes, en el documento US 2006/00073804 A1 se propone un dispositivo que reconfigura los bloques funcionales de un sistema de radiocomunicaciones que se necesitan en distintos estados de servicio en distintas conexiones al cambiar de estado de servicio. En el documento US 2006/00073804 A1, por reconfiguración se entiende exclusivamente la inversión de la dirección de procesamiento de los datos en el sistema, pero no un intercambio de bloques funcionales diferentes. De este modo se evita un montaje múltiple de bloques funcionales idénticos. El montaje se realiza en un FPGA (Field Programable Gate Array), es decir, en una matriz de puertas programables por campo. Un inconveniente de esta solución es que los bloques funcionales idénticos, que se necesitan en distintos estados de servicio en distintas configuraciones, representan sólo una pequeña parte del montaje de un sistema de radiocomunicaciones típico. Otro inconveniente es que no existen funciones que requieran otros bloques funcionales, por lo que no pueden ser realizadas.

Por lo tanto, la complejidad del montaje de los equipos, el volumen de los equipos y los costes sólo pueden reducirse un poco.

La invención tiene el objetivo de crear un sistema de radiocomunicaciones y un procedimiento para el funcionamiento de un sistema de radiocomunicaciones que con una complejidad reducida del montaje de los equipos presente un volumen de equipos reducido, suponga costes reducidos y soporte al mismo tiempo formas de ondas lo más diferentes posible.

El objetivo se consigue según la invención para el dispositivo mediante las características de la reivindicación independiente 1 y para el procedimiento mediante las características de la reivindicación independiente 8. Las reivindicaciones subordinadas se refieren a variantes ventajosas.

Un sistema de radiocomunicaciones está provisto de un circuito de procesamiento. El circuito de procesamiento procesa tanto señales de recepción como señales de emisión. Parte del circuito de procesamiento es un circuito lógico libremente programable. Mediante un cambio de su programación se adapta a distintos estados de servicio. El servicio de emisión y el servicio de recepción se caracterizan aquí por una programación diferente del circuito lógico libremente programable. Para ello, se descargan (exportan) y cargan (importan) bloques funcionales del circuito lógico libremente programable.

La reprogramación se realiza preferiblemente durante el tiempo de ejecución del sistema de radiocomunicaciones. Gracias a la realización de al menos una parte del circuito de procesamiento como circuito lógico programable se consigue una flexibilidad muy grande del posible montaje del circuito. Esto conduce, además, a una complejidad reducida del montaje de los equipos, un volumen reducido de los equipos y costes reducidos.

Una realización ventajosa del circuito lógico programable mediante un FPGA hace que haya una elevada velocidad de procesamiento consiguiéndose al mismo tiempo costes reducidos. La estructuración ventajosa de la reprogramación del circuito lógico libremente programable en áreas parciales hace que haya una elevada velocidad de procesamiento, puesto que el procesamiento continua en amplias áreas del circuito lógico libremente programable mientras que se reprograma un área parcial. Además, se garantiza la consistencia de las señales, puesto que una reprogramación del circuito lógico libremente programable se realiza sólo en áreas que no se están usando en un momento determinado no pudiendo distorsionarse, por lo tanto, ninguna señal.

Gracias a la posibilidad ventajosa del paso múltiple de las señales o segmentos de señales por distintas áreas parciales del circuito lógico libremente programable, puede reducirse aún más la complejidad del montaje del circuito y, por lo tanto, el tamaño y los costes. Un uso ventajoso para el procesamiento de distintas formas de ondas permite adicionalmente una flexibilidad muy grande de la aplicación del sistema de radiocomunicaciones, sin el esfuerzo de tener que poner a disposición un circuito de procesamiento para cualquier tarea de comunicación concebible.

Gracias a una marcación ventajosa de las áreas del circuito lógico libremente programable por las que ya se ha pasado, la reconfiguración puede comenzar ya en estas áreas, mientras que otras áreas del circuito lógico libremente programable aún están ocupadas con el procesamiento. Esto aumenta la velocidad de procesamiento del circuito de procesamiento gracias a la reducción del tiempo necesario para la reconfiguración.

A continuación, la invención se explicará a título de ejemplo con ayuda del dibujo, en el que está representado un ejemplo de realización ventajoso de la invención. En el dibujo muestran:

La Figura 1 una visión global del montaje de un sistema de radiocomunicaciones según la invención realizado a título de ejemplo;

la Figura 2 un montaje realizado a título de ejemplo de un circuito de procesamiento según la invención;

la Figura 3 un diagrama de bloques de la conexión interior de un FPGA realizado a título de ejemplo en servicio de recepción;

la Figura 4 un diagrama de bloques de la conexión interior de un FPGA realizado a título de ejemplo en servicio de emisión;

la Figura 5 un diagrama de bloques de la conexión interior de un FPGA realizado a título de ejemplo al principio de la reprogramación del servicio de recepción al servicio de emisión;

la Figura 6 un diagrama de bloques de la conexión interior de un FPGA realizado a título de ejemplo al final de la reprogramación del servicio de recepción al servicio de emisión;

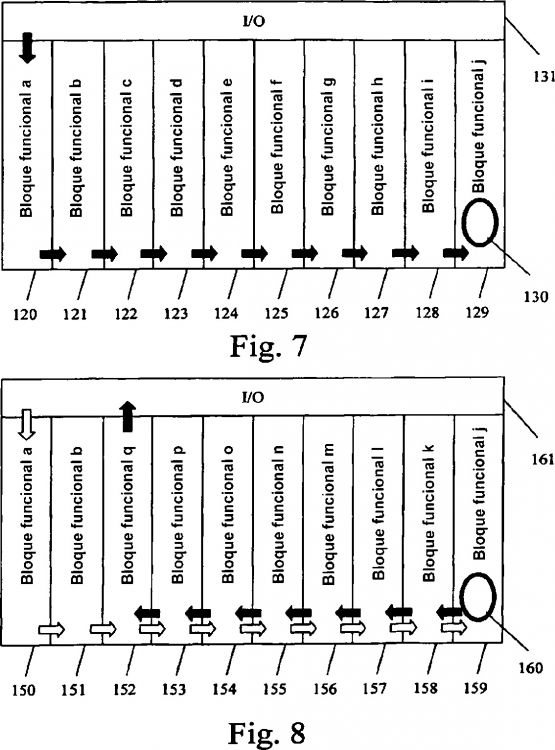

la Figura 7 un diagrama de bloques de la conexión interior de un FPGA realizado a título de ejemplo de función genérica durante el procesamiento de un segmento de señal y

la Figura 8 un diagrama de bloques de la conexión interior de un FPGA realizado a título de ejemplo de función genérica después de la reprogramación para el uso múltiple de distintas áreas parciales.

En primer lugar, se explicará con ayuda de las Figuras 1 y 2 el montaje y el funcionamiento general del sistema de radiocomunicaciones. Mediante las Figuras 3 y 4 se muestra en general la función de la reprogramación. Con ayuda de las Figuras 5 y 6 se muestra la reprogramación por bloques. Las Figuras 7 y 8 muestran el uso múltiple de áreas individuales del circuito de procesamiento para la realización de distintas operaciones. En figuras similares, los elementos idénticos en parte no se han representado y descrito de forma repetida.

La Figura 1 muestra una visión global del montaje de un sistema de radiocomunicaciones según la invención realizado a título de ejemplo. Una antena 1 está conectada con un circuito de procesamiento 2. El circuito de procesamiento procesa tanto señales salientes como señales entrantes.

En la Figura 2 se muestra un montaje realizado a título de ejemplo de un circuito de procesamiento según la invención. Un convertidor analógico-digital/digital-analógico 10 está conectado con un FPGA 11. El FPGA 11 estás conectado con una fuente de datos 12 y un sumidero de datos 13. El convertidor analógico-digital/digital-analógico 10 recibe señales recibidas de la antena 1, las digitaliza y las transmite al FPGA 11. El FPGA 11 demodula y decodifica las señales y realiza, dado el caso, otras operaciones. Los datos recibidos son transmitidos al sumidero de datos 13. La fuente de datos 12 genera datos destinados a la emisión. Los datos se transmiten al FPGA 11. El FPGA 11 codifica y modula los datos convirtiéndolos en una señal. Dado el caso, el FPGA 11 realiza otras operaciones. La señal que se presenta aún en forma digital es transmitida al convertidor analógico-digital/digital-analógico 10, es convertida por éste en una señal analógica y es transmitida a la antena 1.

...

Reivindicaciones:

1. Sistema de radiocomunicaciones con un circuito de procesamiento (2),

en el que el circuito de procesamiento (2) procesa señales de recepción y señales de emisión,

en el que el circuito de procesamiento (2) comprende un circuito lógico libremente programable,

en el que el circuito de procesamiento (2) es adaptable a un servicio de recepción y a un servicio de emisión del sistema de radiocomunicaciones gracias al cambio de la programación del circuito lógico libremente programable,

en el que, en el momento de la conmutación del servicio de recepción al servicio de emisión y/o del servicio de emisión al servicio de recepción mediante el cambio de la programación del circuito lógico libremente programable se exportan bloques funcionales (30-39, 50-59, 70-79, 90-99, 120-129, 150-159) del sistema de radiocomunicaciones del circuito lógico y/o se importan en el circuito lógico,

en el que la reprogramación del circuito lógico libremente programable se realiza en áreas parciales y en el que las áreas parciales no afectadas por la reprogramación del circuito lógico libremente programable no sufren ninguna interrupción de su función durante la reprogramación.

2. Sistema de radiocomunicaciones según la reivindicación 1, caracterizado porque la reprogramación del circuito lógico libremente programable se realiza sin interrupción de la función del sistema de radiocomunicaciones.

3. Sistema de radiocomunicaciones según la reivindicación 2, caracterizado porque el circuito lógico libremente programable es un FPGA (11).

4. Sistema de radiocomunicaciones según una de las reivindicaciones 1 a 3, caracterizado porque distintos segmentos de señal (130, 160) pasan varias veces por las áreas parciales (152-158) del circuito lógico libremente programable y porque la programación de las áreas parciales (152-158) del circuito lógico libremente programable se cambia tras el procesamiento y la transmisión de un segmento de señal (130, 160).

5. Sistema de radiocomunicaciones según la reivindicación 4, caracterizado porque el segmento de señal (130, 160) vuelve a pasar por las áreas parciales (152-158) modificadas del circuito lógico libremente programable y porque las etapas reprogramación y procesamiento de señal en un área parcial del circuito lógico libremente programable puede repetirse las veces que se desee para un segmento de señal (130, 160).

6. Sistema de radiocomunicaciones según una de las reivindicaciones 1 a 5, caracterizado porque el circuito lógico libremente programable presenta programaciones diferentes cuando procesa distintas formas de ondas y porque las distintas formas de ondas provienen de distintos procedimientos de modulación y/o procedimientos de codificación y/o procedimientos de cifrado y/o frecuencias y/o espectros y/o potencias.

7. Sistema de radiocomunicaciones según la reivindicación 4 ó 5, caracterizado porque el último segmento de señal (80, 100) que antes de una reprogramación está previsto para ser procesado por parte de un área determinada (70-79) del circuito lógico libremente programable se indica mediante una señal determinada, porque las áreas (70-73, 90-98) del circuito lógico libremente programable que ya han procesado este último segmento de señal se liberan para la reprogramación y porque se cambia la programación de las áreas (70-73, 90-98) liberadas del circuito lógico libremente programable mientras que el último segmento de señal (80, 100) aún es procesado por otras áreas (74-79, 99) no modificadas del circuito lógico libremente programable.

8. Procedimiento para el funcionamiento de un sistema de radiocomunicaciones con un circuito de procesamiento (2),

en el que el procesamiento de señales de recepción y de señales de emisión es realizado por el circuito de procesamiento (2),

en el que el procesamiento es realizado al menos en parte por un circuito lógico libremente programable contenido en el circuito de procesamiento (2), en el que el circuito de procesamiento (2) es adaptado mediante un cambio de la programación del circuito lógico libremente programable a distintos estados de servicio del sistema de radiocomunicaciones,

en el que, en el momento de la conmutación del servicio de recepción al servicio de emisión y/o del servicio de emisión al servicio de recepción mediante el cambio de la programación del circuito lógico libremente programable se exportan bloques funcionales (30-39, 50-59, 70-79, 90-99, 120-129, 150-159) del circuito lógico y/o se importan en el circuito lógico,

en el que la reprogramación del circuito lógico libremente programable se realiza en áreas parciales y en el que las áreas parciales no afectadas por la reprogramación del circuito lógico libremente programable no sufren ninguna interrupción de su función durante la reprogramación.

9. Procedimiento según la reivindicación 8, caracterizado porque durante el funcionamiento del sistema de radiocomunicaciones, en el momento de la conmutación del servicio de recepción al servicio de emisión y/o del servicio de emisión al servicio de recepción se realizan las siguientes etapas:

a. procesamiento de señales mediante el circuito lógico libremente programable en el servicio de emisión o en el servicio de recepción;

b. cambio de la programación del circuito lógico libremente programable;

c. continuación del procesamiento de señales mediante el circuito lógico libremente programable en el servicio de recepción o en el servicio de emisión.

10. Procedimiento según la reivindicación 8 ó 9, caracterizado porque el cambio de la programación del circuito lógico libremente programable se realiza sin interrupción de la función del sistema de radiocomunicaciones.

11. Procedimiento según la reivindicación 10, caracterizado porque el circuito lógico libremente programable es un FPGA (11).

12. Procedimiento según una de las reivindicaciones 8 a 11, caracterizado porque para la reprogramación del circuito lógico libremente programable se realizan las siguientes etapas:

a. procesamiento de señales mediante el circuito lógico libremente programable;

b. cambio del estado de servicio del sistema de radiocomunicaciones;

c. cambio de la programación de las áreas parciales no usadas del circuito lógico libremente programable;

d. continuación del procesamiento de señales mediante el circuito lógico libremente programable;

e. repetición de las etapas c. y d. hasta que la programación del circuito lógico libremente programable esté completamente adaptado al nuevo estado de servicio.

13. Procedimiento según una de las reivindicaciones 8 a 12, caracterizado porque distintos segmentos de señal (130, 160) pasan varias veces por las áreas parciales (152-158) del circuito lógico libremente programable y porque se cambia la programación de las áreas parciales (152-158) del circuito lógico libremente programable tras el procesamiento y la transmisión de un segmento de señal (130, 160).

14. Procedimiento según la reivindicación 13, caracterizado porque el segmento de señal (130, 160) vuelve a pasar por las áreas parciales (152-158) modificadas del circuito lógico libremente programable y porque las etapas reprogramación y procesamiento de señal pueden repetirse las veces que se desee en un área parcial del circuito lógico libremente programable para un segmento de señal (130, 160).

15. Procedimiento según la reivindicación 14, caracterizado porque para el paso repetido de segmentos de señal (130, 160) por distintas áreas parciales del circuito lógico libremente programable se realizan las siguientes etapas:

a. procesamiento de los segmentos de señales (130, 160) mediante los bloques funcionales en primeras áreas parciales del circuito lógico libremente programable;

b. procesamiento de los segmentos de señales (130, 160) mediante los bloques funcionales en segundas áreas parciales del circuito lógico libremente programable;

c. cambio de los bloques funcionales de las primeras áreas parciales del circuito lógico libremente programable;

d. procesamiento de los segmentos de señales (130, 160) mediante los bloques funcionales en primeras áreas parciales del circuito lógico libremente programable;

e. cambio de los bloques funcionales de las segundas áreas parciales del circuito lógico libremente programable;

f. repetición de las etapas b. a e. hasta que haya finalizado el procesamiento de los segmentos de señales.

16. Procedimiento según una de las reivindicaciones 8 a 15, caracterizado porque el circuito lógico libremente programable se programa de diferentes maneras para el procesamiento de distintas formas de ondas y porque las distintas formas de ondas se realizan mediante distintos procedimientos de modulación y/o procedimientos de codificación y/o procedimientos de cifrado y/o frecuencias y/o espectros y/o potencias.

17. Procedimiento según la reivindicaciones 14 ó 15, caracterizado porque el último segmento de señal (80, 100) que está previsto para ser procesado por parte de un área determinada (70-79) del circuito lógico libremente programable se indica mediante una señal determinada antes de un cambio de la programación, porque las áreas (70-73, 90-98) del circuito lógico libremente programable que ya han procesado este último segmento de señal se liberan para la reprogramación y porque la programación de las áreas (70-73, 90-98) liberadas del circuito lógico libremente programable se cambia mientras que el último segmento de señal aún es procesado por otras áreas (74-79, 99) no modificados del circuito lógico libremente programable.

Patentes similares o relacionadas:

METODO PARA GESTIONAR RECURSOS DE COMPUTACION APLICABLE A UN SISTEMA DE RADIO DEFINIDA POR PROGRAMA, del 27 de Septiembre de 2010, de UNIVERSITAT POLITECNICA DE CATALUNYA: Método para gestionar recursos de computación aplicable a un sistema de radio definida por programa. Comprende mapear unas funciones, procesos o partes […]

Radio digital multicanal, del 1 de Abril de 2020, de Elbit Systems Land and C4I Ltd: Un dispositivo de radio digital compacto multicanal , configurado como transceptor, que comprende: al menos una antena ; al menos un convertidor de banda […]

Conjunto de dispositivo aplicado a terminal móvil y terminal móvil, del 8 de Enero de 2020, de Guangdong OPPO Mobile Telecommunications Corp., Ltd: Un conjunto de dispositivo aplicado a un terminal móvil que comprende un conjunto de huellas dactilares , comprendiendo el conjunto de huellas […]

Unidad remota de radio, receptor y estación base, del 30 de Octubre de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Una unidad remota de radio, RRU, que comprende al menos un par de canales de recepción , un primer módulo de oscilador local , un segundo […]

Unidad remota de radio, receptor y estación base, del 30 de Octubre de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Una unidad remota de radio, RRU, que comprende al menos un par de canales de recepción , un primer módulo de oscilador local , un segundo […]

Sistema de transporte de radiofrecuencia por paquetes, del 2 de Octubre de 2019, de Kratos Integral Holdings, LLC: Un sistema de red espectral para la transmisión y recepción de señales de RF multibanda a través de una red de protocolo de Internet (IP), que comprende una primera […]

Dispositivo terminal de radio definida por software y método para distribuir e instalar aplicación de radio, del 4 de Septiembre de 2019, de Industry-University Cooperation Foundation Hanyang University: Dispositivo terminal de radio definida por software (SDR) que se configura de manera adaptativa según una aplicación de radio, comprendiendo el […]

Procedimiento y aparato para la comunicación concurrente con múltiples sistemas de comunicación inalámbrica de diferentes tecnologías de acceso por radio, del 28 de Agosto de 2019, de QUALCOMM INCORPORATED: Un aparato para comunicación inalámbrica, que comprende:

un primer receptor (230a, 330a) configurado para recibir una primera señal de enlace […]

Procedimiento y aparato para la comunicación concurrente con múltiples sistemas de comunicación inalámbrica de diferentes tecnologías de acceso por radio, del 28 de Agosto de 2019, de QUALCOMM INCORPORATED: Un aparato para comunicación inalámbrica, que comprende:

un primer receptor (230a, 330a) configurado para recibir una primera señal de enlace […]

Receptor de radio para agregación de portadora, del 7 de Agosto de 2019, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un circuito receptor de radio para un sistema de comunicaciones celulares, que comprende: un primer receptor de conversión directa, dispuesto […]