PROCEDIMIENTO Y DISPOSICION DE ACOPLAMIENTO PARA PREVENIR EL ACCESO NO AUTORIZADO A UN MICROPROCESADOR.

Un procedimiento para prevenir el uso no autorizado de una cierta interfaz protegida (102) en y hacia un procesador (101,

101'), que se caracteriza porque comprende: a1) generar dentro del procesador (101, 101') una indicación (NO PAT, ALARM) de intento de uso de la interfaz protegida, a2) Transmitir la indicación generada a otro componente (103, 103') y b) como respuesta a dicha indicación, detectar dentro de dicho otro componente (103, 103') si se ha recibido una palabra secreta en código (LIBERAR) a una orden de entrada de ese otro componente, y si no se ha recibido una palabra secreta en código, generando una señal de inhabilitación dentro de ese otro componente y usando dicha señal de inhabilitación para inhabilitar (INHABILITAR) al menos una gran parte de las operaciones del procesador

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E00103666.

Solicitante: NOKIA MULTIMEDIA TERMINALS OY.

Nacionalidad solicitante: Finlandia.

Dirección: P.O. BOX 226, 00045 HELSINKI.

Inventor/es: LAIHO,KIMMO, KAUNISTO,ISMO.

Fecha de Publicación: .

Fecha Solicitud PCT: 22 de Febrero de 2000.

Fecha Concesión Europea: 18 de Agosto de 2010.

Clasificación Internacional de Patentes:

- G06F21/00N1C

- G06F21/00N1S

Clasificación PCT:

- G06F21/02

Clasificación antigua:

- G06F1/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

La invención se refiere, en general, a la tecnología de protección de circuitos electrónicos y sus programas almacenados contra el acceso no autorizado. Especialmente, la invención se refiere a la tecnología de prevenir el uso no autorizado de una cierta interfaz a un procesador.

Un microprocesador (o "procesador” para abreviar) puede comprender una denominada interfaz de depuración para proporcionar un amplio control sobre las operaciones del procesador. La interfaz de depuración se puede usar para, por ejemplo, descargar y cargar programas, leer contenidos de los registros internos del procesador y realizar la ejecución paso por paso de los programas almacenados. En general, puede decirse que en un dispositivo electrónico controlado por procesador ofrece un acceso más o menos directo a todas estas características funcionales del procesador que pueden ser propiedad del fabricante y/o del operador autorizado del dispositivo. Por tanto, los fabricantes están buscando con impaciencia soluciones que evitarían el uso no autorizado de la interfaz de depuración. En función de la estructura del procesador puede haber también otras interfaces de procesador que deberían protegerse de forma similar.

Una fuerza bruta alternativa para proteger una interfaz es eliminar físicamente los vástagos externos o cortar las conexiones desde ellos a los correspondientes acoplamientos internos en los dispositivos que van desde la producción en serie al mercado. Por tanto, la interfaz de depuración sólo estaría disponible en prototipos y en unidades de prueba. La desventaja está clara: La interfaz de depuración no está disponible cuando, por ejemplo, una unidad disponible comercialmente debe ponerse en servicio o repararse.

El documento de la técnica anterior EP-A-O-897 144 divulga un procedimiento y un aparato para proporcionar protección frente al acceso en un procesador de datos. La solución se basa en comparar los datos de acceso y las señales control con valores de comparación previamente definidos y en responder a una falta de coincidencia realizando una reinicialización del hardware.

El documento de la técnica anterior EP-A-831 399 divulga un circuito temporizador de vigilancia (en inglés “perro guardián”), cuyo propósito es controlar que un procesador está funcionando de un modo deseado. Las situaciones de error, generadas por interferencias electromagnéticas, radiación externa o fallos de software, producen un funcionamiento anormal del procesador y, en consecuencia, alertan al circuito de vigilancia, que responde reiniciando el procesador.

Es un objeto de la presente invención proporcionar un procedimiento y una disposición de acoplamiento para prevenir el uso no autorizado de determinadas interfaces en un procesador. También es un objeto de la invención que el conjunto no necesariamente impide el uso autorizado de las interfaces protegidas. Un objeto adicional de la invención es implementar la protección sin un gran número de componentes adicionales.

Los objetos de la invención se consiguen mediante la asociación del uso de la interfaz de depuración con un cambio en ciertas rutinas realizadas por el procesador, disponiendo la detección de tal cambio fuera del procesador y uniendo la detección con la inhabilitación de una gran parte de la operación del procesador si no se ha activado cierto procedimiento de habilitación.

El procedimiento de acuerdo con la invención se caracteriza por las etapas mencionadas en la parte de caracterización de la reivindicación independiente dirigida a un procedimiento.

Adicionalmente, la invención se aplica a un dispositivo que está caracterizado por los rasgos mencionados en la parte de caracterización de la reivindicación independiente dirigida a un dispositivo.

Un dispositivo electrónico controlado por procesador comprende también otros componentes, entre los cuales puede haber otro circuito que es programable en el sentido de que se puede disponer de modo que espere ciertas señales de entrada y reaccione a ellas con cierta respuesta. De acuerdo con la invención, tal circuito externo se dispone de modo que actúe como un denominado perro guardián: el procesador cuya(s) interfaz(ces) se deben proteger tiene que "acariciar al perro guardián" con regularidad o dar una cierta señal de entrada al circuito externo con el fin de evitar la inhabilitación de al menos una gran parte de las operaciones del procesador. El procesador también está dispuesto de modo que asocie el uso de una interfaz protegida con el retraso o atasco de la emisión de dichas entradas, por que normalmente un intento de usar la interfaz protegida tendrá como resultado la inhabilitación de al menos una gran parte de la operación del procesador. Un usuario autorizado conoce una orden o procedimiento secreto que evitará que el circuito externo reaccione o anule la reacción de modo que el procesador se mantenga operativo.

El concepto de “acariciar al perro guardián” puede también entenderse de forma inversa: en condiciones normales, el procesador no envía entradas al circuito externo, lo que mantiene el procesador habilitado. Un intento de usar la(s) interfaz(ces) protegida(s) hace que el procesador emita una alarma al circuito externo que, a su vez, inhabilita al menos una gran parte de la operación del procesador. Una orden o procedimiento de liberación está disponible para los usuarios autorizados para evitar que la alarma cause la inhabilitación.

Los nuevos rasgos que se consideran característicos de la invención se exponen en particular en las reivindicaciones adjuntas. No obstante, la propia invención, tanto en cuanto a su construcción como a su procedimiento de operación, junto con objetos adicionales y ventajas de la misma, se entenderá mejor a partir de la siguiente descripción de formas de realización específicas cuando se leen en relación con las figuras adjuntas.

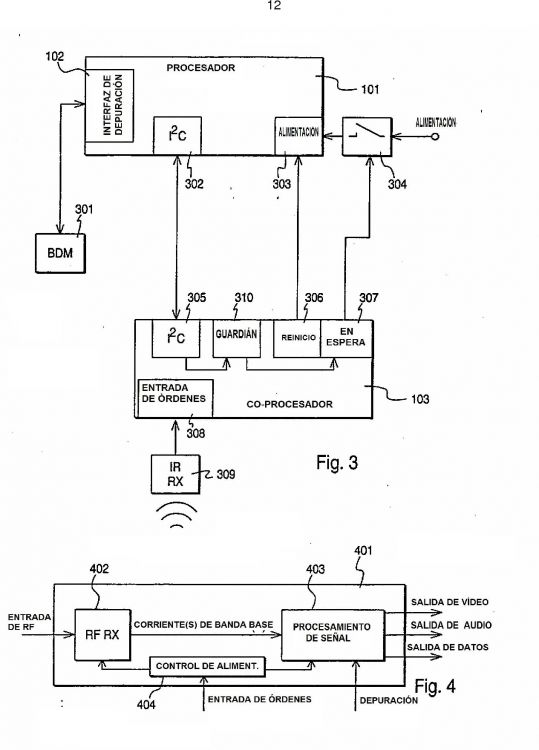

La Figura 3 Ilustra la disposición de un circuito que implementa el principio de las Figuras 1a-1c y

La Figura 4 ilustra un dispositivo electrónico de acuerdo con una forma de realización de la invención.

Partes similares en las figuras se designan con los mismos indicadores de referencia.

Las Figuras 1a a 1c muestran un procesador 101 con una interfaz 102 que debería protegerse contra el acceso no autorizado. Otra parte del conjunto es un circuito de vigilancia

103. En condiciones normales, cuando no hay intentos de usar la interfaz 102, el procesador envía con regularidad un poco de información de entrada al circuito de vigilancia de acuerdo con la flecha “PAT”. Como resultado, el circuito de vigilancia 103 habilita la operación del procesador 101 de acuerdo con la flecha “HABILITAR”. El procesador 101 se ha construido y programado de tal modo que cuando se efectúa un intento de usar la interfaz protegida 102 como en la Figura 1b, el procesador se detiene o retrasa el envío de entradas al circuito de vigilancia 103. Este último normalmente responde inhabilitando al menos una gran parte de las operaciones del procesador. La Figura 1c ilustra una situación en la que el intento de usar la interfaz protegida 102 se acompaña de una orden de liberación al circuito de vigilancia. La orden de liberación evita que el circuito de vigilancia 103 inhabilite el procesador 101 de modo que el usuario que sepa la orden de liberación correcta pueda proseguir usando la interfaz protegida, por ejemplo para depurar cualquier software recién cargado en el procesador.

Las Figuras 2a a 2c muestran de nuevo un procesador y un circuito de vigilancia que ahora se han designado 101' y 103' respectivamente porque su operación difiere ligeramente de la del procesador 101 y el circuito de vigilancia 103 de las Figuras 1a a 1c. Cuando no se efectúan intentos de usar la interfaz protegida 102, el procesador 101' no envía al circuito de vigilancia 103' ninguna entrada relacionada con la interfaz protegida como en a Figura 2a. Un intento de usar la interfaz protegida hace que se emita una alarma al circuito de vigilancia 103' de acuerdo con la Figura 2b, lo que inhabilita al menos una gran parte de la operación del procesador 101'. Si el intento...

Reivindicaciones:

1. Un procedimiento para prevenir el uso no autorizado de una cierta interfaz protegida

(102) en y hacia un procesador (101, 101'), que se caracteriza porque comprende: a1) generar dentro del procesador (101, 101') una indicación (NO PAT, ALARM) de

intento de uso de la interfaz protegida, a2) Transmitir la indicación generada a otro componente (103, 103') y b) como respuesta a dicha indicación, detectar dentro de dicho otro componente

(103, 103') si se ha recibido una palabra secreta en código (LIBERAR) a una orden de entrada de ese otro componente, y si no se ha recibido una palabra secreta en código, generando una señal de inhabilitación dentro de ese otro componente y usando dicha señal de inhabilitación para inhabilitar (INHABILITAR) al menos una gran parte de las operaciones del procesador.

2. Un procedimiento de acuerdo con la reivindicación 1, que se caracteriza porque comprende antes a1) transmisión regular de una corriente de señales (PAT) desde el procesador a este otro componente y a1) y a2) corresponden a retrasar o detener la generación y la transmisión de dicha corriente de señales (NO PAT).

3. Un procedimiento de acuerdo con la reivindicación 1, que se caracteriza porque dicha inhabilitación en b) corresponde a cambiar el procesador a un estado en espera.

4. Un procedimiento de acuerdo con la reivindicación 3, que se caracteriza porque dicho cambio se consigue desconectando la energía de operación de una gran parte del procesador.

5. Un procedimiento de acuerdo con la reivindicación 1, que se caracteriza porque a1) y a2) corresponden a fijar una señal de alarma específica (ALARMA) en un estado de activo.

6. Un procedimiento de acuerdo con la reivindicación 1, que se caracteriza porque comprende después de b): Detectar dentro de ese otro componente si se ha recibido una palabra secreta en código (LIBERAR) a una entrada de orden de ese otro componente y si se a recibido una palabra secreta en código (LIBERAR), rehabilitando la parte inhabilitada de la operación del procesador.

7. Un dispositivo que comprende

- un procesador (101, 101') y

- dentro del procesador una primera interfaz (102) al procesador, y una segunda interfaz (302), que se caracteriza por prevenir el uso no autorizado de la primera interfaz que el dispositivo electrónico comprende

- otro componente (103) acoplado a dicha segunda interfaz,

- dentro del procesador (101, 101 '), medios para generar una indicación (NO PAT, ALARMA) de intento de uso de la primera interfaz y medios para transmitir dicha indicación a ese otro componente mediante dicha segunda interfaz (302),

- dentro de este otro componente, medios (310, 307) para generar, sobre la base de una indicación recibida, una señal de inhabilitación para inhabilitar (INHABILITAR) al menos una parte de la operación del procesador, y

- dentro de este otro componente, una entrada de órdenes y medios para detectar si se ha recibido una palabra secreta en código (308) a dicha entrada de órdenes, y medios para inhabilitar la emisión de dicha señal de inhabilitación al procesador como respuesta a la detección de que dicha palabra secreta en código no se ha recibido.

8. Un dispositivo de acuerdo con la reivindicación 7, que se caracteriza porque comprende un conmutador (304), que responde a dicha señal de inhabilitación, para apagar de forma selectiva la energía de operación de una parte del procesador.

9. Un dispositivo de acuerdo con la reivindicación 7, que se caracteriza porque comprende -dentro de este otro componente un registro de vigilancia (310) y medios para cambiar con regularidad el valor de dicho registro de vigilancia de forma monótona en una dirección determinada, -dentro del procesador medios (302) para reiniciar con regularidad dicho registro de vigilancia a un valor constante determinado a través de dicha segunda interfaz,

- dentro de ese otro componente, medios para comparar con regularidad el valor de dicho registro de vigilancia frente a cierto valor limitante que reside en dicha

dirección determinada a partir de dicho valor constante,

- dentro de este otro componente, medios para generar, como respuesta a una igualdad detectada o que supera el valor del registro de vigilancia al valor limitante, dicha señal de inhabilitación (307).

10. Un dispositivo de acuerdo con la reivindicación 7, que se caracteriza porque dichos medios para detectar si se ha recibido una palabra secreta en código están acoplados a un receptor inalámbrico (309) para recibir órdenes por una conexión inalámbrica.

11. Un dispositivo de acuerdo con la reivindicación 7, que se caracteriza porque ese otro componente (103) es un co-procesador responsable de proporcionar las señales de tensión y reinicio a las otras partes del dispositivo.

Patentes similares o relacionadas:

METODO PARA VISUALIZAR LA CANTIDAD DE BATERIA RESIDUAL Y EQUIPO ELECTRONICO, del 21 de Septiembre de 2010, de SONY CORPORATION: Un microprocesador que tiene función de comunicación utilizado por una batería compacta configurada para ser instalada de manera desmontable en […]

METODO PARA VISUALIZAR LA CANTIDAD DE BATERIA RESIDUAL Y EQUIPO ELECTRONICO, del 21 de Septiembre de 2010, de SONY CORPORATION: Un microprocesador que tiene función de comunicación utilizado por una batería compacta configurada para ser instalada de manera desmontable en […]

METODO PARA VISUALIZAR LA CANTIDAD DE BATERIA RESTANTE, Y APARATO ELECTRONICO, del 15 de Abril de 2010, de SONY CORPORATION: Un método para visualizar la cantidad de batería residual en un equipo electrónico, que comprende:

un cuerpo del equipo en el cual está montado un […]

METODO PARA VISUALIZAR LA CANTIDAD DE BATERIA RESTANTE, Y APARATO ELECTRONICO, del 15 de Abril de 2010, de SONY CORPORATION: Un método para visualizar la cantidad de batería residual en un equipo electrónico, que comprende:

un cuerpo del equipo en el cual está montado un […]

SISTEMA Y MÉTODO DE PROTECCIÓN DE DATOS EN UN DISPOSITIVO DE COMUNICACIÓN, del 26 de Abril de 2011, de RESEARCH IN MOTION LIMITED: Un dispositivo de comunicación para proteger los datos recibidos en dicho dispositivo de comunicación , comprendiendo el dispositivo […]

SISTEMA Y MÉTODO DE PROTECCIÓN DE DATOS EN UN DISPOSITIVO DE COMUNICACIÓN, del 26 de Abril de 2011, de RESEARCH IN MOTION LIMITED: Un dispositivo de comunicación para proteger los datos recibidos en dicho dispositivo de comunicación , comprendiendo el dispositivo […]

Procedimiento para la comunicación de datos en un vehículo y sistema para el funcionamiento de un dispositivo móvil en un vehículo, del 26 de Octubre de 2016, de VOLKSWAGEN AKTIENGESELLSCHAFT: Procedimiento para la comunicación de datos en un vehículo entre un dispositivo de comunicación de datos interno del vehículo y […]

Procedimiento de detección de anomalias en un circuito criptográfico protegido por lógica diferencial y circuito para implementar a dicho procedimiento, del 8 de Agosto de 2012, de Institut Telecom - Telecom Paristech: Circuito protegido por lógica diferencial que procesa variables lógicas representadas por pares de componentes(at, af) (bt, bf), una primera red de células (T) que realizan funciones […]

Procedimiento de detección de anomalias en un circuito criptográfico protegido por lógica diferencial y circuito para implementar a dicho procedimiento, del 8 de Agosto de 2012, de Institut Telecom - Telecom Paristech: Circuito protegido por lógica diferencial que procesa variables lógicas representadas por pares de componentes(at, af) (bt, bf), una primera red de células (T) que realizan funciones […]

Módulo seguro para proporcionar valores horarios de confianza, del 3 de Agosto de 2012, de VODAFONE GROUP PLC: Un método para proporcionar valores horarios de confianza en dispositivos de comunicaciones que cuentancon un medio de almacenamiento seguro y que se pueden emplear para […]

Módulo seguro para proporcionar valores horarios de confianza, del 3 de Agosto de 2012, de VODAFONE GROUP PLC: Un método para proporcionar valores horarios de confianza en dispositivos de comunicaciones que cuentancon un medio de almacenamiento seguro y que se pueden emplear para […]

Procedimiento de aseguramiento de un microprocesador, programa de ordenador y dispositivo correspondientes, del 11 de Julio de 2012, de COMPAGNIE INDUSTRIELLE ET FINANCIERE D'INGENIERIE INGENICO: Un procedimiento de aseguramiento de un microprocesador que contiene al menos un programa principal, que coopera con al menos una memoria, comprendiendo […]

Procedimiento de aseguramiento de un microprocesador, programa de ordenador y dispositivo correspondientes, del 11 de Julio de 2012, de COMPAGNIE INDUSTRIELLE ET FINANCIERE D'INGENIERIE INGENICO: Un procedimiento de aseguramiento de un microprocesador que contiene al menos un programa principal, que coopera con al menos una memoria, comprendiendo […]

Procedimiento de preservación de la seguridad de una ramificación condicional, soporte de informaciones, programa y sistema asegurado para ese procedimiento, del 28 de Marzo de 2012, de VIACCESS: Procedimiento de preservación de la seguridad de una ramificación condicional contra ataques por inyección deerror, autorizando esta ramificación condicional […]