MOTOR MULTI-PROTOCOLO PARA PROCESAMIENTO DE CORRIENTE DE BITS RECONFIGURABLE EN REDES DE ALTA VELOCIDAD.

Un motor de procesamiento de paquete de datos multi-protocolo para manejar comunicación de paquete de paquetes de datos entre un procesador y una producción/estructura de red de alta velocidad que tiene una velocidad de línea de al menos 10 Gb/segundo,

el motor de procesamiento de paquete de datos comprende:

una porción de ingreso del motor de procesamiento de paquete de datos que incluye:

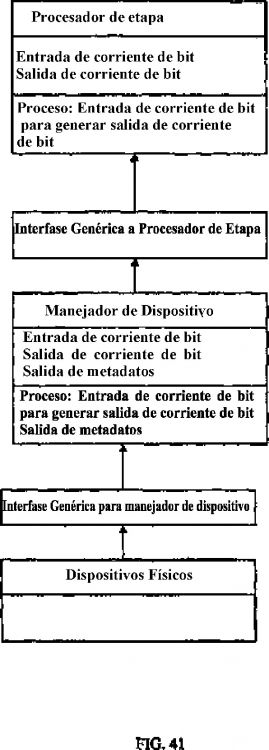

una pluralidad de procesadores de etapa de corriente de bit de ingreso, cada procesador de etapa de corriente de bit de ingreso tiene una memoria de control programable única para aquel procesador de etapa de corriente de bit de ingreso;

una interfase de procesador de ingreso al procesador;

una interfase de red de ingreso a la producción de red; y

una memoria de paquete de flujo de datos multi-puerto operablemente conectada a la pluralidad de procesadores de etapa de corriente de bit de ingreso, la interfase de procesador de ingreso y la interfase de red de ingreso; y

una porción de egreso del motor de procesamiento de paquete de datos que incluye:

una pluralidad de procesadores de etapa de corriente de bit de egreso, cada procesador de etapa de corriente de bit de egreso tiene una memoria de control programable única a aquella del procesador de etapa de corriente de bit de egreso;

una interfase de procesador de egreso al procesador;

una interfase de red de egreso a la producción de red; y

una memoria de paquete de flujo de datos multi-puerto operablemente conectada a la pluralidad de procesadores de etapa de corriente de bit de egreso, la interfase del procesador de egreso y la interfase de red de egreso;

en donde la memoria de control de cada uno de los procesadores de etapa de corriente de bit es individualmente, selectivamente, dinámicamente programable con base en una de una pluralidad de protocolos determinados para un flujo de datos dado de uno o más paquetes de datos y el proceso de los procesadores de etapa de corriente de bit del flujo de datos dado como un flujo de los datos de corriente de bit a través de la memoria de paquete de flujo de datos multi-puerto de tal manera que el procesamiento del flujo de datos dado por la pluralidad de procesadores de etapa de corriente de bit es temporizado de acuerdo al flujo de datos de corriente de bit y el flujo de datos de corriente de bit se establece a una velocidad que posibilita la operación continua del motor de procesamiento de paquete de datos para toda la pluralidad de protocolos sustancialmente a una velocidad que es al menos igual a la velocidad de línea de la producción de red de alta velocidad

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2006/032747.

Solicitante: SLT LOGIC LLC.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 50 COMMONWEALTH AVENUE, SUITE 504,BOSTON, MA 02116.

Inventor/es: SHARMA,VISWA, HOLSCHBACH,ROGER, STUCK,BART, CHU,WILLIAM.

Fecha de Publicación: .

Fecha Concesión Europea: 4 de Noviembre de 2009.

Clasificación Internacional de Patentes:

- G06F13/38A2

- H04L29/06G

- H04L29/06K

Clasificación PCT:

- G06F13/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16).

- G06F13/38 G06F […] › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › Transferencia de informaciones, p. ej. sobre un bus (G06F 13/14 tiene prioridad).

Fragmento de la descripción:

Motor multi-protocolo para procesamiento de corriente de bits reconfigurable en redes de alta velocidad.

Campo de la invención

La presente invención se relaciona de manera general con el campo de las comunicaciones de datos en una red. Más específicamente, la presente invención se relaciona con un motor de procesamiento de corriente de bits indiferente del protocolo reconfigurable, y con sistemas relacionados y metodologías de comunicación de datos, adaptadas para redes de alta velocidad que operan a velocidades de al menos 10 gigabits por segundo.

Antecedentes de la invención

Tradicionalmente, las redes se han dividido en diferentes clases de infraestructuras o estructuras basadas en el propósito de una red dada. Como resultado, se han desarrollado diferentes clases de redes para almacenar redes, redes de comunicación y redes de procesador, que tiene cada una diferentes protocolos y diferentes requisitos de red y cada designado para cumplir con requisitos particulares de comunicación de datos en esa estructura.

En el caso de redes de procesador, el desempeño de la red es un elemento crítico en aplicaciones de computo de controladores de alto desempeño (HPCC). Típicamente, las aplicaciones HPCC corren durante períodos extendidos de tiempo y requieren I/O sostenidos de conjuntos de datos grandes sobre la red entre los procesadores así como también entre el cliente y el servidor. De manera predecible, la infraestructura debe ser capaz de soportar servicios de ancho de banda multi-gigabit, de baja latencia, muy altamente disponibles que son un requisito absoluto para comunicaciones interproceso de gama alta. Convencionalmente, las redes HPCC utilizan Ethernet de Gigabit Conmutado. Los protocolos de propietario tales como, por ejemplo, Myrinet, InfiniBand y Quadrics también encuentran un uso amplio al conectar controladores de procesamiento en un ambiente HPCC.

La necesidad de cantidad es masivas de datos necesita que los procesadores en red en una aplicación HPCC, por ejemplo, estén eficientemente conectados a una estructura de red de almacenamiento. convencionalmente, el HPCC que soporta la infraestructura incluye una red anexada de almacenamiento (SAN) que conmuta la estructura tal como un interruptor de Canal de Fibra, o una red basada en Ethernet de Gigabit unida a amiente de almacenamiento (NAS). El Canal de Fibra es el protocolo dominante y el transporte para una estructura SAN en razón de las velocidades multi-gigabit y los protocolos de transporte que se optimizan para mover cantidades masivas de datos de almacenamiento de bloque entre clientes y dispositivos de almacenamiento.

Las redes de comunicación con Protocolo de Internet (IP) tienden a dominar la estructura para comunicaciones entre diferentes aplicaciones HPCC, así como también las comunicaciones generales entre clientes y servidores sobre una estructura de Internet más amplia. Algunas redes de almacenamiento han adoptado protocolos "piggyback" adecuados para mover datos de almacenamiento de bloque sobre redes de almacenamiento IP tales como SCSI Internet (iSCSI), Protocolo de Canal de Fibra de Internet (iFCP), y Canal de Fibra sobre IP (FCIP). Estos protocolos "piggyback", sin embargo, no permiten necesariamente la inter-operabilidad directa entre las redes de comunicaciones y las redes de almacenamiento.

La meta de suministrar interoperabilidad entre estructuras a través de estas diferentes clases de estructuras de red es una meta bien conocida. Aunque esta meta se puede lograr directamente en el contexto de redes de baja velocidad en donde todo el procesamiento requerido en la red se podría lograr con procesadores programables estándar, tal solución simplemente no es viable en altas velocidades de comunicación requeridas que operan a 10 gigabits por segundo y superiores. Para la mayor parte, los adaptadores especializados se han utilizado para hacer la transición entre un protocolo específico en la estructura y un protocolo común en un nodo interruptor central. Aunque esta aproximación puede ser transparente para el usuario final, es fácilmente evidente para un experto en la técnica de que tal como cuadros de adaptadores presentes en un problema de explosión exponencial en términos del número de protocolos siempre crecientes. La capacidad de suministrar un conmutador de red de alta velocidad que sería capaz de manejar múltiples protocolos es una solución que al menos algunos elaboradores de equipo de red no creen que sea posible. Silvano Gai, "Toward a unified architecture for LAN/WAN/WLAN/SAN suites and routers", pp. 23, HSPR 2003, Cisco Systems, Inc. (notar la no disponibilidad de un conmutador LAN barato de 10 Gb/s). De acuerdo con esto, subsiste la necesidad de encontrar una solución a la meta de suministrar interoperabilidad interestructura entre redes que sean tanto eficientes como escalables para redes de alta velocidad.

El documento WO 2004/013759 describe porciones de ingreso/egreso de datos un motor de procesamiento de paquete que comprende procesadores independientes conectados en un cable de datos.

Resumen de la invención

La presente invención suministra un motor de procesamiento de corriente de bits indiferente del protocolo reconfigurable, y sistemas relacionados y metodologías de comunicación de datos, que se adaptan para lograr la meta de suministrar interoperabilidad inter-estructura entre redes de alta velocidad que operan a velocidades de al menos 10 gigabits por segundo. El motor de procesamiento de corriente de datos opera como un procesador multi-protocolo, multi-etapa que se puede configurar con conmutadores apropiados y elementos de red relacionados para crear una estructura de red sin costuras que permiten la interoperabilidad no solamente entre los protocolos de comunicación existentes, sino también con la capacidad de acomodar futuros protocolos de comunicación. El método y los sistemas de la presente invención son aplicables a redes que incluyen redes de almacenamiento, redes de comunicación y redes de procesador.

En una realización de la invención, el motor de procesamiento multi-protocolo opera como un motor de procesamiento de flujo de datos que incluye tanto una porción de ingreso como una porción de egreso, teniendo cada porción al menos un procesador de etapa de corriente de bits. Preferiblemente, cada procesador de etapa se optimiza durante una etapa particular en el flujo de datos. Conceptualmente, el motor de procesamiento de flujo de datos trabaja muy similarmente a una línea de montaje de producción en la que en la medida en que el flujo de datos se mueve a través del motor de procesamiento se logra un procesamiento diferente como diferentes etapas de la línea de montaje, y todo el procesamiento es temporizado al flujo de los datos. El flujo de datos a través del motor de procesamiento se establece a una velocidad que permitirá la operación continúa del motor de procesamiento en la velocidad de línea de la o las redes a las cuales se conecta el motor de procesamiento. El modelo de flujo de datos utilizado en esta realización evita la necesidad de un manejo de buffer profundo y extenso con el fin de mantener el seguimiento de los datos tal como sería necesario en un procesador de protocolo convencional. Adicionalmente, los motores en cualquier etapa están inherentemente en cascada para soportar la escalabilidad.

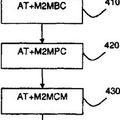

En una realización del motor de procesamiento multi-protocolo (OPE), las etapas múltiples incluyen al menos un procesador de corriente de bits de etapa de ingreso, una máquina de estado de etapa secundaria, un procesador de tráfico, un programador y un procesador de corriente de datos en etapa de egreso. El procesador de corriente de bits en etapa de ingreso hace interfase con la capa física del flujo de datos y establece marcos y/o flujos para la corriente de bits de acuerdo con un protocolo determinado para la corriente de bits. La máquina de estado de etapa secundaria analiza los marcos/flujos de acuerdo con el protocolo determinado, preferiblemente utilizando un clasificador de flujo de Palabra con Instrucción Muy Larga programable (VLIW) que procesa en cadena la generación clave. El procesamiento del marco/flujo se maneja por el procesador de tráfico. El programador maneja la salida del flujo de datos desde el procesador de tráfico y el procesador de la corriente de bits de etapa de egreso hace interfase con la capa física del flujo de datos por fuera del motor de procesamiento multi-protocolo. Todas las etapas son dinámicamente reconfigurables y reprogramables para permitirle al OPE ser indiferente al protocolo.

En una realización, la máquina de estado de etapa secundaria y el procesador de tráfico utilizan...

Reivindicaciones:

1. Un motor de procesamiento de paquete de datos multi-protocolo para manejar comunicación de paquete de paquetes de datos entre un procesador y una producción/estructura de red de alta velocidad que tiene una velocidad de línea de al menos 10 Gb/segundo, el motor de procesamiento de paquete de datos comprende:

una porción de ingreso del motor de procesamiento de paquete de datos que incluye:

una pluralidad de procesadores de etapa de corriente de bit de ingreso, cada procesador de etapa de corriente de bit de ingreso tiene una memoria de control programable única para aquel procesador de etapa de corriente de bit de ingreso;

una interfase de procesador de ingreso al procesador;

una interfase de red de ingreso a la producción de red; y

una memoria de paquete de flujo de datos multi-puerto operablemente conectada a la pluralidad de procesadores de etapa de corriente de bit de ingreso, la interfase de procesador de ingreso y la interfase de red de ingreso; y

una porción de egreso del motor de procesamiento de paquete de datos que incluye:

una pluralidad de procesadores de etapa de corriente de bit de egreso, cada procesador de etapa de corriente de bit de egreso tiene una memoria de control programable única a aquella del procesador de etapa de corriente de bit de egreso;

una interfase de procesador de egreso al procesador;

una interfase de red de egreso a la producción de red; y

una memoria de paquete de flujo de datos multi-puerto operablemente conectada a la pluralidad de procesadores de etapa de corriente de bit de egreso, la interfase del procesador de egreso y la interfase de red de egreso;

en donde la memoria de control de cada uno de los procesadores de etapa de corriente de bit es individualmente, selectivamente, dinámicamente programable con base en una de una pluralidad de protocolos determinados para un flujo de datos dado de uno o más paquetes de datos y el proceso de los procesadores de etapa de corriente de bit del flujo de datos dado como un flujo de los datos de corriente de bit a través de la memoria de paquete de flujo de datos multi-puerto de tal manera que el procesamiento del flujo de datos dado por la pluralidad de procesadores de etapa de corriente de bit es temporizado de acuerdo al flujo de datos de corriente de bit y el flujo de datos de corriente de bit se establece a una velocidad que posibilita la operación continua del motor de procesamiento de paquete de datos para toda la pluralidad de protocolos sustancialmente a una velocidad que es al menos igual a la velocidad de línea de la producción de red de alta velocidad.

2. El motor de procesamiento de paquete de datos de la reivindicación 1 en donde la pluralidad de procesadores de etapa de corriente de bit para la porción de ingreso del motor de procesamiento de paquete de datos comprende:

un procesador de corriente de bit de etapa de entrada que hace interfase con una capa física de la interfase de red de ingreso y establece marcos para el flujo de los datos de corriente de bit de acuerdo con una de la pluralidad de protocolos determinados para el paquete de datos dado.

una máquina de estado de etapa secundaria que analiza los marcos de acuerdo con una de la pluralidad de protocolos determinados para el paquete de datos dado;

un procesador de etapa de tráfico que maneja el procesamiento marco para los marcos analizados por la máquina de estado de etapa secundaria;

un procesador de etapa de programador que maneja la salida de los marcos desde el procesador de etapa de tráfico, y

un procesador de corriente de bit de etapa de salida que hace interfase con los marcos desde el procesador de estado programado con una capa física de la interfase del procesador de ingreso.

3. El motor de procesamiento de paquete de datos de la reivindicación 2 en donde la máquina de estado de etapa secundaria utiliza un arreglo de revisión clave en la medida en que la máquina de estado de etapa secundaria analiza los marcos que incorporan un clasificador de flujo de Palabra de Instrucción muy Larga Programable (VLIW) que encadena la generación clave para la disposición de revisión clave.

4. El motor de procesamiento de paquete de datos de la reivindicación 2 en donde el procesador de etapa de tráfico se implementa como un procesador de flujo de datos que tiene múltiples segmentos donde los múltiples segmentos en el procesador de etapa de tráfico se implementan dinámicamente dependiendo de uno de la pluralidad de protocolos determinado para el flujo de datos dado.

5. El motor de procesamiento de paquete de datos de la reivindicación 1 en donde al menos una porción de los procesadores de etapa de corriente de bit hace interfase con la memoria de paquete de flujo de datos multi-puerto utilizando una de una aproximación multiplexada arbitrada o con división de tiempo con el fin de eliminar la necesidad para cada uno de los procesadores de etapa de corriente de bit para copiar algunos o todos los datos en el flujo de datos dado con el fin de procesar esos datos.

6. El motor de procesamiento de paquete de datos de la reivindicación 1 en donde la memoria de control de cada uno de los procesadores de etapa de corriente de bit es seleccionable de uno de una memoria de instrucción o una memoria de estado y es individualmente, selectivamente, dinámicamente reconfigurable y programable utilizando un control de acceso de registro (RAC) y un sistema de control de acceso de sub-módulo (SAC).

7. El motor de procesamiento de paquete de datos de la reivindicación 6 en donde el sistema RAC y SAC se controla por una interfase de usuario gráfica (GUI) que maneja la generación de código, el control de flujo, el reporte de desempeño, los diagnósticos y el mantenimiento del motor de procesamiento de paquete de datos.

8. El motor de procesamiento de paquete de datos de la reivindicación 1 en donde la producción de red de alta velocidad se selecciona del conjunto que consiste de: redes de almacenamiento, redes de comunicación, redes de procesador y cualquier combinación de éstos.

9. El motor de procesamiento de paquete de datos de la reivindicación 1 que comprende además:

un conmutador de paquete de datos de alta velocidad multi-puerto,

en donde una pluralidad de motores de procesamiento de paquete de datos están operablemente conectados al conmutador multi-puerto para formar una disposición de puente multi- protocolo, y en donde cada una de la pluralidad de motores de procesamiento de paquete de datos se conecta a diferentes redes de alta velocidad que se comunican utilizando un protocolo diferente.

Patentes similares o relacionadas:

GESTIÓN DE UNA MEMORIA FÍSICA PARTICIONADA EN UNA ENTIDAD ELECTRÓNICA: PROCEDIMIENTO Y DISPOSITIVO, del 14 de Febrero de 2012, de OBERTHUR TECHNOLOGIES: Dispositivo de gestión de una memoria física de una entidad electrónica capaz de conectarse a una estación central , comprendiendo dicha […]

DISPOSITIVO DE ALMACENAMIENTO MASIVO Y SISTEMA DE ALMACENAMIENTO, del 2 de Diciembre de 2011, de SAGEM DEFENSE SECURITE: Dispositivo de almacenamiento masivo que incluye: -un módulo físico de almacenamiento masivo ;-un módulo de gestión física de […]

ARQUITECTURA PARA DISCO RELAMPAGO PARA ORDENADOR PERSONAL BASADA EN CANAL DE COMUNICACIONES SERIE UNIVERSAL, del 25 de Agosto de 2010, de MSYSTEMS LTD: Un dispositivo de memoria relámpago USB para conexión a un canal de comunicaciones definido USB, cuyo dispositivo de memoria relámpago comprende:

(a) […]

ARQUITECTURA PARA DISCO RELAMPAGO PARA ORDENADOR PERSONAL BASADA EN CANAL DE COMUNICACIONES SERIE UNIVERSAL, del 25 de Agosto de 2010, de MSYSTEMS LTD: Un dispositivo de memoria relámpago USB para conexión a un canal de comunicaciones definido USB, cuyo dispositivo de memoria relámpago comprende:

(a) […]

MODULO INTERFACE DE LECTURA/ESCRITURA DE TARJETAS SIN CONTACTO, del 24 de Mayo de 2010, de INTELLIGEN DATA S.L: Especialmente concebido para constituir un elemento fácilmente integrable en diferentes tipos de máquinas y automatismos, a fin de permitirles realizar operaciones […]

MODULO INTERFACE DE LECTURA/ESCRITURA DE TARJETAS SIN CONTACTO, del 24 de Mayo de 2010, de INTELLIGEN DATA S.L: Especialmente concebido para constituir un elemento fácilmente integrable en diferentes tipos de máquinas y automatismos, a fin de permitirles realizar operaciones […]

ARQUITECTURA PARA UNIDAD RELAMPAGO PARA ORDENADOR PERSONAL BASADA EN CANAL DE COMUNICACIONES SERIE UNIVERSAL, del 18 de Mayo de 2010, de M-SYSTEMS FLASH DISK PIONEERS LTD.: Un dispositivo de memoria relámpago USB para conexión a un canal de comunicaciones definido USB, cuyo dispositivo de memoria relámpago […]

ARQUITECTURA PARA UNIDAD RELAMPAGO PARA ORDENADOR PERSONAL BASADA EN CANAL DE COMUNICACIONES SERIE UNIVERSAL, del 18 de Mayo de 2010, de M-SYSTEMS FLASH DISK PIONEERS LTD.: Un dispositivo de memoria relámpago USB para conexión a un canal de comunicaciones definido USB, cuyo dispositivo de memoria relámpago […]

ESTRUCTURA DE PAQUETES PARA UNA INTERFAZ DIGITAL DE PANTALLA MÓVIL, del 19 de Julio de 2011, de QUALCOMM INCORPORATED: Procedimiento de envío de un paquete de datos de vídeo sin ventanas en un enlace de transmisión que acopla un cliente y un servidor en un dispositivo […]

TELÉFONO MÓVIL CON LECTOR DE RFID Y TRANSMISOR WLAN INTEGRADOS EN LA TARJETA SIM, del 3 de Febrero de 2011, de TELENOR ASA: Un procedimiento para el uso de un teléfono móvil para la adquisición de informaciones suplementarias en relación con un objeto provisto con una etiqueta de identificación […]

TELÉFONO MÓVIL CON LECTOR DE RFID Y TRANSMISOR WLAN INTEGRADOS EN LA TARJETA SIM, del 3 de Febrero de 2011, de TELENOR ASA: Un procedimiento para el uso de un teléfono móvil para la adquisición de informaciones suplementarias en relación con un objeto provisto con una etiqueta de identificación […]

PROCEDIMIENTO DE COMUNICACION POR MENSAJES Y DISPOSITIVO ASOCIADO, del 2 de Agosto de 2010, de FRANCE TELECOM: Procedimiento de comunicación entre un dispositivo emisor y un dispositivo destinatario, que comprende

- una etapa de transmisión, desde el dispositivo emisor […]

PROCEDIMIENTO DE COMUNICACION POR MENSAJES Y DISPOSITIVO ASOCIADO, del 2 de Agosto de 2010, de FRANCE TELECOM: Procedimiento de comunicación entre un dispositivo emisor y un dispositivo destinatario, que comprende

- una etapa de transmisión, desde el dispositivo emisor […]