MÉTODO Y SISTEMA DE TESTADO DE CIRCUITOS INTEGRADOS DE RADIOFRECUENCIA A NIVEL DE OBLEA Y SU USO.

Método y sistema de testado de circuitos integrados de radiofrecuencia a nivel de oblea y su uso.

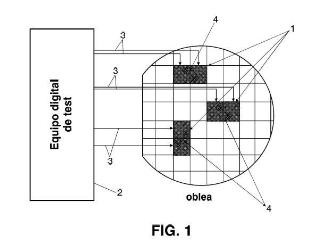

El objetivo principal de este invento es proporcionar un sistema y un método fiable y rápido para descartar transceptores integrados defectuosos a nivel de oblea mediante el establecimiento de enlaces inalámbricos entre diferentes circuitos en la oblea, de tal forma que las señales necesarias para testar un determinado transceptor son proporcionadas o leídas por otro de los transceptores de la misma oblea. El sistema emplea para ello, un equipo de test digital de baja frecuencia que al menos comprende dos agujas de test para el envío, recepción y comparación de unas secuencias de datos de test que se intercambian entre el equipo de test y los circuitos integrados de la oblea.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201131109.

Solicitante: CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC).

Nacionalidad solicitante: España.

Inventor/es: HUERTAS DIAZ,JOSE LUIS, BARRAGÁN ASIÁN,Manuel José.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H01L23/00 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad).

Fragmento de la descripción:

Método y sistema de testado de circuitos integrados de radiofrecuencia a nivel de oblea y su uso

OBJETO DE LA INVENCIÓN

La presente invención, tal y como se expresa en el enunciado de esta memoria descriptiva se refiere a un método y un sistema de testado de circuitos integrados de radiofrecuencia a nivel de oblea, es decir, circuitos integrados que se integran precisamente en obleas electrónicas. Además la presente invención se refiere también al uso del mencionado método y sistema.

La demanda creciente de sistemas on-chip con capacidad para comunicaciones inalámbricas ha llevado a un primer plano el problema de testar estos sistemas de manera eficiente. El test de sistemas de radiofrecuencia se ha realizado tradicionalmente mediante la verificación de especificaciones. Estos procedimientos son costosos en términos de recursos de test. Este invento intenta facilitar la identificación rápida de circuitos o transceptores integrados defectuosos, haciendo posible la identificación a nivel de oblea, y proporcionando además información que se puede usar para mejorar el rendimiento del proceso de fabricación. Las consideraciones económicas son sólo una de las ventajas ofrecidas por el invento presentado. Otras ventajas incluyen un aumento de la detección de fallos, un control mejorado del proceso de fabricación, capacidades diagnósticas, una reducción en la duración del ciclo de testado de un circuito integrado, y una simplificación del desarrollo de los programas de test.

Así pues, la invención se basa en explotar la capacidad de establecer comunicaciones inalámbricas entre los dispositivos bajo test (DUT, en sus siglas en inglés) a nivel de oblea. El objetivo de este test es proporcionar un método rápido y fiable para identificar transceptores defectuosos. Tal método de test reduciría en gran medida el coste asociado al test de producción, dado que esta detección temprana de fallos evita ejecutar una fracción importante de test tradicionales, ahorra costes de empaquetado del circuito integrado, y evita el uso de costosos equipos de test de RF dedicados. Adicionalmente, la detección de un dispositivo defectuoso se puede usar para activar circuitería de test específica (circuitería de autotest interno, o BIST en sus siglas inglesas) para diagnóstico, y además la información obtenida en los test se puede usar para guiar la optimización del proceso de fabricación y para mejorar el rendimiento del proceso.

ANTECEDENTES DE LA INVENCIÓN

Actualmente, sistemas electrónicos completos muy complejos se integran en un solo circuito integrado. La mayor parte de estos sistemas es circuitería digital, que usualmente comprende procesadores multinúcleo, memorias, procesadores dedicados de señal, etc. Se pueden encontrar múltiples ejemplos en aplicaciones de consumo como teléfonos móviles, reproductores de DVD, reproductores multimedia, etc.

Desde el punto de vista de un ingeniero de test, testar un subsistema de RF incluido en un sistema on-chip (SoC) representa un desafío importante. La dificultad está en que cada bloque de radiofrecuencia (RF) tiene un conjunto determinado de especificaciones, que usualmente requieren estrategias de test específicas para su medida. Se puede decir que el test de RF ha heredado todas las dificultades del test analógico, pero añadiendo el problema de manejar señales de muy alta frecuencia. Este marco de trabajo lleva al mismo problema fundamental para los tests analógicos y de RF: testar estos sistemas significa medir funcionalmente un conjunto de especificaciones, mientras que los tests basados en fallos, muy exitosos en el dominio digital, son imposibles de estandarizar en el campo de radiofrecuencia, dado que cada circuito requiere un modelo de fallo específico. Reducir la complejidad y el coste del test de circuitos de radiofrecuencia es todavía una línea de investigación abierta. Trabajos recientes en esta área incluyen modelado de defectos y diagnóstico de fallos, alternate test, Diseño para Test (DfT) y técnicas BIST, etc (M. J. Barragán, G. Huertas, A. Rueda, J. L. Huertas, “ (Some) open problems to incorporate BIST in complex heterogeneous itegrated systems” in Proceedings of the Fifth IEEE International Symposium on Electronic Design, Test and Application (DELTA) , 2010, pp. 8-13) .

Los métodos tradicionales para test de circuitos de RF están basados en especificaciones, es decir, comprueban que algunas o todas las características del sistema están de acuerdo con las especificaciones de diseño. Esta aproximación requiere la aplicación y/o adquisición de señales de alta frecuencia, para lo cual es necesario emplear equipos de test de alta frecuencia y, para dispositivos integrados, es necesario también disponer de un acceso adecuado a los nudos internos del sistema. No obstante, el incremento de la frecuencia de operación de estos sistemas y el aumento de la capacidad de integración hacen muy difícil cumplir con estos requerimientos. El acceso a nodos internos para test es normalmente imposible, e incluso cuando estos nodos son alcanzables puede haber pérdidas importantes de señal en el transporte de éstas hacia o desde el exterior debido a su alta frecuencia. Las soluciones de test BIST serían muy interesantes en este sentido. Las manipulaciones de señal serían internas, eliminando el problema del transporte. Sin embargo, la generación interna de estímulos de test de RF es complicada. Para mitigar este problema se han propuesto las soluciones loopback, que consisten en reinyectar la salida del transmisor al camino de recepción dentro del transceptor. Esto permite que el conversor D/A del transmisor cargue al conversor A/D del receptor, completando un test completamente digital. No obstante, el esquema loopback implica perturbar el funcionamiento normal del sistema: para acomodar la salida del transmisor a la entrada del receptor es necesario desconectar algunos componentes del transmisor del camino de señal y/o introducir un atenuador a la entrada del receptor.

Adicionalmente hay una gran demanda de soluciones de test KGD (known-good-die) que se puedan implementar a nivel de oblea, debido principalmente al incremento de coste que supone el empaquetado de circuitos defectuosos.

DESCRIPCIÓN DE LA INVENCIÓN

Para lograr los objetivos y evitar los inconvenientes indicados anteriormente, la invención consiste en un método y un sistema para llevar a cabo el test de circuitos integrados que forman parte de obleas electrónicas y el uso del método y sistema.

El objetivo principal de este invento es proporcionar un método fiable y rápido para descartar transceptores integrados defectuosos a nivel de oblea mediante el establecimiento de enlaces inalámbricos entre diferentes dados en la oblea, de tal forma que las señales necesarias para testar un determinado transceptor son proporcionadas o leídas por otro de los transceptores de la misma oblea. Estos enlaces inalámbricos permiten un test completo a nivel de sistema de las funciones de transmisión y recepción para cada dispositivo en la oblea, sin la necesidad de costosos equipos de test de RF para generar o leer señales de alta frecuencia, y sin perturbar el funcionamiento normal de los dispositivos bajo test. La invención que se reporta reduce los costes asociados al test de producción, y la detección temprana de circuitos defectuosos evita ejecutar una fracción importante de test tradicionales. Tiene también la ventaja de detectar fallos a nivel de oblea, de forma que se reducen los costes de empaquetado, que usualmente suponen aproximadamente el 25% del coste total del sistema.

La posibilidad de testar la funcionalidad de un transceptor a nivel de oblea proporciona además información sobre el proceso de fabricación. Los resultados del test se pueden mapear sobre la oblea para obtener distribuciones de fallo intra-oblea e inter-oblea. Estas distribuciones se pueden usar para detectar y corregir desviaciones del proceso sistemáticas o no sistemáticas, o para guiar otras estrategias de test como las técnicas de screening.

La detección de un transceptor defectuoso se puede usar también para activar funciones de test internas durante las operaciones de transmisión y recepción. De esta forma se pueden identificar los bloques internos defectuosos dentro del transceptor.

Así en una primera realización de la invención, el método de testado de circuitos integrados de radiofrecuencia a nivel de oblea objeto de la presente invención hace uso de un equipo de test digital de baja frecuencia que al menos comprende dos agujas de test. Las dos agujas, que denominaremos como primera aguja de test y segunda aguja de test, son para enviar y recibir unas secuencias de datos de test que se intercambian entre el equipo...

Reivindicaciones:

1. Método de testado de circuitos integrados de radiofrecuencia a nivel de oblea, que hace uso de un equipo de test digital de baja frecuencia que al menos comprende dos agujas de test, una primera aguja de test y una segunda aguja de test, para enviar y recibir unas secuencias de datos de test entre el equipo de test y los circuitos integrados de una oblea electrónica, y habiéndose seleccionado previamente por parte de una cabeza de test integrada en el equipo de test al menos una pareja de circuitos integrados de la oblea electrónica, se caracteriza porque comprende las siguientes fases:

i) enviar desde la primera aguja de test una secuencia de datos de test hasta un primer circuito integrado de la al menos una pareja previamente seleccionada;

ii) almacenar la secuencia de datos de test en un registro de datos del primer circuito integrado;

iii) enviar desde el primer circuito integrado la secuencia de datos de test hasta un segundo circuito integrado de la pareja previamente seleccionada;

iv) almacenar la secuencia de datos de test en un registro de datos del segundo circuito integrado;

v) enviar desde el segundo circuito integrado la secuencia de datos de test hasta el equipo digital de test

a través de la segunda aguja de test;

vi) comparar la secuencia de datos enviada por el equipo de test en la fase i) con la secuencia de datos recibida por el equipo de test en la fase v) ;

vii) enviar desde la segunda aguja de test una secuencia de datos de test hasta el segundo circuito integrado;

viii) almacenar la secuencia de datos de test en el registro de datos del segundo circuito;

ix) enviar desde el segundo circuito integrado la secuencia de datos de test hasta el primer circuito integrado;

x) almacenar la secuencia de datos de test en el registro de datos del primer circuito;

xi) enviar desde el primer circuito integrado la secuencia de datos hasta el equipo de test a través de la primera aguja de test; y,

xii) comparar la secuencia de datos de test enviada por el equipo de test en la fase vii) con la secuencia de datos recibida por el equipo de test en la fase xi) .

2. Método de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 1, caracterizado porque comprende

• etiquetar la al menos una pareja de circuitos integrados como correcta; y,

• almacenar las posiciones de la al menos una pareja de circuitos integrados,

cuando al comparar las secuencias de datos enviada y recibida por el equipo de test en las fases vi) y xii) , la secuencia de datos de test es la misma.

3. Método de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 1, caracterizado porque comprende:

• etiquetar la al menos una pareja de circuitos integrados como errónea; y,

• almacenar las posiciones de la al menos una pareja de circuitos integrados.

cuando al comparar las secuencias de datos enviada y recibida por el equipo digital de test en las fases vi) y xii) , la secuencia de datos es diferente.

4. Método de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 2, caracterizado porque cuando se ha etiquetado la al menos una pareja de circuitos integrados como correcta, cada uno de los dos circuitos integrados que forman la al menos una pareja de circuitos integrados se empareja con un circuito integrado de la vecindad y se lleva a cabo el procedimiento descrito en las reivindicación 1.

5. Método de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 4, caracterizado porque comprende

• etiquetar el circuito integrado de la vecindad como correcto; y,

• almacenar la posición del circuito integrado de la vecindad,

cuando al comparar las secuencias de datos en las fases vi) y xii) la secuencia de datos de test enviada y recibida por el equipo de test es la misma.

6. Método de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 4, caracterizado porque comprende

• etiquetar el circuito integrado de la vecindad como erróneo; y,

• almacenar la posición del circuito integrado de la vecindad,

cuando al comparar las secuencias de datos en las fases vi) y xii) la secuencia de datos de test enviada y recibida por el equipo de test es diferente.

7. Método de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 1, caracterizado porque comprende monitorizar el funcionamiento de cada módulo que integra el circuito integrado mediante unos sensores de test convencionales integrados en las obleas.

8. Método de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 1, caracterizado porque cuando cada uno de los circuitos integrados integra una antena de test, el envío y recepción de la secuencia de datos de test de las fases iii) y ix) se realiza directamente entre las antenas de test del primer y segundo circuito integrado.

9. Método de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 1, caracterizado porque cuando cada uno de los circuitos integrados no integra una antena de test, el envío y recepción de la secuencia de datos de test de las fases iii) y ix) se realiza mediante unas antenas de test externas posicionadas por la cabeza de test sobre el primer y el segundo circuito integrado.

10. Sistema de testado de circuitos integrados de radiofrecuencia a nivel de oblea, que hace uso de un equipo de test digital de baja frecuencia que al menos comprende dos agujas de test, una primera aguja de test y una segunda aguja de test para el envío y recepción de unas secuencias de datos de test entre el equipo de test y los circuitos integrados de una oblea y de al menos una oblea electrónica compuesta de al menos dos circuitos integrados, caracterizado porque al menos comprende:

• medios de transmisión de las secuencias de datos de test entre los circuitos integrados; y,

• un registro de datos integrado en cada circuito integrado donde se almacena la secuencia de datos de test que intercambian los al menos dos circuitos integrados y el equipo de test de baja frecuencia.

11. Sistema de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 10, caracterizado porque los medios de transmisión de las secuencias de datos de test entre los circuitos integrados comprenden estar seleccionados entre una antena de test integrada en cada uno de los circuitos integrados y una antena externa integrada en la cabeza de test para cada uno de los circuitos integrados.

12. Sistema de testado de circuitos integrados de radiofrecuencia a nivel de oblea, según la reivindicación 10, caracterizado porque comprende sensores de test integrados en la oblea para monitorizar el funcionamiento de unos bloques internos de la oblea.

13. Uso del dispositivo y procedimiento descrito en una cualquiera de las reivindicaciones anteriores para la obtención de mapas de distribución de circuitos integrados erróneos, estando los mapas seleccionados entre un mapa de fallos inter-oblea y un mapa de fallos intra-oblea.

14. Uso del dispositivo y procedimiento descrito en una cualquiera de las reivindicaciones 1 a 12, según la reivindicación 13, caracterizado porque comprende emplear los mapas de distribución de circuitos integrados erróneos para la implementación de técnicas seleccionadas entre técnicas de screening Y técnicas de detección de desviaciones en el proceso de fabricación de las obleas.

Patentes similares o relacionadas:

Capa transpondedora y procedimiento para su producción, del 27 de Mayo de 2020, de Linxens Holding S.A.S: Capa transpondedora con un sustrato de antena , que en un lado de antena está dotada de una antena formada por un conductor de hilos y un chip […]

Procedimiento de fabricación de puentes dieléctricos de identificación sin contacto, del 13 de Mayo de 2020, de Foucault, Jean Pierre: Procedimiento de fabricación de puentes dieléctricos de identificación sin contacto de un paso estandarizado y de una tolerancia ampliada, o de etiquetas […]

Sistemas en paquetes, del 19 de Febrero de 2020, de QUALCOMM INCORPORATED: Un sistema en paquete que comprende: un portador ; un primer chip encima de dicho portador , en el que dicho primer chip […]

Conjunto de máscaras metálicas auto alineadas para depositar, de modo selectivo, capas finas sobre dispositivos y substratos microelectrónicos y método de empleo, del 6 de Noviembre de 2019, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS: La presente invención se refiere a un conjunto de máscaras metálicas auto alineadas para depositar, de modo selectivo, capas finassobre dispositivos […]

Sensor de corrosión que tiene conexiones de cable doble encapsulado y método para fabricarlo, del 11 de Septiembre de 2019, de BAE SYSTEMS PLC: Un método para fabricar un sensor de corrosión, comprendiendo dicho sensor un módulo de chip y un módulo de conexión ambos formados […]

Composición que comprende nanopartículas de polímero para el control de tasas de reacción y procedimiento de fabricación, del 4 de Septiembre de 2019, de THE BOEING COMPANY: Una composición que comprende: una resina termoendurecible; caracterizada porque la composición comprende además: una pluralidad […]

Sensor de huella dactilar, método para la fabricación de un sensor de huella dactilar y terminal, del 27 de Mayo de 2019, de Guangdong OPPO Mobile Telecommunications Corp., Ltd: Un sensor de huella dactilar, que comprende: una unidad de chip que tiene una primera superficie y una segunda superficie opuesta […]

Capa transpondedora y procedimiento para su producción, del 17 de Mayo de 2019, de Linxens Holding S.A.S: Capa transpondedora , en particular para la producción de una estructura laminada configurada, por ejemplo, como tarjeta chip, con un sustrato de antena […]