Método para convertir datos analógicos en datos digitales para un módulo de entrada analógica.

Un método para convertir una señal de entrada analógica recibida por un módulo de entrada analógica en un conjunto de datos digitales,

comprendiendo el método:

recibir, por el módulo de entrada analógica, la señal analógica de entrada;

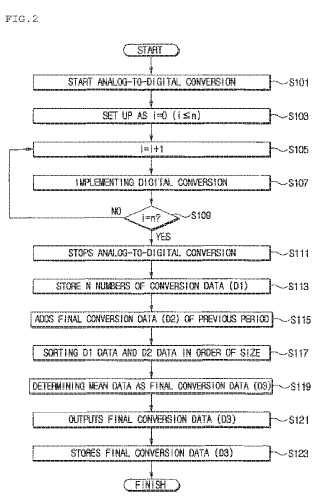

convertir (S101, S103, S105, S107, S109, S111) la señal analógica de entrada en un conjunto de datos digitales (D1) hasta n veces, para cada ko período de conversión de datos, donde n es un número natural que indica los tiempos de conversión y k es un número natural;

estando caracterizado el método por:

almacenar (S113) n números de datos digitales (D1);

incluir (S115) al menos uno o más conjuntos de datos de conversión final (D2) determinados por los k-1o...k-do períodos de conversión anteriores a los n números de datos digitales, donde d es un número natural que corresponde al número de m valores que cumplen la condición n

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E10197081.

Solicitante: LS INDUSTRIAL SYSTEMS CO., LTD.

Nacionalidad solicitante: República de Corea.

Dirección: 1026-6 HOGYE-DONG DONGAN-GU ANYANG-SI GYEONGGI-DO 431-080 REPUBLICA DE COREA.

Inventor/es: SIN,YONG GAK.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M1/06 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 1/00 Conversión analógica/digital; Conversión digital/analógica (conversión de valores analógicos en, o a partir de una modulación diferencial H03M 3/00). › Compensación o prevención continua de la influencia indeseable de parámetros físicos (periódicamente H03M 1/10).

- H03M1/08 H03M 1/00 […] › del ruido.

PDF original: ES-2404531_T3.pdf

Fragmento de la descripción:

Método para convertir datos analógicos en datos digitales para un módulo de entrada analógica.

ANTECEDENTES DE LA INVENCIÓN

Campo La presente descripción se refiere a un método para convertir datos analógicos en datos digitales para un módulo de entrada analógica, y más concretamente, a un método para convertir datos analógicos en datos digitales para un módulo de entrada analógica configurado para emitir de forma estable un conjunto de datos digitales minimizando la influencia del ruido introducido junto con los datos analógicos.

Antecedentes Un módulo de entrada analógica que emplea un ADC (Convertidor Analógico-Digital) ha sido ampliamente utilizado en campos industriales. El módulo de entrada analógica es susceptible a las variaciones de datos según el entorno de la instalación, y la estabilidad de la conversión de datos se puede dañar por un ambiente ruidoso. Recientemente, se han propuesto muchas tecnologías para impedir que sea dañada la estabilidad de la conversión de datos.

La técnica convencional como se ha descrito anteriormente está descrita en, por ejemplo, la publicación de la patente abierta japonesa nº 2000-068833 (publicada el 3 de marzo del 2000) . La técnica enseña un sistema de filtro digital que consta de un convertidor A/D y un medio que elimina una cantidad extremadamente grande (o pequeña) de datos entre los datos de conversión por el número de veces de muestras extraídas por sobre-muestreo y promedia los datos restantes, mediante lo cual los patrones de ruido generados por los ambientes se pueden eliminar digitalmente.

En el módulo convencional de entrada analógica que incluye el sistema de filtración digital, se realizan generalmente varias conversiones analógico-digitales para estabilizar los datos de conversión, y se selecciona un dato estable de entre la pluralidad de los datos de conversión. Por ejemplo, en un módulo que ha obtenido un tiempo para tres tiempos de conversión, un valor medio, exceptuando los valores máximo y mínimo de los resultados de los tres tiempos de conversión, se visualiza como un valor de conversión analógico-digital. Alternativamente, un valor medio de los resultados de los tres tiempos de conversión se puede visualizar como un valor de conversión analógicodigital.

Sin embargo, hay un inconveniente en el módulo convencional de entrada analógica ya que los tiempos de conversión se deben aumentar para mejorar la estabilidad de los datos de conversión. Esto se debe a que el tiempo de la conversión de los datos aumenta en proporción a los tiempos (n) de conversión y por lo tanto, los tiempos (n) de conversión se pueden resolver dentro de una velocidad de conversión dada del módulo. Como resultado, la estabilidad de los datos no se puede buscar convencionalmente a través de aumentar los tiempos de conversión si un producto está capacitado para realizar la determinación de los tiempos (n) de conversión dentro de una velocidad de conversión de una especificación de producto permitido.

Por ejemplo, suponiendo que una velocidad de conversión de una e

permitidos del módulo de entrada analógica son 3 tiempos. Suponiendo que un conjunto de datos de conversión digital ideal para el módulo de entrada analógico del ejemplo es 1.000, se puede obtener un resultado satisfactorio, porque un promedio de tres conjuntos de datos de entrada es 1.000 cuando los tres tiempos de conversión de datos son respectivamente 998, 1002 y 1000.

Sin embargo, en el caso en que se introduce una conversión de datos de 950, 1000 y 1002, el promedio de los tres datos se convierte en 984 debido a la influencia del ruido, de manera que se puede obtener un resultado insatisfactorio en contra de una conversión de datos deseada por el usuario.

Por lo tanto, con el fin de evitar las situaciones anteriormente mencionadas, un diseñador puede seleccionar un método de selección de un valor promedio (media) que prescinda de los valores máximo y mínimo. Sin embargo, incluso en este caso, si dos valores continuos se ven afectados por el ruido, no se puede obtener un resultado deseado por el diseñador. Por lo tanto, es muy difícil esperar cualquier estabilidad más alta a menos que se incrementen los tiempos (n) de conversión. Además, incrementar los tiempos (n) de conversión incrementa inevitablemente el tiempo de conversión de datos para dar lugar a un problema de no satisfacer una velocidad de conversión especificada por la especificación. Como consecuencia, se puede dar el caso de corrección del hardware en el peor de los casos, y si no se da nunca el caso, es inevitable aumentar el tiempo y el coste.

Alternativamente, entre los métodos de estabilizar la conversión de datos en el módulo de entrada analógica, puede haber un método de estabilizar los datos, considerando que ha ocurrido un cambio en los datos solamente cuando el cambio a un bit del nivel más bajo en el convertidor analógico-digital es mayor que un nivel predeterminado. Este método ha prestado una histéresis característica a una señal de entrada, el método de la cual solamente es sensible a un caso donde la fluctuación del dato es mayor que un valor predeterminado, de tal manera que una unidad de fluctuación del dato es reconocida como el valor predeterminado. Por lo tanto, se puede generar un fenómeno donde el dato fluctúa para mostrar una forma de escalera con una anchura del valor predeterminado, para de este modo crear un problema de un control preciso que no sea apropiado.

Con el fin de obviar uno o más de los problemas anteriormente mencionados, se ha requerido un método de conversión digital apropiado para un control preciso y para estabilizar la conversión de datos por la técnica anterior convencional relevante, libre de fluctuaciones en los tiempos de conversión, velocidad de conversión y tiempo de conversión en un módulo de entrada analógica.

La patente US 2009/0066554 A1 describe métodos, sistemas y dispositivos de muestreo pseudo-múltiple para la conversión analógico-digital.

COMPENDIO La presente descripción se refiere a un método para convertir un conjunto de datos analógicos en un conjunto de datos digitales para un módulo de entrada analógica. La presente invención proporciona un método como el definido en la reivindicación 1 adjunta.

Según la presente descripción, se lleva a cabo un método para convertir un conjunto de datos analógicos en un conjunto de datos digitales para un módulo de entrada analógica, donde un módulo de entrada analógica convierte un conjunto de datos analógicos introducidos hasta n veces predeterminadas para cada período de conversión de datos en un conjunto de datos digitales, y basándose en los n números de datos digitales convertidos y un período (ko) de conversión actual, al menos uno o más datos de conversión final determinados para un período (k-1º, ..k-do, donde d es un número natural) de conversión anterior se clasifican por orden de tamaño, y se determina y emite un valor correspondiente a un nivel medio entre los datos clasificados como un conjunto de datos de conversión final del período (ko) de conversión actual.

Como consecuencia, la influencia del ruido introducido en el módulo de entrada analógica se puede minimizar para producir de forma estable un conjunto de datos digitales a partir de un conjunto de datos analógicos.

Por lo tanto, es un objetivo de la presente descripción un método para convertir datos analógicos en datos digitales para un módulo de entrada analógica configurado para producir de forma estable un conjunto de datos digitales minimizando, en un módulo de entrada analógica, la influencia del ruido introducido junto con los datos analógicos.

En un aspecto general de la presente descripción, se proporciona un método para convertir datos analógicos en datos digitales para un módulo de entrada analógica, comprendiendo el método: recibir, por un módulo de entrada analógica, un conjunto de datos analógicos; convertir el conjunto de datos analógicos introducido en un conjunto de datos digitales (D1) hasta un número predeterminado (n, siendo dicha n un número natural) de veces conversión para cada período de conversión de datos (ko, siendo k un número natural) ; obtener por lo menos uno o más datos (D2) de conversión final determinados para períodos de conversión anteriores (k-1º, ..k-do, siendo dicha d un número natural) ; clasificar los n números de datos digitales (D1) convertidos y los al menos uno o más datos obtenidos de conversión final (D2) por orden de tamaño; determinar un valor correspondiente a un nivel medio entre los datos clasificados como datos (D3) de conversión final del período de conversión actual; y producir los datos (D3)... [Seguir leyendo]

Reivindicaciones:

1. Un método para convertir una señal de entrada analógica recibida por un módulo de entrada analógica en un conjunto de datos digitales, comprendiendo el método:

recibir, por el módulo de entrada analógica, la señal analógica de entrada; convertir (S101, S103, S105, S107, S109, S111) la señal analógica de entrada en un conjunto de datos digitales (D1) hasta n veces, para cada ko período de conversión de datos, donde n es un número natural que indica los tiempos de conversión y k es un número natural;

estando caracterizado el método por:

almacenar (S113) n números de datos digitales (D1) ; incluir (S115) al menos uno o más conjuntos de datos de conversión final (D2) determinados por los k1º…k-do períodos de conversión anteriores a los n números de datos digitales, donde d es un número natural que corresponde al número de m valores que cumplen la condición n<m<2n basándose en el período de conversión actual, donde m es un número natural que indica los tiempos de conversión; clasificar (S117) los n números de conjuntos de datos digitales convertidos (D1) y los al menos uno o más conjuntos de datos de conversión final incluidos (D2) determinados por los períodos de conversión anteriores por orden de tamaño;

determinar (S119) un valor correspondiente a un valor de nivel medio entre los datos ordenados como un conjunto de datos de conversión final (D3) del período de conversión actual; emitir (S121) el conjunto de datos de conversión final (D3) ; y almacenar (S123) el conjunto de datos de conversión final (D3) para el período siguiente.

Patentes similares o relacionadas:

Dispositivo de captura de imagen de semiconductores, instrumento electrónico y dispositivo de conversión analógico a digital, del 29 de Abril de 2020, de SONY CORPORATION: Un dispositivo de captura de imagen de semiconductores que comprende: una sección de píxel que tiene una pluralidad de píxels ; un comparador […]

Dispositivo de resincronización de señales analógicas obtenidas por conversión, con unos convertidores digital-analógico DDR, de señales digitales sincronizadas, del 28 de Febrero de 2018, de THALES: Dispositivo de resincronización de una pluralidad de señales analógicas (DAC_OUTPUTA, DAC_OUTPUTB) obtenidas por conversión, con unos convertidores digital-analógico […]

Sistema de control de cargas eléctricas que recibe al menos dos fases de una red de distribución eléctrica, del 16 de Noviembre de 2016, de Groupe Brandt: Sistema de control de cargas eléctricas que recibe al menos dos fases (PH1, PH2) de una red de distribución eléctrica, constituyendo cada […]

Métodos y aparatos para la estimación y la compensación de los errores de no linealidad, del 29 de Diciembre de 2015, de Signal Processing Devices Sweden AB: Una unidad de estimación (30, 30a-c) para estimar un error de no linealidad de un circuito de conversión , en la que el circuito de conversión […]

Métodos y aparatos para la estimación y la compensación de los errores de no linealidad, del 29 de Diciembre de 2015, de Signal Processing Devices Sweden AB: Una unidad de estimación (30, 30a-c) para estimar un error de no linealidad de un circuito de conversión , en la que el circuito de conversión […]

Convertidor analógico/digital con una topología de SAR así como procedimiento correspondiente, del 6 de Junio de 2012, de Rutronik Elektronische Bauelemente GmbH: Convertidor analógico/digital para la determinación del valor de medición absoluto con - un microcontrolador ,

- una topología de SAR […]

Convertidor analógico/digital con una topología de SAR así como procedimiento correspondiente, del 6 de Junio de 2012, de Rutronik Elektronische Bauelemente GmbH: Convertidor analógico/digital para la determinación del valor de medición absoluto con - un microcontrolador ,

- una topología de SAR […]

METODO Y APARATO PARA LA CORRECCION DE ERRORES DE DESVIACION DE C.C. EN CONVERTIDORES DIGITALES A ANALOGICOS., del 16 de Agosto de 2006, de QUALCOMM INCORPORATED: Un circuito de corrección de desviación c.c. para eliminar errores de desviación c.c. de señales de transmisión en banda base en un dispositivo […]

METODO Y DISPOSITIVO PARA MUESTREAR SEÑALES ANALOGICAS., del 1 de Noviembre de 2002, de TELEFONAKTIEBOLAGET LM ERICSSON: PROCEDIMIENTO Y DISPOSITIVO PARA LE MUESTREO DE UNA SEÑAL ANALOGICA (U(T)) OBTENIENDO PRIMERAS SECUENCIA DE VALORES DE MUESTRA DIFERENCIADOS (S 1 A I (T), (S 1 A Q […]

Atenuación de una anomalía de fase en una señal de salida de convertidor analógico-digital, del 27 de Julio de 2016, de Airbus Defence and Space Limited: Un procedimiento de atenuación de una anomalía de fase en una señal de salida de convertidor analógico-digital ADC, comprendiendo el procedimiento: recibir una […]