Método y aparato para la desmodulación de señales moduladas con modulación binaria por desplazamiento diferencial de fase.

Un método para la desmodulación de una señal de modulación binaria por desplazamiento diferencial de fase DBPSK,

comprendiendo dicho método las etapas de:

- recibir una señal DBPSK que ha sido codificada por canal utilizando un código de convolución en el lado del transmisor;

- generar a partir de dicha señal DBPSK (SRF) un componente en fase (Ia) y un componente en cuadratura de fase (Qa);

- procesar por separado dicho componente en fase (Ia) y dicho componente en cuadratura de fase (Qa), mediante aplicar conversión analógico a digital de 1 bit, por lo tanto generando independientemente un primer bit único que representa un componente en fase digital (Id) de dicha señal DBPSK y un segundo bit único que representa un componente en cuadratura de fase digital (Qd) de dicha señal DBPSK;

caracterizado por, a continuación

- llevar a cabo independientemente una descodificación diferencial de

a) dicho componente en fase digital (Id), en el que se procesan dos primeros bits únicos sucesivos del componente en fase digital, para obtener un componente en fase digital descodificado de un único bit (Idd), y

b) dicho componente en cuadratura de fase digital (Qd), en el que se procesan dos sucesivos segundos bits únicos del componente en cuadratura de fase digital, para obtener un componente en cuadratura de fase digital descodificado de un único bit (Qdd);

- combinar dicho componente en fase digital descodificado de un único bit (Idd) y dicho componente en cuadratura de fase digital descodificado de un único bit (Qdd) para formar una señal de softbit indicativa de no más de

i) los valores de bit de los componentes en fase (Idd) y en cuadratura de fase (Qdd) digitales descodificados, y

ii) si los valores de bit son o no iguales;

- decidir acerca de un valor de dicha señal DBPSK mediante llevar a cabo una descodificación de máxima probabilidad utilizando un procedimiento de descodificación de Viterbi de decisión flexible, donde una métrica de entrada al procedimiento de descodificación de Viterbi está formada por la señal de softbit; y

- aplicar por separado descodificación de máxima probabilidad a dicho componente en fase digital descodificado (Idd) y a dicho componente en cuadratura de fase digital descodificado (Qdd), y someter patrones de bit descodificados de dichos componentes en fase y en cuadratura de fase a cálculos de suma de comprobación,

- en el que la decisión acerca de un valor de dicha señal de DBPSK se basa en cálculos de suma de comprobación independientes de la señal de softbit, del componente en fase digital descodificado (Idd) y del componente en cuadratura de fase digital descodificado (Qdd).

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E09177529.

Solicitante: IHP GmbH-Innovations for High Performance Microelectronics / Leibniz-Institut für innovative Mikroelektronik.

Nacionalidad solicitante: Alemania.

Dirección: IM TECHNOLOGIEPARK 25 15236 FRANKFURT / ODER ALEMANIA.

Inventor/es: PETRI,MARKUS, GRASS,ECKHARD DR, PIZ,MAXIM.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04L27/233 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 27/00 Sistemas de portadora modulada. › que utilizan una demodulación no coherente.

PDF original: ES-2511031_T3.pdf

Fragmento de la descripción:

Método y aparato para la desmodulación de señales moduladas con modulación binaria por desplazamiento diferencial de fase.

CAMPO DE LA INVENCIÓN

La presente Invención se refiere a un método, un aparato y un producto de programa Informático para la desmodulación de una señal de modulación binaria por desplazamiento diferencial de fase (DBPSK, differential binary phase shift keying).

ANTECEDENTES DE LA INVENCIÓN

DPSK es una técnica de modulación digital que puede ser utilizada para codificar información en una señal antes de transmitir la señal a uno o varios receptores. En una señal modulada con DPSK, la información se transporta mediante una transición entre diferentes estados digitales, en lugar de mediante estados digitales absolutos. Técnicas específicas de modulación DPSK incluyen DBPSK y codificación por desplazamiento diferencial de fase en cuadratura (DQPSK, differential quadrature phase shift keying).

En la modulación DBPSK, la fase de una señal portadora de amplitud constante se desplaza entre dos posiciones, tales como 0o y 180°. De este modo, se proporcionan dos señales digitales diferentes, por ejemplo, un estado binario "0" en 0o y un estado binario "1" en 180°. La información se codifica diferencialmente en la transición de un estado al siguiente, y/o en la ausencia de dicha transición. De este modo, no es necesario recuperar o rastrear la señal portadora dentro del receptor, tal como requiere un receptor que esté configurado para desmodular señales convencionales moduladas con desplazamiento de fase. Por el contrario, el receptor necesita solamente identificar el desplazamiento de fase relativo entre dos bits adyacentes, para identificar la información contenida en una señal codificada diferencialmente. Esto tiende a simplificar el diseño del receptor. Por lo tanto, en el caso de una codificación diferencial, la fase de un símbolo precedente se multiplica por la fase del símbolo actual.

Un típico receptor para una señal DBPSK puede comprender un elemento frontal de radiofrecuencia (RF) analógico, en el que la señal recibida modulada se transforma desde la banda de RF a la banda base inferior. La señal de banda base obtenida se digitaliza mediante un convertidor de analógico a digital (A/D) y a continuación se procesa adicionalmente. Sin embargo, es posible asimismo desmodular la señal codificada diferencialmente en el dominio analógico, proporcionando circuitos o etapas de procesamiento adicionales.

La codificación diferencial se puede utilizar ventajosamente si no se implementa sincronización de fase entre un transmisor y un receptor. Sin embargo, la determinación de la diferencia de fase requiere la suficiente resolución de la conversión A/D aplicada. Si la señal DBPSK está cuantificada en solamente 1 bit, la desmodulación deja de ser posible a una diferencia de fase de aproximadamente 90° ó 270°, entre el transmisor y el receptor. Por lo tanto, la desmodulación DBPSK involucra un problema porque se requiere una determinación analógica de la diferencia de fase en una complejidad de circuitos correspondientemente superior, o bien se requiere un convertidor A/D con la suficiente resolución. Dicho convertidor AID puede ser inconveniente para sistemas con altas velocidades de transferencia de datos (por ejemplo, >1 Gbit/s), debido al consumo de energía relativamente elevado y a la complejidad de los circuitos, y por lo tanto es de utilización limitada para módulos económicos de alimentación por baterías.

El documento US 6 381 288 B da a conocer un método y un aparato para recuperar datos de una señal DBPSK, en los que el receptor desmodula la señal DBPSK mediante un desmodulador en cuadratura, en componentes en fase y en cuadratura de fase independientes, que se transforman en dos señales digitales utilizando convertidores A/D de 2 bits. A continuación, se descodifican muestras de estas señales digitales, de acuerdo con un algoritmo de criterios de máxima probabilidad, y se adoptan decisiones basándose en la constelación de señal que identifica los datos originales transmitidos.

El documento US 2007/0018717 A1 da a conocer un dispositivo de evaluación, que reproduce componentes I y Q mediante la utilización de estimación de canal, en el que los datos modulados se reproducen a partir de los componentes I y Q.

Wu describe, en Milcom 98.proceedings, volumen 3, 18 de octubre de 1998, páginas 730 a 735, un desmodulador BPSK con un frontal A/D de 1 bit, en el que la señal recibida se transforma mediante un convertidor A/D de 1 bit, antes de la generación de los componentes I y Q. La estimación de máxima probabilidad se calcula independientemente para ambos componentes I y Q, decidiéndose el valor de la señal BPSK recibida en base a la suma de los componentes I y Q del proceso.

El documento US 2007/024477 A1, de Qing y otros, y el documento de IEEE "16th International Symposium on Personal, Indoor and Moblle Radio Communications", Berlín, 11 a 14 de septiembre de 2005, volumen 4, páginas 2586 a 2590, dan a conocer soluciones de desmodulador, donde la señal recibida se digitaliza en primer lugar a través de un limitador estricto, y a continuación se separa en componentes I y Q.

El documento US 6 381 288 B1 describe un desmodulador para una señal DBPSK, en el que los componentes I y Q se muestrean Independientemente, y a continuación se codifican en función de un algoritmo de criterios de máxima probabilidad.

El documento EP 1 791 312 A2 da a conocer un método para la desmodulación de una señal DBPSK, de acuerdo con el preámbulo de la reivindicación 1.

RESUMEN DE LA INVENCIÓN

Por lo tanto, un objetivo de la presente invención es dar a conocer una técnica de desmodulación de DBPSK simplificada, con menos complejidad de los circuitos y menos consumo de energía.

Este objetivo se consigue mediante un método para la desmodulación de una señal de DBPSK, de acuerdo con la reivindicación 1.

Adicionalmente, el objetivo anterior se consigue mediante un aparato para la desmodulación de una señal de DBPSK, de acuerdo con la reivindicación 5.

Además, el objetivo anterior se consigue mediante un producto de programa informático, que comprende medios de código para llevar a cabo el las etapas del método de la reivindicación 1, cuando se ejecuta en un dispositivo informático.

Por consiguiente, se aplica una conversión independiente AID de 1 bit y un proceso subsiguiente de desmodulación para cada uno de los componentes en fase y en cuadratura de fase, de tal modo que ya no son necesarios convertidores AID complejos, y los valores de desmodulación cuantificados con 1 bit se pueden utilizar como información de entrada para una operación de descodificación de máxima probabilidad de por lo menos un descodificador, o para un cálculo de suma de comprobación.

La consideración combinada de los componentes en fase y en cuadratura de fase permite la conversión de los valores descodificados diferencialmente en valores de softbit, que incluyen consideraciones de fiabilidad. Adicionalmente, en las realizaciones del método, se pueden utilizar independientemente las componentes en fase y en cuadratura de fase para decidir sobre el valor de la señal de entrada DBPSK, basándose en la tasa de errores determinada o en la descodificación de máxima probabilidad (tal como, por ejemplo, descodificación de Viterbi).

La señal DBPSK es una señal recibida codificada por canal, donde la codificación por canal se puede basar en un código de convolución.

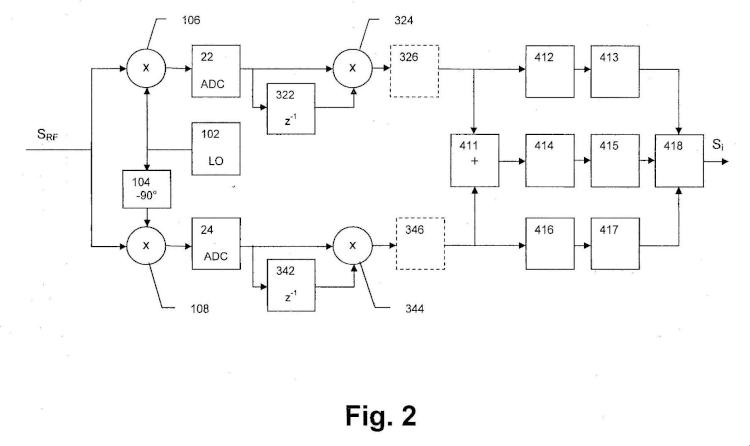

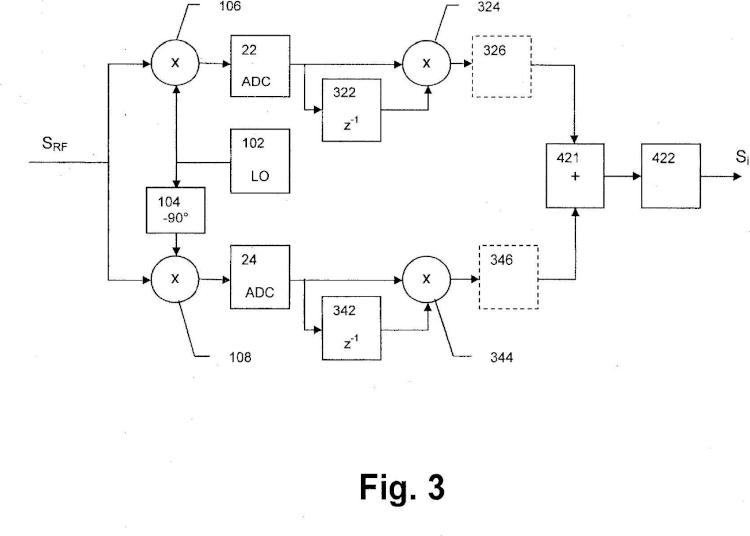

De acuerdo con un primer aspecto, la decisión acerca del valor de la señal DBPSK se puede obtener mediante la aplicación de descodificación de máxima probabilidad con softbits como métricas de entrada, donde los softbits se generan sumando el componente en fase procesado y el componente en cuadratura de fase procesado.

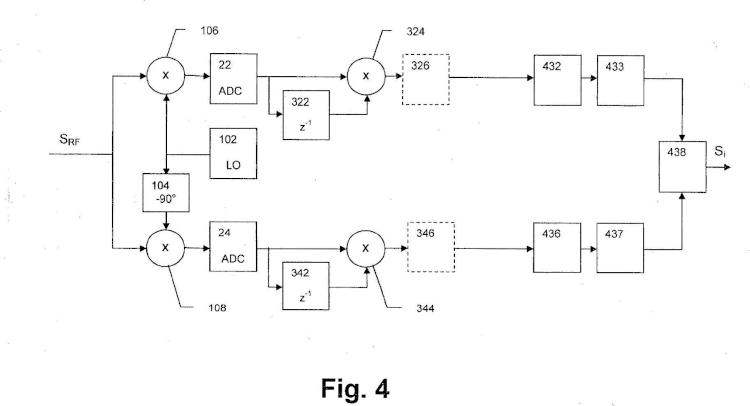

De acuerdo con un segundo aspecto, la decisión acerca del valor de la señal DBPSK se puede realizar aplicando independientemente descodificación de máxima probabilidad al componente en fase procesado y al componente en cuadratura de fase procesado, y decidiendo en función de cálculos de suma de comprobación, sobre la validez de los resultados de descodificación obtenidos. De acuerdo con una implementación específica, los cálculos de suma de comprobación se pueden llevar a cabo para bloques parciales de los componentes en fase y en cuadratura de fase, y decidir acerca de la validez basándose en dichos bloques parciales.

De acuerdo con un tercer aspecto, la decisión sobre la señal DBPSK se puede realizar aplicando independientemente descodificación de máxima probabilidad al componente en fase procesado, al componente en cuadratura de fase procesado,... [Seguir leyendo]

Reivindicaciones:

1. Un método para la desmodulación de una señal de modulación binarla por desplazamiento diferencial de fase DBPSK, comprendiendo dicho método las etapas de:

- recibir una señal DBPSK que ha sido codificada por canal utilizando un código de convolución en el lado del transmisor;

- generar a partir de dicha señal DBPSK (Srf) un componente en fase (la) y un componente en cuadratura de fase

(Qa);

- procesar por separado dicho componente en fase (la) y dicho componente en cuadratura de fase (Qa), mediante aplicar conversión analógico a digital de 1 bit, por lo tanto generando independientemente un primer bit único que representa un componente en fase digital (Id) de dicha señal DBPSK y un segundo bit único que representa un componente en cuadratura de fase digital (Qd) de dicha señal DBPSK;

caracterizado por, a continuación

- llevar a cabo independientemente una descodificación diferencial de

a) dicho componente en fase digital (Id), en el que se procesan dos primeros bits únicos sucesivos del componente en fase digital, para obtener un componente en fase digital descodificado de un único bit (ldd), y

b) dicho componente en cuadratura de fase digital (Qd), en el que se procesan dos sucesivos segundos bits únicos del componente en cuadratura de fase digital, para obtener un componente en cuadratura de fase digital descodificado de un único bit (Qdd);

- combinar dicho componente en fase digital descodificado de un único bit (ldd) y dicho componente en cuadratura de fase digital descodificado de un único bit (Qdd) para formar una señal de softbit indicativa de no más de

i) los valores de bit de los componentes en fase (ldd) y en cuadratura de fase (Qdd) digitales descodificados,

y

ii) si los valores de bit son o no iguales;

- decidir acerca de un valor de dicha señal DBPSK mediante llevar a cabo una descodificación de máxima probabilidad utilizando un procedimiento de descodificación de Viterbi de decisión flexible, donde una métrica de entrada al procedimiento de descodificación de Viterbi está formada por la señal de softbit; y

- aplicar por separado descodificación de máxima probabilidad a dicho componente en fase digital descodificado (ldd) y a dicho componente en cuadratura de fase digital descodificado (Qdd), y someter patrones de bit descodificados de dichos componentes en fase y en cuadratura de fase a cálculos de suma de comprobación,

- en el que la decisión acerca de un valor de dicha señal de DBPSK se basa en cálculos de suma de comprobación independientes de la señal de softbit, del componente en fase digital descodificado (ldd) y del componente en cuadratura de fase digital descodificado (Qdd).

2. El método acorde con la reivindicación 1, que comprende además llevar a cabo dichos cálculos de suma de comprobación para bloques parciales de dichos componentes en fase y en cuadratura de fase procesados, y decidir acerca de dicha validez en base a dichos bloques parciales.

3. El método acorde con la reivindicación 2, que comprende además realizar dicha decisión acerca de la validez después de cada bloque parcial.

4. El método acorde con cualquiera de las reivindicaciones 1 ó 2, en el que dicho cálculo de suma de comprobación está basado en un código de redundancia cíclica.

5. Un aparato para la desmodulación de una señal de modulación binaria por desplazamiento diferencial de fase DBPSK, comprendiendo dicho aparato:

- medios de recepción para recibir una señal DBPSK que ha sido codificada por canal utilizando un código de convolución en el lado del transmisor;

- medios de desmodulación (10) para generar, a partir de dicha señal DBPSK (Srf), un componente en fase (la) y un componente en cuadratura de fase (Qa); y

- medios de procesamiento (22, 24, 32, 34) para procesar independientemente dicho componente en fase y dicho componente en cuadratura de fase mediante la aplicación de conversión analógico a digital de 1 bit, por lo tanto proporcionando por separado un primer bit único que representa un componente en fase digital (Id) de dicha señal DBPSK y un segundo bit único que representa un componente en cuadratura de fase digital (Qd) de dicha señal DBPSK;

caracterizado porque

- dichos medios de procesamiento están configurados adicionalmente para la subsiguiente descodificación diferencial de

a) dicho componente en fase digital (Id), en el que se procesan dos primeros bits únicos sucesivos del componente en fase digital, para obtener un componente en fase digital descodificado de un único bit (Idd), y

(b) dicho componente en cuadratura de fase digital (Qd), en el que se procesan dos sucesivos segundos bits únicos del componente en cuadratura de fase digital, para obtener un componente en cuadratura de fase digital descodificado de un único bit (Qdd);

- medios de combinación (411; 421) para combinar dicho componente en fase digital descodificado de un único bit (Idd) y dicho componente en cuadratura de fase digital descodificado de un único bit (Qdd) para formar una señal de softbit indicativa de no más de

i) los valores de bit de los componentes en fase (Idd) y en cuadratura de fase (Qdd) digitales descodificados,

y

ii) si los valores de bit son o no iguales; y

- medios de decisión (418) para decidir acerca de un valor de dicha señal de DBPSK, mediante

llevar a cabo una descodificación de máxima probabilidad utilizando un procedimiento de descodificación de Viterbi de decisión flexible, en el que una métrica de entrada al procedimiento de descodificación de Viterbi está formado por la señal de softbit;

aplicar por separado descodificación de máxima probabilidad a dicho componente en fase digital descodificado (Idd) y a dicho componente en cuadratura de fase digital descodificado (Qdd). y someter patrones de bit descodificados de dichos componentes en fase y en cuadratura de fase a cálculos de suma de comprobación,

en el que la decisión acerca de un valor de dicha señal de DBPSK se basa en cálculos de suma de comprobación independientes de la señal de softbit, del componente en fase digital descodificado (Idd) y del componente en cuadratura de fase digital descodificado (Qdd).

6. Un producto de programa informático que comprende medios de código para llevar a cabo las etapas del método de la reivindicación 1, cuando se ejecuta en un dispositivo informático.

Patentes similares o relacionadas:

Uso de decisiones de bits fáciles para mejorar la desmodulación DPSK de datos SPS, del 30 de Abril de 2019, de QUALCOMM INCORPORATED: Un procedimiento de desmodulación de datos, dicho procedimiento que comprende: proporcionar una primera señal de entrada que comprende una palabra de […]

Procedimiento y módulo de estimación del sesgo frecuencial en un sistema de telecomunicaciones digitales, del 4 de Abril de 2019, de SIGFOX: Procedimiento de estimación de un sesgo frecuencial que afecta a una señal digital representativa de una trama de símbolos emitida por un terminal […]

Detección de un desplazamiento de frecuencia en un sistema DVB-H, del 5 de Febrero de 2019, de Nokia Technologies OY: Un método que comprende: recibir un símbolo de multiplexación por división de frecuencia ortogonal, OFDM, que comprende una pluralidad de señales en un peine de dominio […]

MÉTODO Y SISTEMA PARA ADQUISICIÓN DE ENLACE INALÁMBRICO CON MÚLTIPLES ANTENAS, del 28 de Enero de 2016, de PONTIFICIA UNIVERSIDAD CATÓLICA DE CHILE: Se describe un sistema MIMO de portadora única y un método correspondiente. El transmisor transmite un preámbulo que comprende secuencias de símbolos, en donde cada secuencia […]

Procedimiento y dispositivo para determinar una información extrínseca, del 6 de Mayo de 2015, de ROHDE & SCHWARZ GMBH & CO. KG: Procedimiento para determinar una información extrínseca para una hipótesis de símbolo de un símbolo en un determinado instante, que se alimenta a una modulación de fase diferencial […]

Método y aparato para la compensación de ruido de fase en receptores digitales, del 26 de Marzo de 2014, de OPTIS WIRELESS TECHNOLOGY, LLC: Un procedimiento para la compensación del ruido en una señal recibida, que comprende las etapas de: recibir una señal recibida en un desmodulador, estando […]

Control de potencia automático para un sistema de comunicación de acceso múltiple por division de código (CDMA), del 2 de Octubre de 2013, de INTERDIGITAL TECHNOLOGY CORPORATION: Metodo para controlar niveles de potencia de transmisión de una unidad de abonado en un acceso múltiple pordivisión de código, CDMA, el metodo […]

TELEFONO MOVIL PROVISTO DE UN CIRCUITO DE DESMODULACION CON OSCILADOR LOCAL MEJORADO, del 16 de Septiembre de 2007, de TCL & ALCATEL MOBILE PHONES LIMITED: Teléfono móvil provisto de un circuito de desmodulación que incluye un oscilador local y un mezclador con una entrada de oscilador local y […]

TELEFONO MOVIL PROVISTO DE UN CIRCUITO DE DESMODULACION CON OSCILADOR LOCAL MEJORADO, del 16 de Septiembre de 2007, de TCL & ALCATEL MOBILE PHONES LIMITED: Teléfono móvil provisto de un circuito de desmodulación que incluye un oscilador local y un mezclador con una entrada de oscilador local y […]