INTERCONEXIÓN DE DISPOSITIVOS ELECTRÓNICOS CON CONDUCTORES ELEVADOS.

Procedimiento de fabricación de un elemento de interconexión (160;

160') para poner en contacto dispositivos electrónicos, incluyendo el procedimiento las etapas siguientes: formar una pluralidad de conductores (130) sobre una superficie principal (110) de un primer sustrato (105) de silicio monocristalino tras tratar la superficie principal para controlar una adhesión de los conductores sobre la superficie principal, presentando cada conductor un primer extremo (130a) y un segundo extremo (130b), acoplar el segundo extremo de cada conductor con un segundo sustrato (140), y separar entre sí el segundo sustrato y el primer sustrato para extender los conductores (130') entre el primer sustrato y el segundo sustrato, caracterizado porque la etapa de tratamiento de la superficie principal incluye: formar un conjunto de regiones de silicio poroso (120) que se extienden desde la superficie principal hacia el interior del primer sustrato

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2007/052497.

Solicitante: ELES SEMICONDUCTOR EQUIPMENT S.P.A.

RISE TECHNOLOGY S.R.L.

Nacionalidad solicitante: Italia.

Dirección: FRAZ. PIAN DI PORTO, ZONA IND.LE BODOGLIE, 148/1/Z 06059 TODI (PERUGIA) ITALIA.

Inventor/es: BALUCANI,MARCO.

Fecha de Publicación: .

Fecha Solicitud PCT: 16 de Marzo de 2007.

Fecha Concesión Europea: 13 de Octubre de 2010.

Clasificación Internacional de Patentes:

- H01L21/48C4C

Clasificación PCT:

- H01L21/48 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 21/00 Procedimientos o aparatos especialmente adaptados para la fabricación o el tratamiento de dispositivos semiconductores o de dispositivos de estado sólido, o bien de sus partes constitutivas. › Fabricación o tratamiento de partes, p. ej. de contenedores, antes del ensamblado de los dispositivos, utilizando procedimientos no cubiertos por un único grupo de H01L 21/06 - H01L 21/326.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia.

PDF original: ES-2359919_T3.pdf

Fragmento de la descripción:

CAMPO TÉCNICO

La presente invención se refiere en general al campo de la electrónica. Más en particular, la presente invención se refiere a la interconexión de dispositivos electrónicos.

ANTECEDENTES

Los dispositivos electrónicos deben interconectarse generalmente entre sí, con el fin de llevar a cabo una serie de tareas. Un ejemplo es un módulo multichip (MCM), en el que una pluralidad de circuitos integrados en chips correspondientes de materiales semiconductores se empaquetan en un único montaje electrónico. Otro ejemplo es una tarjeta de sonda, que se utiliza para poner en contacto circuitos integrados a nivel de oblea para ponerlos a prueba.

Se han propuesto varias soluciones para conseguir el resultado deseado. En particular, una técnica específica conocida en la técnica se basa en la elevación de conductores flexibles, véase, por ejemplo, la patente US nº 5.763.941.

Por ejemplo, el documento EP-A-0 352 020 da a conocer un sistema para interconectar múltiples chips por medio de un soporte semiconductor. Para ello, se conectan unas pastillas conductoras de cada chip a unas partes texturizadas correspondientes de unas pastillas conductoras previstas sobre el soporte (enfrentadas entre sí). Con el fin de aumentar la adaptabilidad mecánica de la estructura obtenida de este modo, el documento EP-A-0 352 020 enseña a disponer una capa localizada de material aislante entre cada chip y una parte de sus pastillas; el material aislante se selecciona para presentar relativamente poca o ninguna adhesión con las pastillas de chip. El chip se presiona contra el soporte, conectando de este modo las partes de las pastillas de chip que se apoyan sobre el material aislante a las pastillas de soporte correspondientes; el chip se levanta entonces ligeramente para separarlo del soporte (por ejemplo, 2 mm). De esta manera, las pastillas de chip se desprenden de la capa aislante, extendiéndolas de ese modo entre el chip y el soporte (con el material aislante que también puede retirarse en el extremo). La estructura propuesta en el documento EP-A-0 352 020 permite resistir los esfuerzos provocados por tensiones mecánicas o térmicas.

Una variación de la misma técnica se propone en el documento EP-A-0 870 325. En este caso, se emplea una capa que puede retirarse para facilitar la elevación de los conductores. Más específicamente, los conductores se forman sobre una lámina de múltiples capas (que consiste en una lámina dieléctrica intercalada entre dos capas de metal); cada conductor está conformado como una tira, que se extiende entre un extremo de punta y un extremo terminal. La capa de metal bajo los conductores se graba entonces, para separar las tiras de la lámina dieléctrica. Sin embargo, el extremo de punta de cada conductor es ligeramente más grande que su tira, de modo que el procedimiento de grabado deja un pequeño botón bajo el mismo; este botón proporciona una adhesión muy pequeña del extremo de punta a la capa dieléctrica (justo lo suficientemente fuerte para retener el extremo de punta contra las fuerzas gravitacional y de aceleración en la manipulación normal). Por otro lado, el extremo terminal de cada conductor es mucho más grande, de tal modo que el mismo procedimiento de grabado deje un botón más grande bajo el mismo; este botón fija de manera segura el extremo terminal a la lámina de múltiples capas (conectando al mismo tiempo el conductor, a través de un orificio pasante, a un terminal correspondiente formado en su superficie opuesta). El componente obtenido de este modo está alineado con una oblea, y los extremos de punta están unidos a contactos correspondientes de la oblea. Tal como se ha expuesto anteriormente, la lámina de múltiples capas y la oblea están separadas, para extender los conductores entre las mismas (con los extremos de punta de los conductores que se desprenden fácilmente de la lámina de múltiples capas).

En cualquier caso, los conductores utilizados en elementos de interconexión se protegen generalmente mediante un material dieléctrico (preferentemente del tipo elástico). Por ejemplo, el documento US-A-3.795.037 da a conocer un conector con conductores resilientes, que están incrustados en un material elastomérico; la estructura obtenida de este modo permite conectar dispositivos electrónicos, sin requerir ningún control preciso de los ocho conductores. El conector se produce definiendo los conductores en una serie de marcos (por ejemplo, mediante fresado químico). A continuación, se forma una pila formada por múltiples marcos con separadores interpuestos, y se sujeta entre dos placas. En este punto, se inyecta un líquido elastomérico en la cavidad definida por las placas, y se cura; al final, las placas se retiran para obtener la estructura deseada.

La misma técnica se aplica también en el documento EP-A-0 870 325 mencionado anteriormente. En este caso (tras haber extendido los conductores), se inyecta un material fluido entre la lámina de múltiples capas y la oblea, para llenar el espacio disponible y para penetrar entre todos los conductores. Tal como se ha expuesto anteriormente, el material se cura entonces para incrustar los conductores en una capa dieléctrica elástica.

Sin embargo, las soluciones conocidas en la técnica no son completamente satisfactorias. De hecho, estas técnicas son relativamente complejas; por ejemplo, requieren la utilización de capas de sacrificio que afectan de manera adversa a los procedimientos de fabricación correspondientes.

Además, es muy difícil obtener un nivel aceptable de calidad. Por ejemplo, en la estructura dada a conocer en el documento EP-A-0 352 020 las pastillas de chip pueden desprenderse fácilmente del material aislante (antes de su conexión al soporte). Por otro lado, en el documento EP-A-0 870 325 se requiere una precisión muy elevada para obtener el tamaño correcto de los botones bajo los extremos de punta; de hecho, el procedimiento de fabricación correspondiente debe controlarse perfectamente para garantizar que los extremos de punta se retienen por la lámina de múltiples capas (antes de su conexión a la oblea), pero al mismo tiempo se desprenden fácilmente cuando deben extenderse los conductores.

SUMARIO

En general, la presente exposición se basa en la idea de tratar un sustrato en el que se forman los conductores.

En particular, diferentes aspectos de la invención proporcionan una solución tal como se expone en las reivindicaciones independientes. Formas de realización ventajosas de la invención se describen en las reivindicaciones subordinadas.

Más específicamente, un aspecto de la invención propone un procedimiento de fabricación de un elemento de interconexión (para poner en contacto dispositivos electrónicos). El procedimiento comienza con la etapa de formación de una pluralidad de conductores sobre una superficie principal de un primer sustrato; cada conductor presenta un primer extremo y un segundo extremo. El segundo extremo de cada conductor está acoplado con un segundo sustrato. El segundo sustrato y el primer sustrato se separan entonces entre sí, para extender los conductores entre el primer sustrato y el segundo sustrato. El procedimiento también incluye la etapa de tratamiento de la superficie principal antes de formar los conductores para controlar una adhesión de los conductores sobre la superficie principal.

En una forma de realización de la invención, este resultado se consigue por medio de una o más regiones de promoción de la adhesión sobre la superficie principal.

Preferentemente, estas regiones de promoción de la adhesión están realizadas en silicio poroso.

Una manera para mejorar adicionalmente la solución es reducir la porosidad de las regiones de silicio poroso a medida que se aleja de la superficie principal.

Además, se propone un intervalo sugerido de la porosidad.

Este resultado puede conseguirse reduciendo una densidad de corriente de un procedimiento anódico correspondiente en el tiempo.

También se sugiere un intervalo de la densidad de corriente.

En una puesta en práctica específica, las regiones de promoción de la adhesión se forman de manera selectiva en cada zona de contacto entre un conductor correspondiente y la superficie principal.

Una manera de mejorar adicionalmente la solución es reducir la adhesión a medida que se mueve desde el primer extremo hasta el segundo extremo de cada conductor.

También se propone un intervalo sugerido de esta variación.

... [Seguir leyendo]

Reivindicaciones:

1. Procedimiento de fabricación de un elemento de interconexión (160; 160') para poner en contacto dispositivos electrónicos, incluyendo el procedimiento las etapas siguientes:

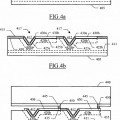

formar una pluralidad de conductores (130) sobre una superficie principal (110) de un primer sustrato (105) de silicio monocristalino tras tratar la superficie principal para controlar una adhesión de los conductores sobre la superficie principal, presentando cada conductor un primer extremo (130a) y un segundo extremo (130b),

acoplar el segundo extremo de cada conductor con un segundo sustrato (140), y

separar entre sí el segundo sustrato y el primer sustrato para extender los conductores (130') entre el primer

sustrato y el segundo sustrato, caracterizado porque la etapa de tratamiento de la superficie principal incluye: formar un conjunto de regiones de silicio poroso (120) que se extienden desde la superficie principal hacia el

interior del primer sustrato.

2. Procedimiento según la reivindicación 1, en el que la etapa de formación de las regiones de silicio poroso

(120) incluye:

modular la porosidad de las regiones de silicio poroso para que dicha porosidad disminuya a medida que se aleja de la superficie principal (110).

3. Procedimiento según la reivindicación 1 ó 2, en el que cada conductor (130) está en contacto con una zona de contacto (117) correspondiente de la superficie principal (110), incluyendo la etapa de formación de las regiones de silicio poroso (120):

formar las regiones de silicio poroso en por lo menos una parte seleccionada de cada zona de contacto.

4. Procedimiento según cualquiera de las reivindicaciones 1 a 3, en el que la etapa de tratamiento de la superficie principal incluye:

reducir la adhesión a medida que se mueve desde el primer extremo (130a) hasta el segundo extremo (130b) de cada conductor (130).

5. Procedimiento según la reivindicación 4 cuando está subordinada a la reivindicación 3, en el que la etapa de reducción de la adhesión incluye:

reducir una concentración de las regiones de silicio poroso (210) a medida que se mueve desde el primer extremo (130a) hasta el segundo extremo (130b) de cada conductor (130).

6. Procedimiento según cualquiera de las reivindicaciones 1 a 5, en el que la etapa de tratamiento de la superficie principal (110) incluye además:

depositar una capa de metal (125) sobre las regiones de silicio poroso (120).

7. Procedimiento según cualquiera de las reivindicaciones 1 a 6, que incluye además las etapas siguientes:

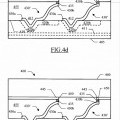

- inyectar un material aislante fluido (155) entre el primer sustrato (105) y el segundo sustrato (140), y

- curar el material aislante para obtener una capa aislante (155) en la que están incrustados los conductores (130').

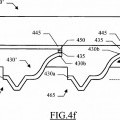

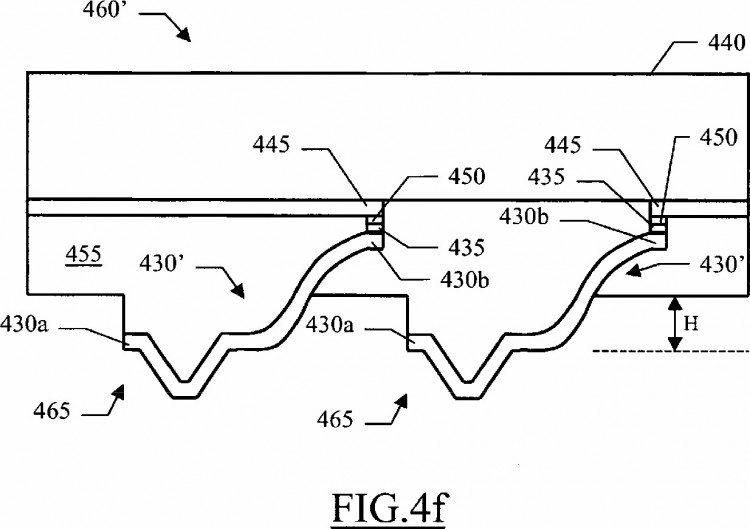

8. Procedimiento según cualquiera de las reivindicaciones 1 a 7, en el que la etapa de formación de los conductores (430') incluye:

crear una pluralidad de ranuras (412) sobre la superficie principal (410), extendiéndose el primer extremo (430a) de cada conductor en una ranura correspondiente.

9. Procedimiento según la reivindicación 8, en el que la etapa de formación de los conductores (430') incluye además:

depositar por lo menos una capa de un material conductor duro (430a) en las ranuras (412), y depositar por lo menos una capa de un material conductor dúctil (430b) para finalizar los conductores.

10. Procedimiento según cualquiera de las reivindicaciones 1 a 9, que incluye además la etapa siguiente: eliminar el primer sustrato (105).

11. Procedimiento según la reivindicación 10, que incluye además la etapa siguiente: eliminar una parte externa de la capa aislante (455) que no está protegida por los conductores (430').

5 12. Procedimiento según la reivindicación 11, en el que la etapa de eliminación de la parte externa de la capa aislante (455) incluye:

eliminar la parte externa para una profundidad igual al 0,1%-70% del espesor de la capa aislante.

13. Procedimiento según cualquiera de las reivindicaciones 1 a 12, que incluye además la etapa siguiente:

eliminar el segundo sustrato (140).

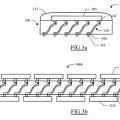

10 14. Procedimiento de fabricación de un montaje (300a) electrónico que incluye un conjunto de dispositivos electrónicos interconectados (3101, 310u), incluyendo el procedimiento la etapa siguiente:

acoplar cada primer terminal (3201) de por lo menos un primer dispositivo electrónico (3101) con el primer extremo (130a) y/o cada segundo terminal (320u) de por lo menos un segundo dispositivo electrónico (310u) con el segundo extremo (130b) de un conductor (130') correspondiente del elemento de interconexión (160') fabricado

15 realizando las etapas según cualquiera de las reivindicaciones 1 a 13.

15. Procedimiento de fabricación de una tarjeta de prueba (460; 460') que incluye una pluralidad de sondas

(465) para poner en contacto terminales correspondientes de dispositivos electrónicos que van a someterse a prueba, incluyendo el procedimiento la etapa siguiente:

acoplar una placa con circuitos (440) con los segundos extremos (430b) de los conductores (430') del elemento 20 de interconexión fabricado realizando las etapas según cualquiera de las reivindicaciones 1 a 13, definiendo los primeros extremos (430a) de los conductores dichas sondas.

Patentes similares o relacionadas:

Sustrato de pastilla embebida con taladro posterior, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un dispositivo, que comprende: un sustrato que tiene un primer lado y un segundo lado opuesto, en el que el sustrato es un sustrato central que […]

Procedimiento para la fabricación de un sustrato de nitruro de aluminio, del 10 de Abril de 2019, de ALSTOM Transport Technologies: Procedimiento para la fabricación de un sustrato de nitruro de aluminio AIN para su utilización como soporte para componentes electrónicos en aplicaciones […]

Método para formar depósitos de soldadura sobre sustratos, del 6 de Enero de 2016, de ATOTECH DEUTSCHLAND GMBH: Un método de formación de un depósito de soldadura sobre un sustrato, que comprende las siguientes etapas:

a. proporcionar un sustrato que incluye […]

Método para formar depósitos de soldadura sobre sustratos, del 6 de Enero de 2016, de ATOTECH DEUTSCHLAND GMBH: Un método de formación de un depósito de soldadura sobre un sustrato, que comprende las siguientes etapas:

a. proporcionar un sustrato que incluye […]

Metalización multinivel sobre un sustrato de cerámica, del 16 de Diciembre de 2015, de CERAMTEC GMBH: Procedimiento para la preparación de una metalización multinivel de cobre sobre un sustrato de cerámica de AlN o Al2O3, mediante el cual se crean sobre un mismo sustrato […]

Disipador térmico para LED de funcionamiento por ciclos, del 18 de Marzo de 2015, de GRAFTECH INTERNATIONAL HOLDINGS INC: Un dispositivo electrónico portátil que comprende: una carcasa; una cámara ubicada en la carcasa; y un ensamblaje de fuente […]

Procedimiento para la producción de una pieza constructiva mediando utilización de una introducción asimétrica de energía a lo largo de la línea de separación o de rotura nominal, del 28 de Agosto de 2013, de CERAMTEC GMBH: Procedimiento para la producción de una pieza constructiva, en el que sobre por lo menos un lado de la superficiede la pieza constructiva se produce […]

Procedimiento para la fabricación de un soporte de conexión, del 27 de Junio de 2012, de SUMITOMO METAL MINING COMPANY LIMITED: Procedimiento para fabricar un soporte de conexión, comprendiendo dicho procedimiento las etapas de: preparar una placa metálica para formar un soporte […]

Procedimiento para la fabricación de un soporte de conexión, del 27 de Junio de 2012, de SUMITOMO METAL MINING COMPANY LIMITED: Procedimiento para fabricar un soporte de conexión, comprendiendo dicho procedimiento las etapas de: preparar una placa metálica para formar un soporte […]

METODO DE UTILIZACION PERMANENTE DE UN MATERIAL SEGUN UN EJE Z., del 1 de Junio de 2004, de W.L. GORE & ASSOCIATES, INC.: LA PRESENTE INVENCION ESTA RELACIONADA CON UN SISTEMA Y UN METODO PARA REALIZAR EL EXAMEN DE FIABILIDAD DE LOS DISCOS DE SEMICONDUCTORES, Y […]